Fターム[5F083NA02]の内容

Fターム[5F083NA02]に分類される特許

1 - 20 / 39

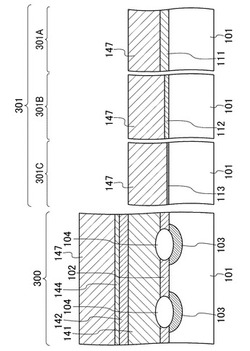

半導体記憶装置の製造方法

【課題】記憶部と論理部とを有する半導体記憶装置において、電気的特性のばらつき及び信頼性の低下を回避できるようにする。

【解決手段】半導体記憶装置の製造方法は、記憶部300及び論理部301を有する基板101の上に、記憶部ゲート絶縁膜102及び第1の導電膜141を形成する工程よりも後に、第1の導電膜141及び記憶部ゲート絶縁膜102における論理部301の上に形成された部分を除去する。論理部ゲート絶縁膜111及び第2の導電膜147を形成する工程よりも後に記憶部300において第1の導電膜141を露出する。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体キャパシタ

【課題】強誘電体膜の表面に現れた窪みを、強誘電体材料で効率的に埋め込むことが可能な強誘電体キャパシタの製造方法を提供する。

【解決手段】基板10の上に第1導電膜11を形成する。第1導電膜11の上に、表面に複数の凹部15が形成された第1強誘電体膜12を形成する。第1強誘電体膜12の表面の凹部15を埋め込むように、第1強誘電体膜12の上に、原子層堆積法により第2強誘電体膜13を形成する。第2強誘電体膜13の上に、第2導電膜17を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

半導体装置とその製造方法

【課題】歩留まりと信頼性を高めるフラッシュメモリセルを備えた半導体装置とその製造方法を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板1に素子分離絶縁膜6を形成する工程と、シリコン基板1の表面にトンネル絶縁膜を形成する工程と、素子分離絶縁膜6とトンネル絶縁膜の上に第1導電膜を形成する工程と、第1導電膜をパターニングして導電パターン13aにする工程と、導電パターン13aの表層部分をスパッタエッチングする工程と、導電パターン13aと素子分離絶縁膜6の上に中間絶縁膜16を形成する工程と、中間絶縁膜16の上に第2導電膜17を形成する工程と、導電パターン13a、中間絶縁膜16、及び第2導電膜17をパターニングすることによりフラッシュメモリセルFLを形成する工程とを有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型半導体記憶装置の電荷蓄積用のトラップ膜及びビット線拡散層を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101に形成され、それぞれ行方向に延伸する複数のビット線拡散層104と、半導体基板101上における互いに隣接する各ビット線拡散層104同士の間に形成され、それぞれが電荷トラップ膜102bを含む複数のONO膜102と、複数のビット線拡散層104の上にそれぞれ形成された複数のビット線絶縁膜105と、半導体基板101の上にそれぞれ複数のONO膜102及び複数のビット線絶縁膜105を覆うように形成され、各ビット線拡散層104と交差して列方向に延伸する複数のワード線106とを有している。ビット線絶縁膜105の膜厚はONO膜102の膜厚よりも小さく、且つビット線絶縁膜105の上面はONO膜102の上面と平行である。

(もっと読む)

不揮発性半導体記憶装置

【課題】ドレイン層とドレイン電極の間の絶縁膜を絶縁破壊することによりデータを記憶させるようにした不揮発性半導体記憶装置において、絶縁膜の破壊電圧を下げる。

【解決手段】ドレイン電極18は三角形状の先端角部18Pを有しており、この先端角部18Pは、ドレイン層11Dの端部とゲート絶縁膜13を介して重畳している。ドレイン電極18に破壊電圧を印加すると、ドレイン電極18の先端角部18Pに電界集中が起こることにより、低い電圧でゲート絶縁膜13の絶縁破壊が生じ、ドレイン電極18とドレイン層11Dが短絡される。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の製造方法等に関し、特にプラズマダメージを受けたゲート絶縁膜のダメージ層を除去し、ゲート絶縁膜の信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、MONOS型メモリトランジスタ領域101及びトランジスタ領域100を同一の半導体基板に有する場合、MONOS型メモリトランジスタ領域の半導体基板上にトンネル酸化膜7を形成し、そのトンネル酸化膜7上及びトランジスタ領域のゲート絶縁膜5上に窒化シリコン膜8を形成し、その上に酸化シリコン膜9を形成する。MONOS型メモリトランジスタ領域にマスク膜10を形成し、マスク膜10を用いて酸化シリコン膜9を除去し、窒化シリコン膜8をドライエッチングにて除去し、トランジスタ領域100のゲート絶縁膜5の上層部分をウェットエッチングにより除去することを特徴とする。

(もっと読む)

半導体装置

【課題】同一の素子領域に、第1のゲート絶縁膜を備える第1のMIS型トランジスタと、第2のゲート絶縁膜を備える第2のMIS型トランジスタとを設ける半導体装置では、素子領域の周囲を取り囲む素子分離膜の傾斜部の膜減りにより、第1のMIS型トランジスタ、および第2のMIS型トランジスタのリーク電流の発生を防止できなかった。

【解決手段】本発明の半導体装置は、素子分離膜の傾斜部の上部に、第1のゲート絶縁膜、第2のゲート絶縁膜、あるいはそれらの絶縁膜とは膜厚が異なる上部絶縁膜を設ける構造とする。このような構造とすることで、素子分離膜の傾斜部が膜減りすることがなく、リーク電流の発生を防止することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 深さの異なる複数のコンタクトホールを有する構造であって、簡易な製造工程の下、基板に対するエッチングダメージを招来せず製造することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板1上の一部領域にフィールド酸化膜2を形成し、その後にフィールド酸化膜2の一部領域をエッチング処理して凹部構造32を形成し、その後に、少なくとも凹部構造32の底面を覆うように、フィールド酸化膜2の上層に下部電極7、酸化膜8、上部電極9を形成し、ソース・ドレイン拡散領域6を形成し、その後に全面に層間絶縁膜10を堆積する。そして、拡散領域6の上面が露出するように拡散領域6の上方領域に係る層間絶縁膜10をエッチングして第1コンタクトホール11aを形成すると共に、上部電極9の上面が露出するように凹部構造32の上方領域に係る層間絶縁膜10をエッチングすることで第2コンタクトホール11cを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷蓄積層とワードラインとが直接接することを抑制し、かつ電荷蓄積層下のバーズビークを抑制する半導体装置製造方法の提供。

【解決手段】半導体基板10上にゲート電極14を形成する工程と、ゲート電極14を覆うように、トンネル絶縁膜16、絶縁体からなる電荷蓄積層18、ダミー絶縁膜を順に形成した積層膜を形成する工程と、積層膜をエッチバックし、ゲート電極14の側面に積層膜からなる側壁32を形成する工程と、ゲート電極14および側壁32をマスクに半導体基板10内に拡散領域26を形成する工程と、側壁32のうちダミー絶縁膜を除去する工程と、側壁32、ゲート電極14および拡散領域26上にトップ絶縁膜30を形成する工程と、トップ絶縁膜30上に導電層34を形成する工程と、導電層34を、ゲート電極14が露出するまで研磨する工程と、ゲート電極14および導電層34上にワードライン36を形成する工程と、を有する。

(もっと読む)

集積回路、メモリ、メモリ製造方法、メモリデバイス製造方法、集積回路およびシステム

【課題】SONOSメモリの記憶密度を増大させる方法を提供する。

【解決手段】finFETSONOSメモリセルを採用し、第1のSONOSメモリセル136a、および、第2のSONOSメモリセル136bを備える。第2のメモリセル136bは、第1のメモリセル136a上に積み重ねる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】フロントゲートとは独立に制御可能なバックゲートを有するFETをメモリセルとして備え、かつコストの低廉な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、絶縁膜20と、絶縁膜の上方に設けられたFin型半導体16、18と、Fin型半導体内を貫通する貫通口40の内壁に設けられた第1のゲート絶縁膜50と、貫通口内を貫通し、第1のゲート絶縁膜によってFin型半導体から絶縁された第1のゲート電極BGと、第1のゲート電極上にあるFin型半導体の側面上および上面上に形成された第2のゲート絶縁膜60と、Fin型半導体の側面上および上面上に第2のゲート絶縁膜を介して設けられた第2のゲート電極FGとを備えている。

(もっと読む)

半導体装置

【課題】高耐圧トランジスタやメモリ素子を混載した微細化構造の半導体装置では、選択酸化法による素子分離膜を採用した際に、素子分離絶縁膜の膜減りによるトランジスタのリーク防止用保護膜を形成すると、半導体表面の凹凸によりゲート寸法制御性が著しく低下するという問題があった。

【解決手段】ゲート電極と、素子分離膜と素子領域との境界領域とが平面的に重なる部分に保護膜を設ける。この保護膜は、製造工程途中で素子分離膜の膜減りを保護することができる。また、素子分離膜を所定の厚さにエッチングすることにより、半導体基板上部を平坦化する。この構成によって、ゲート電極下のリークを防止しつつ、平坦化効果によりゲート寸法制御性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのwellコンタクトをとりやすい半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、絶縁層20上に第1の領域及び第2の領域を有するシリコン層30を形成する工程と、シリコン層30の第1の領域に不純物をドープする工程と、不純物をドープした後シリコン層30の表面に熱酸化膜16を形成する工程と、熱酸化膜16を除去する工程と、第1の領域において第1のフィールド酸化膜41を絶縁層20に接するように形成する工程と、第2の領域において第2のフィールド酸化膜42をシリコン層30を介して絶縁層20上に形成する工程と、第1の領域におけるシリコン層30に、完全空乏型のトランジスタを形成する工程と、第2の領域におけるシリコン層30に、部分空乏型のトランジスタを形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりを向上させることが可能な強誘電体キャパシタを備えた半導体装置の製造方法を提供する。

【解決手段】下地絶縁膜37の上に、第1導電膜41、強誘電体膜42、及び第2導電膜43を順に形成する工程と、第2導電膜43をパターニングして上部電極43aにする工程と、強誘電体膜42の上にレジストパターンを形成する工程と、レジストパターンをマスクにしながら、ハロゲンガスを含むエッチングガスを用いて強誘電体膜42をエッチングすることにより、キャパシタ誘電体膜42aを形成する工程と、レジストパターンを除去する工程と、キャパシタ誘電体膜42aの側面を水洗する工程と、第1導電膜41をパターニングして下部電極にし、該下部電極、キャパシタ誘電体膜42a、及び上部電極43aでキャパシタQを構成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】素子分離膜に対するフローティングゲートの位置ずれを小さくすることができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1を熱酸化することにより、不揮発メモリのトンネル酸化膜11aを形成する工程と、トンネル酸化膜11a上に導電パターン12aを形成する工程と、導電パターン12aの表面上及び側面上に保護膜を形成する工程と、前記保護膜及び導電パターン12aをマスクとして半導体基板1を熱酸化することにより、半導体基板1に素子分離膜2を形成する工程と、前記保護膜を除去する工程と、導電パターン12aを選択的に除去することにより、不揮発メモリのフローティングゲートを形成する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】トラップ膜を有するメモリセルのデータ保持特性の劣化を防止し、信頼性が高いMONOS型不揮発性半導体装置及びその製造方法を提供する。

【解決手段】p型の半導体基板101の上に、電荷を蓄積するONO膜102を有し、ONO膜102の上に多結晶シリコンからなる複数のワードライン103を有し、ワードライン103の表面、ワードライン103の側面、およびONO膜102の表面上に、有機原料を用いた減圧CVD法による、膜厚が約30nm、水素結合量が約5×1022個/cm3、水素含有量が約5×1022atoms/cm3、炭素含有量が約5×1021atoms/cm3のシリコン窒化膜104を有する。これにより、トラップ膜へのチャージングを無くすと共に、ゲート電極間の酸化絶縁膜中の固定電荷を制御することで、メモリセルのデータ保持特性の劣化を防止することができる。

(もっと読む)

不揮発性半導体メモリ装置及びその製造方法

【課題】書き込み特性や読み込み特性に優れ、かつ製造が容易な不揮発性半導体記憶装置及びその製造方法を提供すること。

【解決手段】ほぼ平行に形成された複数のソース/ドレイン領域11、及び、前記複数のソース/ドレイン領域11の間に凹部12が形成された半導体基板1と、前記半導体基板1の前記凹部12に形成される電荷蓄積ゲート3と、前記複数のソース/ドレイン領域11に交差し、かつ、前記蓄積ゲート3上に絶縁層を介して配置される複数の導電ゲート6と、を有する不揮発性半導体記憶装置とする。

(もっと読む)

1 - 20 / 39

[ Back to top ]