Fターム[5F083PR29]の内容

Fターム[5F083PR29]に分類される特許

61 - 80 / 364

シリコン層の形成方法、半導体装置の製造方法

【課題】シリコン層表面の溶解を防止しつつ、エピタキシャル成長により形成された凝集性異物を除去する。清浄な表面を有し、膜厚が均一なシリコン層を形成する。

【解決手段】シリコン基板上にエピタキシャル成長によりシリコン層を形成した後に、シリコン層の表面を酸化する。このシリコン層の表面を洗浄して、エピタキシャル成長時にシリコン層の表面に発生した異物を除去する。

(もっと読む)

可変抵抗メモリ装置及びその製造方法

【課題】可変抵抗メモリ装置及びその製造方法を提供する。

【解決手段】可変抵抗メモリ装置及びその製造方法を提供する。基板上に複数の下部電極を構成し、前記下部電極を露出し、第1方向に延長されるトレンチを含む第1層間絶縁膜を構成し、前記第1層間絶縁膜上に前記第1方向と交差する第2方向に延長される上部電極を構成し、前記トレンチ内に前記上部電極の側壁にアライメントされる側壁を有する可変抵抗パターンを形成する。

(もっと読む)

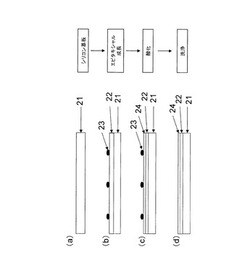

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を簡易に実現する、キャパシタを備える半導体装置を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10上に形成され、且つ、開口部OPを有する絶縁層20と、絶縁層20上に形成された第1キャパシタCAP1及び第2キャパシタCAP2と、を備える。絶縁層20の上面は、開口部OPの内壁面の少なくとも一部を含む第1上面と、第1上面と比較して半導体基板からより離れている第2上面と、を含む。第1キャパシタCAP1は、第1上面上に形成された第1下部電極51と、第1下部電極51上に誘電体膜60を介して形成された上部電極70と、を備える。第2キャパシタCAP2は、第2上面上に形成され第1下部電極51と電気的に分離された第2下部電極52と、第2下部電極52上に誘電体膜60を介して形成された上部電極70と、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】ビット線の上面にハードマスク膜を形成し、ビット線の側壁に窒化膜をエッチバックして形成したサイドウォールを設けるSAC(セルフアラインコンタクト)プロセスを用いることなくビット線と容量コンタクトとの間の短絡を防止する。

【解 決手段】SAC構造を採用していない半導体装置に対して、ビット線6が形成されている場所以外のビットコンタクト層間膜13をエッチング処理により除去した後に、 ダイレクト窒化膜19をビット線6の上面および側面の全面にビット線6を覆うようにして形成する。ビット線6上の上面の窒化膜の膜厚を側面とほぼ同一にで きるため、ビット線6自体の高さが低くなり、微細化を図ることができる。また、エッチバックを必要とせずに、ビット線6の側壁に窒化膜を形成するため、 SAC構造に比べて、ビット線6の側壁に一定の膜厚を有する窒化膜を容易に形成できる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体集積回路装置

【課題】多層配線の下地半導体基板への配線引き出し部のコンタクト抵抗均一化を図った半導体集積回路装置の提供。

【解決手段】半導体集積回路装置は、半導体基板と、前記半導体基板上に複数層積層形成された配線と、前記配線の引き出し領域に前記配線の延長部として形成されて、所定幅のスペースを介して対向するメタル片対により構成されるフックアップ部73と、前記フックアップ部のメタル片対のスペースを貫通するように埋め込まれたコンタクト導体72とを有し、前記配線の少なくとも2層の間で前記フックアップ部のメタル片対のスペース幅を異ならせた。

(もっと読む)

半導体装置

【課題】メモリセルの端部にダミーのパッドコンタクトを形成した場合、ゲート配線の電位がビット配線の影響を受けない構造の半導体装置を提供する。

【解決手段】半導体基板10と、半導体基板10の主表面に形成された活性領域と、活性領域を取り囲む分離絶縁膜19と、活性領域上のゲート配線2と、ゲート配線2を被覆し、窒素を含むゲート配線被覆3,4と、ゲート配線2に立体的に交差してゲート配線2よりも上層に形成されるビット配線8と、半導体基板10の主表面とゲート配線被覆3,4で被覆されたゲート配線2とを覆う層間酸化膜5と、層間酸化膜5を貫通して、平面的に見てゲート配線2の間で、ゲート配線被覆3,4と接触するように形成されたパッドコンタクト6,21bとを備えたメモリセルを含む半導体装置である。メモリセルの端部の少なくとも一部のパッドコンタクト6,21bが、活性領域と導通しないように分離絶縁膜19上に形成されている。

(もっと読む)

スプリットゲート型不揮発性半導体記憶装置の製造方法、及びスプリットゲート型不揮発性半導体記憶装置

【課題】スプリットゲート型不揮発性記憶装置に製造における工程数を削減する。

【解決手段】基板(2)と、ゲート絶縁膜(7)を介して基板(2)の上に形成されたフローティングゲート(5)と、トンネル絶縁膜(8)を介してフローティングゲート(5)の隣に形成されたコントロールゲート(6)と、コントロールゲート(6)側の基板(2)に形成された第1ソース/ドレイン拡散層(4)と、フローティングゲート(5)側の基板(2)に形成された第2ソース/ドレイン拡散層(3)と、第1ソース/ドレイン拡散層(4)と第2ソース/ドレイン拡散層(3)との間の基板に設けられるチャネル領域と、第2ソース/ドレイン拡散層(3)に接触しているシリサイド(21)とを具備するスプリットゲート型不揮発性半導体記憶装置を構成する。

(もっと読む)

フローティングゲートメモリセルを製造するための方法およびフローティングゲートメモリセル

【課題】ソースがチャネル領域の中に横方向に散在および拡散するのを低減させ、これはフローティングゲートメモリセルにおけるドレイン誘導障壁低下(DIBL)の低減をもたらす。

【解決手段】基板404のソース領域422に窪み464を形成する。窪み464はスタックゲート構造408に隣接して位置し、窪み464は傾斜のついた側壁466と底部468と深さ476とを有し、スタックゲート構造408は基板404におけるチャネル領域426の上に位置する。さらに、窪み464の傾斜のついた側壁466に隣接したフローティングゲートメモリセル402のソース488を形成し、スタックゲート構造408に隣接しかつ窪み464の傾斜のついた側壁466に隣接したスペーサ490を形成する。スペーサ490は窪み464の底部468に延在し、ソース488が前記チャネル領域426の中に横方向に散在および拡散するのを低減させる。

(もっと読む)

半導体装置の製造方法

【課題】電荷蓄積膜を用いる不揮発性記憶用MOS型トランジスタと、これを選択するMOS型トランジスタが隣接するスプリットゲート構造を有する不揮発性メモリセルにおいて、電荷保持特性を向上し、ゲート電極を低抵抗化する。

【解決手段】電荷蓄積膜のコーナー部20の薄膜化を抑制して電荷保持特性を向上するために、選択ゲート電極15の側壁にテーパーを設ける。また、自己整合で形成するゲート電極を低抵抗化するシリサイドを安定に行うため、選択ゲート電極15の側壁をリセスさせる。もしくは、自己整合ゲート電極上部18と選択ゲート電極上部65の間に段差を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】優れた特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100に設けられた素子形成領域10bと、素子形成領域上に形成されたトンネル絶縁膜11と、トンネル絶縁膜上に形成された電荷蓄積絶縁膜12と、電荷蓄積絶縁膜上に形成されたブロック絶縁膜14と、ブロック絶縁膜上に形成された制御ゲート電極15と、を備えたメモリセルトランジスタと、メモリセルトランジスタに隣接して形成された素子分離領域13と、を具備し、メモリセルトランジスタのチャネル幅方向に平行な断面において、電荷蓄積絶縁膜の端部の膜厚は、電荷蓄積絶縁膜の中央部の膜厚よりも薄い。

(もっと読む)

半導体記憶装置

【課題】静電容量の大きなキャパシタを備え、低コストで製造が可能な、高集積化された半導体記憶装置を提供する。

【解決手段】半導体基板上にY方向に延在しY方向と垂直なX方向に互いに平行に配列されたワード線と、Y方向に互いに平行に配列され二つのワード線と交差する帯状の活性領域と、各活性領域上のその長手方向の両端部にそれぞれ接続する容量コンタクトプラグと、容量コンタクトプラグ上の第1下部電極と第1下部電極上の第2下部電極を含むスタック下部電極と、容量絶縁膜と、上部電極とを有し、第2下部電極の中心位置が第1下部電極の中心位置から所定の方向へシフトしている、半導体記憶装置。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

自己整列式縦ヒータと低抵抗率界面を備えた相変化メモリセル

【課題】完全に自己整列式の縦ヒータ素子を備えた相変化メモリセルを製造するためのプロセスを提供する。

【解決手段】自己整列式縦ヒータ素子と選択デバイスの接点領域の間に低抵抗率界面材料が提供されている。相変化カルコゲナイド材料を、縦ヒータ素子の上に直接堆積させている。或る実施形態では、縦ヒータ素子は、ワード線方向に沿った曲線状の縦壁と横基部を有するL字形である。或る実施形態では、低抵抗率界面材料は、PVD技法を使用して、負の輪郭を有するトレンチの中へ堆積させてゆく。低抵抗率界面材料の上側面は、先細の鳥のくちばし状伸張部を有していてもよい。

(もっと読む)

半導体集積回路装置

【課題】不揮発性メモリにおいて、データの書き換え回数増加時における動作信頼性を向上できる技術を提供する。

【解決手段】基板1上に、ボトム酸化膜7Aと電荷蓄積層8Aとトップ酸化膜9Aからなる積層絶縁膜を介して、ゲート電極9Aが形成され、ボトム酸化膜7Aの膜厚はトップ酸化膜9Aの膜厚よりも厚く形成されている。このように構成されているメモリセルにおいて、書き込みおよび消去となる電荷蓄積層8Aへの電荷のやり取りは、ゲート電極10Aと電荷蓄積層8Aとの間で行う。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】写真製版プロセスのマージンを大幅に拡大でき、かつマイクロローディング効果を低減することによって「開口不良」を抑制できるとともに「ショート」のプロセス裕度を確保しやすくし、かつコンタクト抵抗を低減できる半導体装置の製造方法を提供する。

【解決手段】活性領域に対して傾斜して延びるようにゲート電極層50と窒素を含む絶縁膜2とが積層される。シリコン酸化膜5が形成される。活性領域の幅より大きくかつ互いに隣り合う活性領域のピッチより小さい帯状の開口パターンが絶縁膜2に形成され、開口パターンから1対の不純物拡散領域の各々が露出させられる。開口パターンが導電層23で埋め込まれる。導電層23から1対の不純物拡散領域の各々に電気的に接続されたプラグ導電層23a、23bが形成されるとともに、プラグ導電層23a、23bの各上面と絶縁膜2の上面とが同一平面とされる。

(もっと読む)

半導体装置およびその製造方法

【課題】コントロールゲート電極とメモリゲート電極間に発生する電界強度を緩和してリーク電流を低減できる、コントロールゲート電極とメモリゲート電極が近接するスプリットゲート型不揮発性メモリを提供する。

【解決手段】半導体基板1S上にゲート絶縁膜GOXが形成され、このゲート絶縁膜GOX上にコントロールゲート電極CGが形成されている。そして、コントロールゲート電極CGの右側の側壁には、積層絶縁膜を介してメモリゲート電極MGが形成されている。このとき、コントロールゲート電極CGの上端部にバーズビークBVが形成されている。この結果、コントロールゲート電極CGの上端部と、メモリゲート電極MGの上端部が、バーズビークBV分だけ離れるので電界強度の緩和を図ることができ、コントロールゲート電極CGとメモリゲート電極MG間を流れるリーク電流を低減できる。

(もっと読む)

61 - 80 / 364

[ Back to top ]