Fターム[5F083PR29]の内容

Fターム[5F083PR29]に分類される特許

101 - 120 / 364

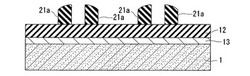

半導体装置の製造方法

【課題】トレンチゲート形成において、ペアスペースパターンの位置ずれの生じないパターン形成方法を提供する。

【解決手段】被加工層1上に、第3〜第1マスク層13,12,11を順次積層する。第1マスク層上に第4マスク層を形成し、第4マスク層をマスクにして第1マスク層をラインパターン形状に成形する。第1マスク層のライン幅方向両側に、サイドウオール層21aを形成してから第1マスク層を除去する。一対のサイドウオール層をマスクにして第2マスク層を一対のラインパターン形状に成形する。第3マスク層上に第5マスク層を形成し、第5マスク層をマスクにして一対の開口部を第3マスク層に設ける。第3マスク層をマスクにして被加工層に一対の溝部を設ける。

(もっと読む)

不揮発性半導体記憶装置

【課題】高電界領域及び低電界領域のリーク電流特性の双方を改善する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101内に互いに離間して設けられたソース領域110S及びドレイン領域110Dと、ソース領域110S及びドレイン領域110D間のチャネル領域上に設けられた第1の絶縁膜102と、第1の絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられ、かつ第1のランタンアルミシリケート膜と、第1のシリコン酸化膜若しくは第1のシリコン酸窒化膜とが積層された積層構造を含む第2の絶縁膜104と、第2の絶縁膜104上に設けられた制御ゲート電極105とを含む。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】カップリング比を減少させずにゲート電極と不純物拡散領域との位置が整合して形成される不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板に形成される複数の不純物拡散領域と、前記半導体基板上に形成される絶縁膜と、隣り合う前記不純物拡散領域を繋ぐように前記半導体基板上に前記絶縁膜を介して形成されるフローティングゲート電極と、前記フローティングゲートの上面及び側面に形成されるゲート間絶縁膜と、前記ゲート間絶縁膜を介して前記フローティングゲート電極の上面及び両側面と接するように形成されるコントロールゲート電極とを備える。

(もっと読む)

不揮発性半導体記憶装置のメモリセル

【課題】微細化を行っても、書き込み/消去特性、繰り返し特性、およびリテンション特性に優れたMONOS型メモリセルを提供する。

【解決手段】不揮発性半導体記憶装置のメモリセルは、MONOS型の構造をしており、電荷蓄積層が複数の絶縁物層から構成される。それらの絶縁膜の隣接する層間の伝導帯端エネルギーと価電子帯端エネルギーの関係は、トンネル絶縁膜からブロック絶縁膜に向かって、次第に大きくなるか、または、次第に小さくなるかのいずれかである。さらに、ブロック絶縁膜の比誘電率をεrとすれば、電荷蓄積層とブロック絶縁膜の間のエネルギー障壁は、電子に対して4.5εr-2/3(eV)以上、3.8eV以下、正孔に対して4.0εr-2/3(eV)以上、3.8eV以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造のMONOS型不揮発性メモリセルを有する半導体装置において、信頼度を低減することなく高集積化を実現する。

【解決手段】メモリ用nMISのメモリゲート電極MGの高さを選択用nMISの選択ゲート電極CGの高さよりも20〜100nm高く形成することにより、メモリゲート電極MGの片側面(ソース領域Srm側の側面)に形成されるサイドウォールSW1の幅を、所望するメモリセルMC1のディスターブ特性を得るために必要とする大きさとする。また、周辺用第2nMIS(Q2)のゲート電極G2の高さを選択用nMISの選択ゲート電極CGの高さ以下とすることにより、ゲート電極G2の側面に形成されるサイドウォールSW3の幅を小さくして、シェアードコンタクトホールC2の内部がサイドウォールSW3により埋め込まれるのを防ぐ。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル間の短絡を防ぐことで、リーク電流を低減する、抵抗変化型不揮発性メモリセルを備えた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1の絶縁層11上に設けられ、かつ第1の方向に延在する第1の配線層13と、第1の配線層13上に柱状に設けられ、かつ直列に接続された非オーミック素子18と可変抵抗素子14とを含む不揮発性メモリセルMCと、メモリセルMC上に設けられ、かつ面内方向に単一の層で構成されたバリア層21と、バリア層21上に設けられ、かつ面内方向に単一の層で構成された導電層30と、第1の絶縁層11上に設けられ、かつメモリセルMC、バリア層21及び導電層30の側面を覆う第2の絶縁層20と、導電層30上に設けられ、かつ第2の方向に延在する第2の配線層22とを含む。

(もっと読む)

強誘電体ゲート有機電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート有機電界効果トランジスタの製造方法

【課題】強誘電体膜及びゲート電極間のリーク電流値を低減させると共に耐絶縁性を向上させる。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3HfSiON膜4及びC60膜6が、この順で積層されたゲート構造を有しており、強誘電体膜3の、HfSiON膜4と接する側の表面におけるRa値とRms値との和の第1絶対値が、HfSiON膜4の膜厚以下であり、かつ、HfSiON膜4の、C60膜6と接している側の表面におけるRa値とRms値との和の第2絶対値が3.0nm以下である。

(もっと読む)

半導体記憶装置の製造方法

【課題】ゲート電極の形状が可能な限り揃ったものとすることができる半導体記憶装置の製造方法を提供すること。

【解決手段】ゲート絶縁膜10上に、ゲート電極材料からなるゲート電極材料膜を形成するゲート電極材料膜形成工程と、前記ゲート電極材料膜をエッチングにより選択的に除去して、行方向に延伸するゲート電極18,38を複数本、隣接するゲート電極18,38間のすき間間隔が等しくなるように形成するゲート電極形成工程と、前記複数本のゲート電極18,38の内、コンタクトプラグの形成予定領域に形成したゲート電極38をダミーのゲート電極38として、エッチングにより選択的に除去するダミーゲート電極除去工程とを設けた。

(もっと読む)

半導体装置の製造方法

【課題】

DRAMの容量を安定化し、メモリセル部と周辺回路部の高低差を小さくして平坦化を容易にする。

【解決手段】

メモリセルトランジスタ上の第1の絶縁膜に第1のコンタクトプラグを埋め込み、エッチング特性の異なる第2、第3の絶縁膜を形成し、第3、第2の絶縁層を貫くコンタクト窓を形成し、シリンダ型蓄積電極を形成し、第2の絶縁膜をエッチングストッパとして第3の絶縁膜を除去し、キャパシタ絶縁膜、導電膜を形成し、パターニングして対向電極を形成し、対向電極に合わせて第2の絶縁膜も除去してメモリセルを形成し、周縁領域において第1の絶縁膜の上に導電膜、絶縁膜を形成し、第2のコンタクトプラグを埋め込む。第2の絶縁膜端部は、第2のコンタクトプラグに接しない。

(もっと読む)

半導体装置とその製造方法

【課題】基板からの高さが異なる導電層に、コンタクト窓を形成するDRAM等の半導体装置を提供する。

【解決手段】半導体基板16上に、第1導電パターン19、20と第1絶縁膜26、エッチング特性の異なる第2絶縁膜30、第3絶縁膜52、蓄積電極39、キャパシタ絶縁膜、対向電極40、エッチング特性の異なる第4絶縁膜41を形成し、第1導電パターン19,20上方に第1開口、対向電極40上方に第2開口を有するマスクを形成し、第1絶縁膜26をストッパとして、第1開口下方の第4絶縁膜41、第2絶縁膜30をエッチングし、第3絶縁膜52をストッパとして、第2開口下方の第4絶縁膜41、対向電極40をエッチングし、第1開口下方の第1絶縁膜26をエッチングして第1コンタクトホール44を形成し、第2絶縁膜30をストッパとして、第2開口下方の第3絶縁膜52をエッチングして第2コンタクトホール42を形成し、導電材を埋め込む。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積を縮小化した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メタル27、第1メタル27と交差する第2メタル36、第1メタル27及び第2メタル36の交差部でそれらの間に接続されたメモリセルMCを有する単位セルアレイMATを備える。周辺領域Ar2において、所定位置からカラム方向の(4m−3)番目(mは正の整数)及び(4m−2)番目に位置する第1メタル27は、そのロウ方向の一端側にコンタクト接続部27bを有する。周辺領域において、所定位置からカラム方向の(4m−1)番目及び4m番目に位置する第1メタル27は、そのロウ方向の他端側にコンタクト接続部27aを有する。

(もっと読む)

半導体装置

【課題】リーク電流を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、素子領域20と、素子領域20上に形成されたトンネル絶縁膜30と、トンネル絶縁膜30上に形成された電荷蓄積絶縁膜40と、電荷蓄積絶縁膜40上に形成されたブロック絶縁膜60と、ブロック絶縁膜60上に形成された制御ゲート電極70と、を備えた第1及び第2のメモリセルと、第1及び第2のメモリセルの素子領域20、トンネル絶縁膜30及び電荷蓄積絶縁膜40の間に形成された素子分離領域20と、を具備し、ブロック絶縁膜60は、金属元素及び酸素を主成分として含有する第1の絶縁膜61と、シリコン及び酸素を主成分として含有する第2の絶縁膜62とで形成され、ブロック絶縁膜60の少なくとも一部は、素子分離領域50上に形成されていることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】隣り合う複数のゲート電極間にセルフアラインコンタクト構造を信頼性良く形成できるようにする。

【解決手段】シリコン基板2上にゲート絶縁膜5を介して多結晶シリコン層6、ONO膜7、多結晶シリコン層8、シリサイド層9、ゲート加工用マスクを順に形成し、異方性エッチング処理することで分断加工して複数のゲート電極MG1、MG2を形成する。その後、ゲート加工用マスクを除去処理してシリサイド層9の上面を露出し、露出したシリサイド層9の上面上にSAC用マスクとしてシリコン窒化膜10を形成し、シリコン窒化膜10をマスクとして複数のゲート電極MG1、MG2間にシリコン基板2の上面に達するコンタクトホールDH、SHを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低電圧トランジスタのジャンクションリークを減らす。

【解決手段】高電圧トランジスタおよび低電圧トランジスタを含む半導体装置は、高電圧トランジスタの第1素子領域11と低電圧トランジスタの第2素子領域14との間に形成された素子分離絶縁膜と、第1素子領域11の半導体基板1上に形成された第1ゲート絶縁膜17と、第1ゲート絶縁膜17上に形成された第1ゲート電極12と、第2素子領域14の半導体基板1上に形成された第2ゲート絶縁膜18と、第2ゲート絶縁膜17上に形成された第2ゲート電極15と、を備えている。素子分離絶縁膜は、第1素子領域11の周囲に隣接する第1素子分離領域13と、第2素子領域14の周囲に隣接し、第1素子分離領域13の底部より低い底部を有する第2素子分離領域16と、を含む。第1ゲート絶縁膜17は、第2ゲート絶縁膜18より厚くなるように形成される。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離領域の深さを抑制しながら耐圧の低下を抑制できるようにする。

【解決手段】ドレイン領域2aはゲート電極MG1の近傍に位置して形成されており、ソース領域2bはシリコン酸化膜11およびシリコン窒化膜12の膜厚分だけゲート電極MG1の側端(端部)から平面方向に離間してシリコン基板2の表層に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ビットコンタクトと容量コンタクトとの接触を防止する。

【解決手段】拡散層領域121,122を有するトランジスタ111と、層間絶縁膜151に埋め込まれ、それぞれ拡散層領域121,122に接続されたセルコンタクト131,141と、層間絶縁膜152に埋め込まれ、セルコンタクト131に接続されたビットコンタクト132と、層間絶縁膜153に埋め込まれ、ビットコンタクトと接続されたビット線130と、層間絶縁膜152,153に埋め込まれ、セルコンタクト141と接続された容量コンタクト142とを備える。ビット線130の側面130aは、ビット線130の延在方向に沿ったビットコンタクト132の側面132aと一致している。これにより、ビットコンタクトと容量コンタクトが直接短絡することがなくなるため、容量コンタクトの形成マージンが拡大する。

(もっと読む)

記憶装置及び半導体装置

【課題】抵抗変化素子を有する記憶装置であって、抵抗変化素子の抵抗状態のばらつき抑制が図られた記憶装置を提供する。

【解決手段】記憶装置は、下部電極と、下部電極を覆って形成され、底に下部電極の露出する開口を有する絶縁膜と、開口の側壁上に形成され、底に下部電極の露出する凹部を画定するサイドウォール絶縁膜と、凹部内に形成された上部電極と、凹部の底で、下部電極と上部電極との間に形成された抵抗変化膜とを有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コントロールゲート電極にプロセス整合性の高いメタル材料を用いても、適切な閾値電圧を有するメモリセルを備えた不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板に離間して設けられたソース領域およびドレイン領域4a、4bと、ソース領域とドレイン領域との間のチャネル領域6となる半導体基板上に設けられた第1絶縁膜12と、第1絶縁膜上に設けられた電荷蓄積膜13と、電荷蓄積膜上に設けられた第2絶縁膜14と、第2絶縁膜上に設けられ、Ni、Co、Pd、Ptのグループから選択されたいずれか一つの元素と、Siと、Oとを含むコントロールゲート電極18と、を備えている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】高いカップリング比を有するセルトランジスタを備えた不揮発性半導体記憶装置およびその製造方を提供する。

【解決手段】半導体基板11の第1領域11aにおいて、第1ゲート電極15の上面15bおよび第1絶縁分離層12の側面12aを露出させる工程と、第1絶縁分離層12の側面12aに第1側壁膜35aを形成する工程と、第1側壁膜35aをマスクとして、第1ゲート電極15の上部をエッチングし、第1ゲート電極15の上部に第1凹部15aを形成する工程と、第1ゲート電極15の上部を露出させる工程と、第1ゲート電極15の上部を含む第1絶縁分離層12上にコンフォーマルに第2ゲート絶縁膜16を形成する工程と、第1凹部15aを埋め込むように、第2ゲート絶縁膜16上に第2ゲート電極材料膜を形成する工程と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】リテンションタイム(情報保持時間)を大きくすることで、リフレッシュサイクルを長くでき、消費電力を大幅に低減できるキャパシタレスRAMを提供する。

【解決手段】キャパシタレスRAMを含む半導体装置は、フローテイングボデイ構造を有する電界効果トランジスタ(FET)を含み、FETは所定のバンドギャップを有する第1の半導体(p−SiGe)からなる領域に設けられたチャネルボデイ部3と、第1の半導体よりもバンドギャップの大きい第2の半導体(n−Si)からなる領域10−2を有する。この特徴により電荷(ホール)をボデイ領域3に蓄える際、ボデイ領域3にあるホールから見たソース・ドレイン領域10のエネルギー障壁が大きいので、蓄えられるホール(正電荷)数を多くすることができる。

(もっと読む)

101 - 120 / 364

[ Back to top ]