Fターム[5F089AA06]の内容

フォトカプラ、インタラプタ (4,081) | フォトカプラの応用 (230) | 半導体集積回路の光配線(インターコネクション) (24)

Fターム[5F089AA06]に分類される特許

1 - 20 / 24

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】 サファイア単結晶基板10と、サファイア単結晶基板10の一方主面10Aに第1素子機能部22を備え、他方主面10Bに第2素子機能部32を備え、第1素子機能部22が光を発光し、第2素子機能部32がサファイア単結晶基板10を透過した光を受光することで、高い周波数の信号を精度良く伝送する。

(もっと読む)

光半導体の駆動回路

【課題】フォトカプラ等の光半導体のCTRが低下していない場合には、入力電流を必要以上に流さないようにする。

【解決手段】フォトカプラ等をスイッチング動作させてパルス信号の伝達をしている光半導体の駆動回路において、入力抵抗を可変させるためのスイッチと、出力電流を監視して該スイッチをオン、オフさせる出力電流判定部を備え、出力電流の値によりCTRの低下を判定し、適切な入力抵抗値とすることで必要な入力電流のみを流すようにする。フォトカプラのCTRが低下していない場合でも必要以上に入力電流を流さないようにできる。

(もっと読む)

半導体パッケージ、半導体装置、及びその検査方法

【課題】より細かい故障箇所の特定が可能な半導体パッケージ、半導体装置、及びその検査方法を提供すること。

【解決手段】本発明にかかる半導体パッケージ1は、LSIチップ5と発光素子チップ6Aとがパッケージ基板4に実装されたものであって、発光素子チップ6Aから出力される出力光信号が、パッケージ基板4に形成された出力光信号分岐構造によって分岐され、分岐された出力光信号のうち少なくともふたつが半導体パッケージ1の外部に出射される構造を有する。また、LSIチップ5と受光素子チップ6Bとがパッケージ基板4に実装されたものであって、半導体パッケージ1に入力される入力光信号が、パッケージ基板4に形成された入力光信号分岐構造によって分岐され、分岐された入力光信号のうちの少なくともひとつが受光素子チップ6Bに入力され、別の少なくともひとつが半導体パッケージ1の外部に出射される構造を有する。

(もっと読む)

高速光配線素子

【課題】多重チャネルを含む高速光配線素子を提供する。

【解決手段】高速光配線素子が提供される。高速光配線素子は、SOI基板上の第1半導体チップと、SOI基板上の前記第1半導体チップから電気信号を受信して光信号を出力する光放出器と、SOI基板上の前記光信号を感知して電気信号に変換する光検出器と、SOI基板上の前記光検出器によって変換された電気信号を受信する第2半導体チップとを含む。

(もっと読む)

集積回路モジュール

【課題】三次元形状の立体配線基体に実装される複数の電子ディバイス又は光ディバイスの配置設計の自由度を拡大する。

【解決手段】中空部11を有する三次元形状で形成される立体配線基体1と、この立体配線基体1の中空部11の内側面12に配設され、光信号で情報の送信及び/又は受信を行う複数の電子ディバイス21、〜、27とを備え、前記一の電子ディバイス21が他の複数の電子ディバイス22、〜、27との間で光信号による情報の送信及び/又は受信を行う構成としているので、各電子ディバイス及び光ディバイスとの配設位置に制限されることなく同時に情報の送信及び受信ができることとなり、三次元形状の立体配線基体に実装される複数の電子ディバイス又は光ディバイスの配置設計の自由度を拡大すると共に、設計時間及び労力を極力少なく設計できるという効果を有する。

(もっと読む)

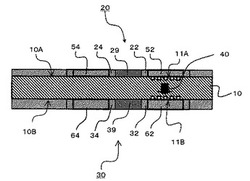

光結合装置

【課題】信頼性を確保しつつ小型化が可能な光結合装置を提供する。

【解決手段】開口部を有し絶縁材料からなる支持体と、前記支持体の第1の面に設けられた第1の配線層と、前記支持体の前記第1の面と反対側の第2の面に設けられた第2の配線層と、前記第1の面上に設けられ、前記第1の配線層に接続され、少なくとも一部が前記開口部に対向する発光素子と、前記第2の面上に設けられ、前記第2の配線層に接続され、前記開口部を介して前記発光素子と対向する受光素子と、前記発光素子と、前記受光素子と、を覆うように設けられた遮光性樹脂と、を備えたことを特徴とする光結合装置が提供される。

(もっと読む)

光クロック分配装置

【課題】LSIの微細化や高速化に伴い、従来の(電気配線)電気信号によるクロックでは配線遅延によるクロックスキューが問題になるが、それを回避するための光クロック信号を分配する光学系が複雑になっており、実装コストがかかる。

【解決手段】コア及びクラッドから構成される光ファイバ形状の導波路を一定の間隔で束ね、板状に成形したファイバオプティックプレートからなる光分配機能素子と、受光素子を搭載したLSIチップとを積層させ、開口角よりも大きい角度(θi>θa)で前記光分配機能素子へ入射する外部光源を配置することで、FOPの拡散モード伝搬を用いた光分配素子とLSIとを積層する構成により、LSIのチップ構造等は変更せず、クロックスキューの低減を図るための光クロックの分配装置が単純な実装方法により達成するという効果を有する。

(もっと読む)

光学部品実装用サブマウント、及び光送受信モジュール

【課題】簡易且つ確実に精度良く光学部品の実装が可能な光学部品実装用サブマウント、及びこれを用いた光送受信モジュールを提供すること。

【解決手段】 例えば、サブマウント22は、略直方体状の基板から構成されている。このサブマウント22には、高分子光導波路フィルム10を取付けるための凹部26(光学部品実装用凹部)と、受光素子及び発光素子を嵌め込んでそれぞれ保持(実装)するための凹部28a,28b(光学部品実装用凹部)とが形成されている。このような構成のサブマウント22において、光学部品実装用凹部としての凹部26,28a,28bは、4つ或いは3つの側壁がテーパー状となっており、開口が底面よりも大きくなるように設ける。

(もっと読む)

光結合装置の製造方法

【課題】発光素子3A(3B)および受光素子4A(4B)の対からなるフォトカプラを多数有する光結合装置の製造方法において、隣り合うチャンネル間のクロストークを十分に抑制した構造を簡易かつ低コストで得られるようにする。

【解決手段】単一のシリコン基板2上に多数のフォトカプラを設けた多チャンネル・モノリシックタイプのチップ1を絶縁基板20上に搭載し、フォトカプラを構成する発光素子3A(3B)と受光素子4A(4B)との間にダイシングにより第1切り込み溝25を形成し、この第1切り込み溝25に透光性絶縁樹脂30を充填した後、隣り合うフォトカプラの間にダイシングにより第2切り込み溝26を形成し、各発光素子3A(3B)および各受光素子4A(4B)と外部端子22とをボンディングワイヤ31にて電気的に接続して、絶縁基板20上の全体を遮光性樹脂32でモールドする。

(もっと読む)

光導波路ユニット

【課題】光信号の伝送が効率よく行われ、低コストで製造可能な光導波路ユニットを提供することにある。

【解決手段】本発明の光導波路ユニット1は、コア層12と、クラッド層11、13とを備えた光導波路基板10に、信号光の送信側および受信側の光学素子50が設置される。光導波路基板10は、前記光学素子50の設置側からスタンプ部材20を光導波路基板10に押圧させることにより、コア層12に前記信号光を反射させるミラー部31が形成され、クラッド層11には光学素子50の位置決め用の基板ガイド部32が形成される。

(もっと読む)

光電変換装置及びその製造方法、並びに光導波モジュール及び光情報処理装置

【課題】 光電変換素子と、レンズ部とのアライメント精度を向上することができ、小型化及び薄型化が可能な光電変換装置及びその製造方法、並びに光導波モジュール及び光情報処理装置を提供すること。

【解決手段】 光出射面又は光入斜面5が露出するように素子基体1に設けられた光電変換素子(例えば発光素子又は受光素子)2と、光電変換素子2に対応したレンズ部6が設けられた単一のレンズ基体7とからなり、光出射面又は光入斜面5の側において素子基体1にレンズ基体7が直接接合されている光電変換装置10、及びその製造方法。本発明の光電変換装置と、光導波部(例えば光導波路)とからなる、光導波モジュール。本発明の光電変換装置と、光導波部と、前記光電変換素子を駆動する駆動素子とからなる、光情報処理装置。

(もっと読む)

半導体装置、基板製造方法および電子機器

【課題】上面入射による基板内の光信号伝送を容易に行い得るようにする。

【解決手段】SOI基板101のシリコン酸化膜101bは、第1の深さ部分101b1、この第1の深さ部分より深い第2の深さ部分101b2およびこれら第1、第2の深さ部分を接続する傾斜部分101b3からなっている。傾斜部分101b3を光信号の通過路を構成する反射ミラーとして用いる。面発光レーザチップ105からの光信号はSiO2貫通孔104aを介して傾斜部分101b3に導かれる。そして、この光信号は、傾斜部分101b3の内表面で反射され、その後、シリコン酸化膜101bの第2の深さ部分101b2を光導波路として導波されていく。この光信号は、再びシリコン酸化膜101bの傾斜部分101b3の内表面で反射され、SiO2貫通孔104bを介してPDチップ108の光信号入力部108bに入力される。

(もっと読む)

光導波路アレイ、それを用いた光電複合装置および電子機器

【課題】光導波路アレイを構成するリッジ型の光導波路の延伸方向と直交する方向の強度を高める。

【解決手段】光導波路アレイ103は、複数本のリッジ型の光導波路135,136が、その延伸方向(X方向)と直交する方向(Y方向)に、所定間隔をもって並べて配置されている。X方向に間隔d1をもって、各光導波路135,136と隣接する他の光導波路を接続する補強梁部138を設ける。補強梁部138は、Y方向に延びるものであり、かつ光導波路135,136と同一材質のものとされている。補強梁部138aを設けることで、光導波路135,136のY方向の強度が高まり、物理的外乱に強いものとなる。補強梁部138を光導波路135,136と同一材質のものとすることで、当該補強梁部138を光導波路135,136と同一のプロセスで同時に形成でき、製造が容易となる。

(もっと読む)

光素子、その実装方法、並びに光電複合装置および電子機器

【課題】光素子の実装占有面積を小さくして実装の高密度化を図る。

【解決手段】インターポーザ105aの裏面には発光素子アレイ106が実装されている。インターポーザ105aの裏面の電極パッド153aと発光素子アレイ106の上面の電極161aとの間にはんだ155aが介在されている。発光素子アレイ106を構成する各発光素子161は、それぞれ、表面(上面)側に、発光部161bと同軸上に電極161aが配置されており、発光部161bから裏面(下面)側に光信号としてのレーザ光を出射する。光素子アレイ106をインターポーザ105aに実装する際に、例えばインターポーザ105aの電極パッド153aにプリコーティングされたはんだ155aのみを利用し、フラットニング処理などで、発光部161bに余分な負荷を与えないようにする。

(もっと読む)

半導体装置およびそれを用いた電子機器

【課題】クロックスキューを容易に低減し、また消費電力の増大を招くことなくクロック信号の周波数を上げて半導体装置の動作速度の高速化を図る。

【解決手段】SOIウェーハ101上に複数の機能ブロックが形成されている。複数の機能ブロックは夫々フォトダイオード(PD)102を有している。複数の機能ブロックの全てが導光板107で覆われる。光信号発生部108からはクロック信号に対応した光信号が発生され、この光信号が導光板107に入射される。この光信号は導光板107を介して、複数の機能ブロックのPD102に入射される。複数の機能ブロックでは、夫々、PD102により光信号が電気信号に変換され、クロック信号を取得できる。PD102に対応して波長分波フィルタ105を配設することで、各機能ブロックのPD102には、所定の波長の光信号のみを選択的に入射できる。

(もっと読む)

半導体集積回路、半導体集積回路配置装置及び方法

【課題】 直接位置決めしたい光素子を配置予定位置に位置させて、半導体体回路の位置決め精度を向上させる。

【解決手段】 ICチップ42を予め定められた配置予定位置に位置させ((A))、かつ、この場合に該ICチップ42の実装の光素子20と光通信可能な光通信位置に光検出素子20を配置する。光素子20と光検出素子22との間の光通信状態に基づいて、ICチップ42を位置決めする((B))。

(もっと読む)

半導体装置及びそれを用いた光半導体リレー装置

【課題】 信号遮断時の出力端子間容量Coffを低減し、且つオン抵抗Ronを低減化

したSOI構造の半導体装置及びそれを用いた光半導体リレー装置を実現する。

【解決手段】 パワーMISFET20は、第1のシリコン基板1の表面上にBOX層(

酸化膜層)2が形成され、このBOX層2の表面上にN+ソース層7、P層6、低不純物

濃度オフセット層5、N+ドレイン層8が設けられている。このP層6上には、ゲート絶

縁膜9を介して第1のゲート電極10が設けられている。そして、第1のシリコン基板1

の裏面には、P層6に対向してBOX層2をゲート絶縁膜とする第2のゲート電極15が

設けられている。

(もっと読む)

光電変換モジュール、積層基板接合体

【課題】その目的は、全体の低背化を達成しやすくて、光部品と他部品とを高い精度で光結合でき、しかも比較的簡単に製造できる光電変換モジュールを提供すること。

【解決手段】本発明の光電変換モジュール41は、積層基板接合体40、光素子17、光結合部材31等を備える。積層基板接合体40は、複数の絶縁層52を積層してなる第1積層基板51と、複数の絶縁層62を積層してなる第2積層基板61とを備える。第1積層基板51及び第2積層基板61は、絶縁層52,62の積層方向を直交させた状態で接合され、かつ電気的に接続される。光素子17は第1積層基板51に搭載されている。光結合部材31は、第1積層基板51に設けられる。光結合部材31は、光素子17と光素子17に光結合されるべき他部品21との光軸合わせの際の位置基準となる。

(もっと読む)

半導体チップの製造方法、半導体チップ、半導体装置の製造法および半導体装置

【課題】貫通電極の形成に伴う半導体基板の金属汚染を抑制することができる半導体チップの製造方法を提供する。

【解決手段】一方表面に機能素子3が形成されたウエハWの当該一方表面に、ウエハWの厚さよりも浅い所定の深さの表面側凹所9を形成する。続いて、表面側凹所9内に非金属材料を供給して、当該非金属材料からなるダミープラグ8を形成する。次に、ウエハWにおいて上記一方表面とは反対の面である裏面Wrを機械的に研削して、ウエハWを表面側凹所9の深さより小さな厚さに薄型化して、表面側凹所9をウエハWを貫通する貫通孔にする。その後、この貫通孔内のダミープラグ8を除去し、さらに、この貫通孔内に金属材料を供給して貫通電極を形成する。

(もっと読む)

光導波モジュール及びその実装構造

【課題】 光結合ロスを低減することができる光導波モジュール及びその実装構造を提供すること。

【解決手段】 第1の半導体層7、絶縁層8及び第2の半導体層9とがこの順に積層され、第1の半導体層7と第2の半導体層9との間に光導波層10が形成されている光導波装置2と、光電変換素子(発光素子等の光入射手段3、受光素子等の受光手段4)とが、セラミクス等のインターポーザー5に配されている、光導波モジュール1。本発明の光導波モジュール1が、インターポーザー5を介して実装基板6に実装されている、光導波モジュールの実装構造。

(もっと読む)

1 - 20 / 24

[ Back to top ]