Fターム[5F092BB82]の内容

Fターム[5F092BB82]に分類される特許

1 - 20 / 201

磁気抵抗素子の製造方法

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

磁気センサ装置およびその製造方法

【課題】1つの基板に形成した複数の磁気抵抗素子部のピン磁性層を任意の方向に着磁させたとしても、着磁による熱拡散の影響を低減する。

【解決手段】基板10の一面11の上方に各磁気抵抗素子部50を形成する。次に、基板10のうち各磁気抵抗素子部50に対応する部分に溝13を形成して空間部14を形成する。この後、磁場の向きが第1の方向に設定された磁場中に、各磁気抵抗素子部50が形成された基板10を配置し、一方の磁気抵抗素子部50を局所的に加熱して磁場中アニールを行い、当該磁気抵抗素子部50のピン磁性層51の磁化の向きを第1の方向に着磁する。また、磁場の向きを第1の方向とは異なる第2の方向に設定した磁場中において、他方の磁気抵抗素子部50を局所的に加熱して磁場中アニールを行い、当該磁気抵抗素子部50のピン磁性層51の磁化の向きを第2の方向に着磁する。

(もっと読む)

磁気検出装置とその製造方法

【課題】本発明は、小型化に優れると共に高精度な電気抵抗の調整が可能である磁気検出装置とその製造方法を提供することを目的とする。

【解決手段】第一の短絡層41と第二の短絡層42とを、それぞれ第一の磁気抵抗効果素子層11と第一の抵抗素子層21とにのみ導通させ且つ一体に積層させて短絡することで、第一の磁気抵抗効果素子層11と第一の抵抗素子層21との電気抵抗を調整する。

(もっと読む)

磁気抵抗素子及びその製造方法

【課題】磁気抵抗素子の出力を低下させずに耐環境性の向上を図ること。

【解決手段】半導体に磁界を加えると抵抗が変化する磁気抵抗体10を備えている磁気抵抗素子で、磁気抵抗体10が、基板11上に設けられた薄膜状の半導体層12aからなる感磁部12と、感磁部12上に配置された複数の短絡電極13,13とを備え、半導体層12aの厚みが、0.4μm以上0.8μm以下である。半導体層12aの延在方向に対して垂直方向の半導体層の幅をW、複数の短絡電極間の一定間隔の距離をLとしたときに、距離Lと幅Wの比であるL/Wが、0.18以上0.22以下である。

(もっと読む)

スピン注入磁化反転素子

【課題】MgOを障壁層として磁化反転電流を低減したTMR素子構造を備える光変調素子を提供する。

【解決手段】光変調素子5は、磁化固定層11、MgOからなる障壁層12、磁化自由層13を積層してなるTMR素子構造1と、その上下に接続した上部電極3、下部電極2を備える。下部電極2は、組成がCu1-xCrx(0.07<x<0.42)である非晶質のCu−Cr合金からなり、磁化固定層11は非晶質の磁性体からなり、このような非晶質の層の上に、障壁層12としてMgO膜が形成されるため、MgO膜が強い(001)面配向を示して、TMR素子構造1の磁化反転電流を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

磁気センサ装置およびその製造方法

【課題】1つの基板に形成した複数の磁気抵抗素子部のピン磁性層を任意の方向に着磁させたとしても、磁気抵抗素子部の検出精度の低下を防止する。

【解決手段】基板10に各磁気抵抗素子部22に対応するヒータ部30をそれぞれ形成し、ヒータ部30の上方に各磁気抵抗素子部22を形成する。磁場の向きが基板10の一面13の面方向のうちの第1の方向に設定された磁場中において、一方の磁気抵抗素子部22に対応するヒータ部30を加熱して磁場中アニールを行い、当該磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きを第1の方向に着磁する。続いて、磁場の向きを第1の方向とは異なる第2の方向に設定した磁場中において、他方の磁気抵抗素子部22に対応するヒータ部30を加熱して磁場中アニールを行い、当該磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きを第2の方向に着磁する。

(もっと読む)

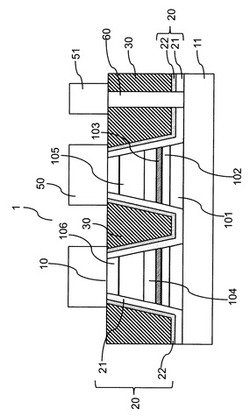

半導体記憶装置

【課題】磁気抵抗効果素子間の磁気的な干渉作用を遮断し、安定した動作を可能にし、且つ、容易に製造することができる半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、半導体基板上にマトリックス状に配列した複数の磁気抵抗効果素子を有し、各磁気抵抗効果素子は、半導体基板上に形成された第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成された第2の磁性層とからなる積層構造を有し、隣り合う各磁気抵抗効果素子の間には、金属、又は、磁性体材料が分散された絶縁膜が埋め込まれている。

(もっと読む)

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

記憶素子及びメモリ

【課題】書き込み電流を増大させることなく、熱安定性を改善することができるメモリを提供する。

【解決手段】情報を磁性体の磁化状態により保持する記憶層を有し、この記憶層に対して、中間層を介して磁化固定層が設けられ、中間層が絶縁体から成り、積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる記憶素子と、この記憶素子の積層方向に流す電流を供給する配線とを備え、記憶素子の上に隣接して積層された層に、記憶層と熱膨張係数の異なる、TiN,WN,TaN,Moのうちのいずれかの材料が用いられ、記憶層に歪が印加されているメモリを構成する。

(もっと読む)

磁気メモリデバイスの駆動方法及び磁気メモリデバイス

【課題】基準素子におけるディスターバンスの発生を防止することができる磁気メモリデバイスを提供する。

【解決手段】基準セル28が、基準素子20を含む。基準素子は、固定磁化層21、絶縁層22、自由磁化層23を含み、自由磁化層の磁化方向は固定磁化層の磁化方向と反平行であり、メモリセル18の磁気抵抗素子10が平行状態のときの抵抗値と反平行状態のときの抵抗値との間の抵抗値を有する。基準素子に、基準素子の固定磁化層から自由磁化層に向かう読出電流を流し、磁気抵抗素子の抵抗値と、基準素子の抵抗値との大小関係に依存する物理量を検出することにより、情報の読出しを行う。

(もっと読む)

スピン注入型磁化反転素子、光変調素子および空間光変調器

【課題】スピン注入型磁化反転素子の中間層におけるMgOの(001)面配向性を向上する。

【解決手段】光変調素子(スピン注入型磁化反転素子)5は、垂直磁気異方性を示す磁化固定層51と、MgOからなる中間層52と、垂直磁気異方性を示す磁化自由層53とをこの順で積層したトンネル磁気抵抗型のスピン注入型磁化反転素子構造を備え、スピン注入型磁化反転素子構造の上下に設けられた一対の電極2、3を介して電流を供給されることにより磁化自由層53の磁化方向を変化させて、入射した光をその偏光方向を変化させて出射する。ここで、磁化自由層53は、遷移金属または遷移金属を含む合金からなる界面層53bと、Ta膜またはRu膜からなる緩衝層53cと、磁化方向が反転される磁性層である主層53aとをこの順で積層して構成した。

(もっと読む)

磁気記憶装置およびその製造方法

【課題】メモリセルまたはMTJ素子が不良となることを抑制することができるとともに、製造コストが増加するのを抑制することができる磁気記憶装置を提供する。

【解決手段】本実施形態の磁気記憶装置は、半導体層に離間して設けられたソース領域/ドレイン領域と、前記ソース領域/ドレイン領域間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域/ドレイン領域にそれぞれ設けられたソース電極/ドレイン電極と、前記ソース電極/ドレイン電極のうちの一方の電極上に設けられ、少なくとも第1および第2強磁性層と、前記第1および第2強磁性層間に設けられた絶縁性のトンネルバリア層とを備えた第1積層構造と、前記ソース電極/ドレイン電極のうちの他方の電極上に設けられ、少なくとも前記第1および第2強磁性層と同じ材料で形成された層を有し、前記第1積層構造と実質的に同じ高さを有するコンタクトプラグと、を備えている。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 界面磁性層が十分に結晶化された磁気ランダムアクセスメモリ及びその製造方法を提供する。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、第1の磁性層、第1の界面磁性層、非磁性層、第2の界面磁性層、及び第2の磁性層が順に積層された磁気抵抗効果素子を有する。前記第1の磁性層の下層、前記第1の磁性層と前記第1の界面磁性層との間、前記第2の界面磁性層と前記第2の磁性層との間、及び前記第2の磁性層上のいずれかに第1の金属原子、第2の金属原子、及びB原子を含む金属層が設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ロジック混載MRAMにおいて、LSIの多層配線形成プロセスがMRAMの特性変動を引き起こす不都合、また、MRAMの形成プロセスが多層配線の特性変動を引き起こす不都合を軽減すること。

【解決手段】多層配線層に含まれる配線層Aの中に、配線層Bに形成された第1の配線104bに接し、互いに絶縁している少なくとも2つの第1の磁化固定層50a及び50bと、2つの第1の磁化固定層50a及び50bと平面視で重なり、かつ、第1の磁化固定層50a及び50bと接続している磁化自由層10と、磁化自由層10の上に位置する非磁性層40と、非磁性層40の上に位置する第2の磁化固定層104aと、を有するMRAMが形成されている半導体装置。

(もっと読む)

1 - 20 / 201

[ Back to top ]