半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

近年、TMR(Tunneling Magnetoresistive)効果、もしくは、GMR(Giant Magnetoresistive)効果を利用した磁気ランダムアクセスメモリ(MRAM:Magnetic Random Access Memory)を実現すべく、様々な技術が提案されている。

【0003】

MRAMは、不揮発性半導体記憶装置の1つであり、磁性トンネル接合(Magnetic Tunnel Junction:以下、MTJと略す)素子を有している。詳細には、このMTJ素子の構造は、基本的には、磁化方向を変えることでデータを記憶させるための磁化膜からなる記憶層、一方向に磁化を固定して用いるための磁化膜からなる参照層、及び、これらの層の間に形成された絶縁膜からなるトンネル接合層(非磁性層)の3層からなる積層構造をもつ。記憶層/トンネル接合層/参照層からなるMTJ素子に電流を流すと、TMR効果により、参照層の磁化方向に対して、記憶層の磁化方向が変化することによりMTJ素子の抵抗値が変化し、具体的には、記憶層と参照層との磁化方向が平行のときには極小値を、反平行のときには極大値をとる。このような状態を“1”、“0”情報として記憶するのである。

【0004】

上記のようなMRAMにおいて、実用化に向けて数々の技術が提案されている。スピン偏極電流による磁化方向の反転が理論的にも実験的にも確認されたことから、これらの技術の1つとして、スピン偏極電流を利用したMRAMが提案されている。この提案によれば、磁性層にスピン偏極電流を流すだけで磁性層の磁化反転を実現でき、さらに、磁性層の体積が小さければ、磁性層の反転のために注入されるスピン偏極電子も少なくて済むため、微細化及び低電流化を両立できると期待されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−141210号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供するものである。

【課題を解決するための手段】

【0007】

本発明の実施形態によれば、半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、前記各記憶素子の前記側面において膜厚が10nm以下である保護膜と、前記層間絶縁膜中に形成されたコンタクトとを備え、前記保護膜は、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、前記第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

【図面の簡単な説明】

【0008】

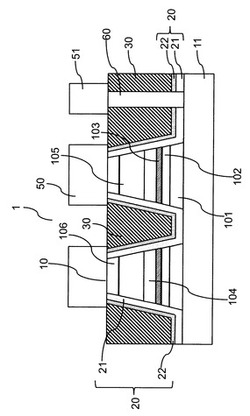

【図1】第1の実施形態にかかる半導体記憶装置の断面図である。

【図2】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その1)である。

【図3】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その2)である。

【図4】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その3)である。

【図5】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その4)である。

【図6】第2の実施形態にかかる半導体記憶装置の断面図である。

【図7】第2の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その1)である。

【図8】第2の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その2)である。

【発明を実施するための形態】

【0009】

以下、図面を参照して、実施形態を説明する。ただし、本発明はこの実施形態に限定されるものではない。なお、全図面にわたり共通する部分には、共通する符号を付すものとし、重複する説明は省略する。また、図面は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置とは異なる個所もあるが、これらは以下の説明と公知の技術とを参酌して適宜、設計変更することができる。

【0010】

(第1の実施形態)

図1を用いて本実施形態のMRAM(半導体記憶装置)1を説明する。図1は、本実施形態のMRAM1の断面図である。ここでは、MTJ素子(記憶素子)10とそれを覆う保護膜20とについて説明するが、本発明は以下のような半導体記憶装置に限られるものではなく、様々な形態のMRAMにも適用することができ、さらReRAM(Resistance Change Random Access Memory)の有する抵抗変化素子等にも適用することができる。

【0011】

図1に示されるように、本実施形態にかかるMRAM1は、半導体基板11の上面に複数のMTJ素子10を有し、隣り合うMTJ素子10の間隔は例えば60nmであり、その間に層間絶縁膜30が埋め込まれている。MTJ素子10は、例えば、半導体基板11上に順次堆積された、下地層101、記憶層102、トンネル接合層103、参照層104、キャップ層105、コンタクト層106の積層構造からなるが、本実施形態のMTJ素子10はこのような構成の積層構造に限定されるものではなく、他の積層構造であっても良い。また、層間絶縁膜30は例えば酸化シリコン膜からなり、SOG(Spin On Glass)等を用いて各MTJ素子10の間に埋め込まれる。

【0012】

そして、各MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面とは、保護膜20で連続的に覆われている。なお、保護膜20が各MTJ素子10の上面の一部を覆っていても良い。詳細には、保護膜20は、MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面との上に連続的に形成された第1の保護膜21と、第1の保護膜21上に連続的に形成された第2の保護膜22とからなり、それぞれ、MTJ素子10の側面と半導体基板11の上面とを露出することのないコンフォーマルな膜である。さらに、第1の保護膜21と第2の保護膜22とを合わせた保護膜20の膜厚は、MTJ素子10の側面において10nm以下であることが好ましく、これより厚くなってしまうと、隣り合うMTJ素子10の間が狭くなってしまい、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことが難しくなるからである。また、このように保護膜20の膜厚が薄いため、MTJ素子10に保護膜20から大きな応力印加されることを避けることができ、この応力によるMTJ素子10の特性悪化を避けることができる。

【0013】

また、第1の保護膜21は、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなり、電気的な絶縁性を有し、且つ、誘電率が低い。従って、第1の保護膜21により、MTJ素子10を構成する各層間を電気的に絶縁し、且つ、隣り合うMTJ素子10の間に生じる寄生容量の増加を避けることができ、さらに、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。詳細には、第1の保護膜21を酸化シリコン膜から形成した場合には、寄生容量の増加を抑える効果がより高く、第1の保護膜21を窒化シリコン膜から形成した場合には、水分や酸素等がMTJ素子10に入り込むことを防ぐ効果がより高くなる。また、第1の保護膜21を酸窒化シリコン膜とした場合には、上記の酸化シリコン膜及び窒化シリコン膜の両方の効果を適度に兼ね備えることができる。

【0014】

また、第2の保護膜22は、結晶ボロン膜やアモルファスボロン膜といったボロン膜又は窒化ボロン膜からなる。ボロン膜又は窒化ボロン膜に含まれる原子結合は共有結合であるため、その結合は強く、よって第2の保護膜22は後の工程で行われるエッチングに対して耐性を有する。従って、第1の保護膜21と第2の保護膜22との膜厚、すなわち、保護膜20の膜厚が薄いものであっても、エッチング耐性を有する第2の保護膜がエッチングから第1の保護膜を保護しているため、MTJ素子10を構成する各層間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0015】

さらに、保護膜20において、第1の保護膜21は薄く、第2の保護膜22がそれに比べて厚い場合には、エッチング耐性のある膜が厚くなることから、コンタクトホール61の加工時のエッチングストップ膜として用いることができる。それに対して、第1の保護膜21が厚く、第2の保護膜22がそれに対して薄い場合には、低誘電率である膜が厚くなることから、隣り合うMTJ素子10の間の寄生容量をより抑えることができる。

【0016】

そして、図1に示されるように各MTJ素子10の上面の上には、各MTJ素子10と電気的に接続された配線50が配置されている。さらに、隣り合うMTJ素子10の間の層間絶縁膜30にはコンタクトホール61が形成されており、その中に、半導体基板11と、層間絶縁膜30上に位置する配線51とを電気的に接続するコンタクト60が形成されている。

【0017】

次に、図2から図5を用いて、本実施形態のMRAM1の製造方法の一例を説明する。図2から図5は、本実施形態の製造方法における各工程での断面図であり、図1に示すMRAM1の断面に対応するものである。ここでは、MTJ素子10を覆う保護膜20の製造方法について説明するが、本発明は以下の半導体記憶装置の製造方法に限られるものではない。

【0018】

図2(a)に示されるように、半導体基板11の上面に複数のMTJ素子10を周知の方法により形成する。隣り合うMTJ素子10の間隔は例えば60nmである。

【0019】

次に、図2(b)に示されるように、MTJ素子10の上面及び側面と、MTJ素子10の間に位置する半導体基板11の上面とを連続的に覆うように、窒化シリコン膜、酸化シリコン膜、又は、酸窒化シリコン膜(第1の保護膜)21を堆積する。すなわち、窒化シリコン膜、酸化シリコン膜、又は、酸窒化シリコン膜21は、MTJ素子10の側面と、半導体基板11の上面とを露出することのないコンフォーマルな膜として形成する。なお、窒化シリコン膜、酸化シリコン膜、又は、酸窒化シリコン膜21は、MTJ素子10の上面を覆っていても良い。以下、窒化シリコン膜21を形成するものとして説明するが、窒化シリコン膜21の形成は、熱ALD(Atomic Layer Deposition)法、プラズマALD(プラズマアシストALD)法、プラズマCVD(プラズマアシストCVD)法、スパッタ法等を用いて行うことができる。

【0020】

詳細には、熱ALD法は、カバレッジ率が例えば100%程度であるような、高いカバレッジ率を有する窒化シリコン膜21を容易に形成できる点で好ましく、しかしながら、プロセス温度が高温であるため、MTJ素子10が高温に弱い膜を含む場合には好ましいものではない。プラズマALD法は、熱CVD法により形成された膜に比べるとカバレッジ率は低くなるが、カバレッジ率が例えば60から80%程度であるようなシリコン窒化膜21を容易に形成することができ、さらに、プロセス温度が低温であってもコンフォーマルな膜を形成することができるという点で好ましい。プラズマCVD法は、カバレッジ率が例えば30から50%程度であるような窒化シリコン膜21が形成されやすいが、プロセス温度が低温であっても生産性(スループット)が高い膜が得られるという点で好ましい。スパッタ法は、カバレッジ率が例えば20から40%程度であるような窒化シリコン膜21が形成されやすいが、室温程度のプロセス温度であっても水素濃度が低い膜が得られる点で好ましい。

【0021】

そして、図3(c)に示されるように、窒化シリコン膜21を連続的に覆うように、ボロン膜又は窒化ボロン膜(第2の保護膜)22を周知の方法により堆積する。すなわち、ボロン膜又は窒化ボロン膜22は、窒化シリコン膜21の表面を露出することのないコンフォーマルな膜として形成する。この際様々な方法を選択することができるが、MTJ素子10が高温に弱い膜等を含む場合には、プロセス温度が高温とならない方法を選択することが好ましい。例えば、ジボラン、アンモニア、窒素等のガスを用いた300℃以下の熱CVD法を用いて形成する。なお、これらのガスの割合を変えることにより、所望の組成のボロン膜又は窒化ボロン膜22を形成することができる。

【0022】

なお、先に説明したように、窒化シリコン膜21とボロン膜又は窒化ボロン膜22とを合わせた保護膜20の膜厚がMTJ素子10の側面において10nm以下になるように、これらの膜を形成する。また、MTJ素子10の側面においてこれらの膜厚の合計が10nm以下になるような範囲であれば、窒化シリコン膜21、ボロン膜又は窒化ボロン膜22のそれぞれの膜厚は、保護膜20に対して求める性質に応じて変えることができる。なお、保護膜20をMTJ素子の上面に形成した場合には、MTJ素子10の上面における保護膜20の膜厚は、MTJ素子10の側面における膜厚よりも薄くても良い。

【0023】

さらに、図3(d)に示されるように、保護膜20に覆われたMTJ素子10の間を埋め込むように、SOGを用いて層間絶縁膜30を形成し、その上面をCMP(Chemical Mechanical Polishing)等を用いて平坦化する。

【0024】

次に、図4(e)に示すように、保護膜20に覆われたMTJ素子10の上面と層間絶縁膜30の上面との上にマスク70を形成する。このマスク70は、層間保護膜30の上面を覆い、且つ、保護膜20に覆われたMTJ素子10の上面を露出するように、形成されている。

【0025】

そして、マスク70から露出した保護膜20を、言い換えると、MTJ素子10の上面に位置する保護膜20を除去する。さらに、マスク70を除去し、層間絶縁膜30を平坦化すると、図4(f)に示すような構造を得る。

【0026】

次に、図5(g)に示すように、隣り合うMTJ素子10の間の層間絶縁膜30中に、RIE(Reactive Ion Etching)等のドライエッチングを用いてコンタクトホール61を形成する。

【0027】

そして、図5(h)に示すように、このコンタクトホール61中にコンタクト60を形成する。

【0028】

さらに周知の工程を経て本実施形態のMRAM1を形成する。

【0029】

本実施形態によれば、保護膜20の一部として、ボロン膜又は窒化ボロン膜からなる第2の保護膜22を設けることにより、これらの膜がエッチング耐性を有することから、保護膜20の膜厚が薄いものであっても、エッチング工程において保護膜20がエッチングされることを避け、MTJ素子10や半導体基板11をエッチングから保護することができる。

【0030】

詳細には、MRAM1等の半導体記憶装置に対しては微細化が求められており、これに対応するためにMTJ素子10を微細化した場合には、隣り合うMTJ素子10の間隔が狭くなるため、層間絶縁膜30を埋め込むための空間の幅が狭くなり、言い換えるとこの空間のアスペクト比が高くなる。このようなアスペクト比の高い空間に層間絶縁膜30を埋め込む際、層間絶縁膜30中にボイドが生じることを避けることは難しい。従って、MTJ素子10を微細化しつつMTJ素子10の間隔をより広げるために、MTJ素子10を覆う保護膜20をより薄くすることが好ましく、すなわち、MTJ素子10の間隔をより広げつつMTJ素子10を保護するために、保護膜20は、膜厚が薄く、且つ、MTJ素子10の側面と、MTJ素子10の間に位置する半導体基板11の上面とを露出することのない連続的なコンフォーマルな膜であることが好ましい。

【0031】

しかしながら、保護膜20を薄い膜、例えば薄い窒化シリコン膜のみで構成した場合には、窒化シリコン膜はエッチングに対する耐性が低く、さらに、その膜厚が薄いために、層間絶縁膜30中にドライエッチングを用いてコンタクトホール61を形成する際に、窒化シリコン膜のみで構成された保護膜20がエッチングされ、保護膜20がMTJ素子10を保護する機能を発揮することができなくなり、酸素や水分等により劣化されやすい膜からなるMTJ素子10の記憶層102、参照層104やトンネル接合膜103等が層間絶縁膜30からの酸素や水分等により劣化され、それによってMTJ素子10の磁気特性を劣化させてしまう可能性がある。また、コンタクトホール61が半導体基板11を突き抜けてしまう可能性がある。

【0032】

一方、本実施形態によれば、保護膜20の一部として、ボロン膜又は窒化ボロン膜からなる第2の保護膜22をMTJ素子10の側面と隣り合う各MTJ素子10の間の半導体基板11とを覆うように設けることにより、ボロン膜又は窒化ボロン膜の原子結合は共有結合であるため、その結合は強く、従ってエッチング耐性を有することから、保護膜20を薄く形成した場合であっても、エッチング工程において保護膜20がエッチングされることを避け、ひいては、MTJ素子10が劣化したり、半導体基板11がエッチングされたりすることを避けることができる。

【0033】

さらに、本実施形態によれば、保護膜20をMTJ素子10の側面において10nm以下の膜厚を持つ薄い膜とすることにより、保護膜20の存在により隣り合うMTJ素子10の間を狭くすることを避け、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことを容易にする。さらに、MTJ素子10に保護膜20から大きな応力が印加されることを避け、ひいてはMTJ素子10の特性を悪化させことを避けることができる。

【0034】

また、本実施形態によれば、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなるコンフォーマルな第1の保護膜21と、前記第1の保護膜21上に形成されたボロン膜又は窒化ボロン膜からなるコンフォーマルな第2の保護膜22とからなる積層構造の保護膜20により、MTJ素子10の側面と隣り合う各MTJ素子10の間の半導体基板11とを覆うことにより、MTJ素子10の各層間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0035】

そして、本実施形態によれば、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜21と、ボロン膜又は窒化ボロン膜からなる第2の保護膜22とからなる保護膜20を、先に説明した方法で形成することにより、このような保護膜20がMTJ素子10の側面上に存在することに起因して、もしくは、保護膜20の形成過程に起因して、MTJ素子10が酸化・還元されることはなく、従って、MTJ素子10の特性を劣化させることを避けることができる。さらに、保護膜20は、その形成におけるプロセス温度が例えば300℃以下といった低温であっても、コンフォーマルに形成することができるようなものであるため、保護膜20の形成の際の熱によりMTJ素子10の特性を悪化させることを避けることができる。

【0036】

(第2の実施形態)

第1の実施形態では保護膜20を第1の保護膜21と第2の保護膜22とからなるものとしていたが、本実施形態では、窒化ボロン膜のみからなる保護膜23を用いる点で、第1の実施形態と異なる。このように、窒化ボロン膜のみからなる保護膜23を用いることにより、MRAM1の製造コスト及び製造時間を減らすことができる。

【0037】

図6を用いて本実施形態のMRAM(半導体記憶装置)1を説明する。図6は、本実施形態のMRAM1の断面図である。ここでは、MTJ素子(記憶素子)10とそれを覆う保護膜20とについて説明するが、本発明は以下のような半導体記憶装置に限られるものではなく、様々な形態のMRAMにも適用することができ、さらにReRAMの有する抵抗変化素子等にも適用することができる。なお、以下の本実施形態の説明において、第1の実施形態と同じ構成および機能を有する部分は、第1の実施形態と同じ符号を付し、その説明は省略するものとする。

【0038】

図6に示されるように、本実施形態にかかるMRAM1は、第1の実施形態と同様に、半導体基板11の上面に複数のMTJ素子10を有し、隣り合うMTJ素子10の間に層間絶縁膜30が埋め込まれている。図6中のMTJ素子10は、第1の実施形態と同様の積層構造からなるが、本実施形態のMTJ素子10はこのような構成の積層構造に限定されるものではなく、他の積層構造であってもかまわない。

【0039】

そして、各MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面とは、保護膜23で連続的に覆われている。なお、保護膜23が各MTJ素子10の上面の一部を覆っていても良い。詳細には、保護膜23は、MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面との上に形成された窒化ボロン膜からなり、すなわち、保護膜23は、MTJ素子10の側面と半導体基板11の上面とを露出することのない連続したコンフォーマルな膜である。窒化ボロン膜は、絶縁性を有し、且つ、共有結合であることからエッチング耐性を有する。さらに、第1の実施形態と同様に、保護膜23の膜厚は、MTJ素子10の側面において10nm以下であることが好ましく、これより厚くなってしまうと、隣り合うMTJ素子10の間が狭くなってしまい、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことが難しくなるからである。また、このように保護膜23の膜厚が薄いため、MTJ素子10に保護膜23から大きな応力印加されることを避けることができ、この応力によりMTJ素子10の特性を悪化させることを避けることができる。なお、保護膜23をMTJ素子の上面に形成した場合には、MTJ素子10の上面における保護膜23の膜厚は、MTJ素子10の側面における膜厚よりも薄くても良い。従って、この第2の実施形態においても、第1の実施形態と同様に、保護膜23の膜厚が薄いものであっても、保護膜23はエッチングされることがないため、保護膜23は、MTJ素子10を構成する各層間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0040】

次に、図7及び図8を用いて、本実施形態のMRAM1の製造方法の一例を説明する。図7及び図8は、本実施形態の製造方法における各工程での断面図であり、図6に示すMRAM1の断面に対応するものである。ここでは、MTJ素子10を覆う保護膜23の製造方法について説明するが、本発明は以下の半導体記憶装置の製造方法に限られるものではない。なお、以下の本実施形態の説明においては、第1の実施形態と同じ個所についての説明は省略するものとする。

【0041】

図7(a)に示されるように、第1の実施形態と同様に、半導体基板11の上面に複数のMTJ素子10を周知の方法により形成する。

【0042】

次に、図7(b)に示されるように、MTJ素子10の側面と、MTJ素子10の間の半導体基板11の上面とを連続的に覆うように、窒化ボロン膜(保護膜)23を周知の方法により堆積する。すなわち、窒化ボロン膜23は、MTJ素子10の側面と、半導体基板11の上面とを露出することのないコンフォーマルな膜として形成する。なお、窒化ボロン膜23は、MTJ素子10の上面を覆っていても良い。この際様々な方法を選択することができるが、MTJ素子10が高温に弱い膜等を含む場合には、プロセス温度が高温とならない方法を選択することが好ましい。例えば、ジボラン、アンモニア、窒素等のガスを用いた300℃以下の熱CVD法により形成する。なお、これらのガスの割合を変えることにより、所望の組成の窒化ボロン膜23を形成することができる。

【0043】

また、第1の実施形態と同様に、窒化ボロン膜23の膜厚が、MTJ素子10の側面において10nm以下になるように形成する。なお、窒化ボロン膜23をMTJ素子の上面に形成した場合には、MTJ素子10の上面における窒化ボロン膜23の膜厚は、MTJ素子10の側面における膜厚よりも薄くても良い。

【0044】

さらに、第1の実施形態と同様に、保護膜23で覆われたMTJ素子10の間を埋め込むように、層間絶縁膜30を形成し、平坦化する。そして、保護膜20に覆われたMTJ素子10の上面と層間絶縁膜30の上面との上にマスク70を形成し、マスク70から露出したMTJ素子10の上面に位置する保護膜20を除去する。さらに、マスク70を除去して、層間絶縁膜30に対して平坦化を行うと、図8(c)に示すような構造を得る。

【0045】

次に、図8(d)に示すように、第1の実施形態と同様に、隣り合うMTJ素子10の間の層間絶縁膜30中に、ドライエッチングを用いてコンタクトホール61を形成し、このコンタクトホール61中にコンタクト60を形成する。さらに周知の工程を経て本実施形態のMRAM1を形成する。

【0046】

本実施形態によれば、保護膜23として、絶縁性を有し、且つ、エッチング耐性を有するコンフォーマルな窒化ボロン膜を用いることにより、保護膜23の膜厚が薄いものであっても、エッチング工程において保護膜23がエッチングされることを避け、ひいては、MTJ素子10が劣化したり、半導体基板11がエッチングされたりすることを避けることができる。さらに、MTJ素子10の各層の間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0047】

また、本実施形態によれば、窒化ボロン膜のみからなる保護膜23を用いることにより、MRAM1の製造コスト及び製造時間を減らすことができる。

【0048】

さらに、本実施形態によれば、保護膜23をMTJ素子10の側面において10nm以下の膜厚を持つ膜とすることにより、保護膜23の存在により隣り合うMTJ素子10の間を狭くすることを避け、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことを容易にする。さらに、MTJ素子10に保護膜23から大きな応力が印加されることを避け、ひいてはMTJ素子10の特性を悪化させことを避けることができる。

【0049】

そして、本実施形態によれば、窒化ボロン膜からなる保護膜23を、先に説明した方法で形成することにより、このような保護膜23がMTJ素子10の側面上に存在すること、もしくは、保護膜23の形成過程に起因して、MTJ素子10が酸化・還元されることはなく、従って、MTJ素子10の特性を劣化させることを避けることができる。さらに、保護膜23は、その形成におけるプロセス温度が例えば300℃以下といった低温であっても、コンフォーマルに形成することができるような方法があるため、保護膜23の形成の際の熱によりMTJ素子10の特性を悪化させることを避けることができる。

【0050】

なお、本実施形態においては、保護膜23は各MTJ素子10の上面の一部を覆っていても良く、また、MTJ素子10の上面の一部を覆う保護膜23は、MTJ素子10の側面上の保護膜23の膜厚にくらべて薄くても良い。

【0051】

なお、上記の実施形態においては、半導体基板11は、必ずしもシリコン基板でなくてもよく、他の基板でも良い。また、このような種々の基板上に半導体構造等が形成されたものでも良い。また、上記の実施例においては、MRAMを例に説明したがこれに限るものではなく、抵抗変化素子を構成する層を酸化等から保護する必要があるReRAM等の半導体装置にも適用することができる。

【0052】

本発明の実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0053】

1 MRAM(半導体記憶装置)

10 MTJ素子(記憶素子)

11 半導体基板

20、23 保護膜

21 第1の保護膜

22 第2の保護膜

30 層間絶縁膜

50、51 配線

60 コンタクト

61 コンタクトホール

70 マスク

101 下地層

102 記憶層

103 トンネル接合層

104 参照層

105 キャップ層

106 コンタクト層

【技術分野】

【0001】

本発明の実施形態は、半導体記憶装置及びその製造方法に関する。

【背景技術】

【0002】

近年、TMR(Tunneling Magnetoresistive)効果、もしくは、GMR(Giant Magnetoresistive)効果を利用した磁気ランダムアクセスメモリ(MRAM:Magnetic Random Access Memory)を実現すべく、様々な技術が提案されている。

【0003】

MRAMは、不揮発性半導体記憶装置の1つであり、磁性トンネル接合(Magnetic Tunnel Junction:以下、MTJと略す)素子を有している。詳細には、このMTJ素子の構造は、基本的には、磁化方向を変えることでデータを記憶させるための磁化膜からなる記憶層、一方向に磁化を固定して用いるための磁化膜からなる参照層、及び、これらの層の間に形成された絶縁膜からなるトンネル接合層(非磁性層)の3層からなる積層構造をもつ。記憶層/トンネル接合層/参照層からなるMTJ素子に電流を流すと、TMR効果により、参照層の磁化方向に対して、記憶層の磁化方向が変化することによりMTJ素子の抵抗値が変化し、具体的には、記憶層と参照層との磁化方向が平行のときには極小値を、反平行のときには極大値をとる。このような状態を“1”、“0”情報として記憶するのである。

【0004】

上記のようなMRAMにおいて、実用化に向けて数々の技術が提案されている。スピン偏極電流による磁化方向の反転が理論的にも実験的にも確認されたことから、これらの技術の1つとして、スピン偏極電流を利用したMRAMが提案されている。この提案によれば、磁性層にスピン偏極電流を流すだけで磁性層の磁化反転を実現でき、さらに、磁性層の体積が小さければ、磁性層の反転のために注入されるスピン偏極電子も少なくて済むため、微細化及び低電流化を両立できると期待されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−141210号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供するものである。

【課題を解決するための手段】

【0007】

本発明の実施形態によれば、半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、前記各記憶素子の前記側面において膜厚が10nm以下である保護膜と、前記層間絶縁膜中に形成されたコンタクトとを備え、前記保護膜は、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、前記第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態にかかる半導体記憶装置の断面図である。

【図2】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その1)である。

【図3】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その2)である。

【図4】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その3)である。

【図5】第1の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その4)である。

【図6】第2の実施形態にかかる半導体記憶装置の断面図である。

【図7】第2の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その1)である。

【図8】第2の実施形態にかかる半導体記憶装置の製造方法を説明する断面図(その2)である。

【発明を実施するための形態】

【0009】

以下、図面を参照して、実施形態を説明する。ただし、本発明はこの実施形態に限定されるものではない。なお、全図面にわたり共通する部分には、共通する符号を付すものとし、重複する説明は省略する。また、図面は発明の説明とその理解を促すための模式図であり、その形状や寸法、比などは実際の装置とは異なる個所もあるが、これらは以下の説明と公知の技術とを参酌して適宜、設計変更することができる。

【0010】

(第1の実施形態)

図1を用いて本実施形態のMRAM(半導体記憶装置)1を説明する。図1は、本実施形態のMRAM1の断面図である。ここでは、MTJ素子(記憶素子)10とそれを覆う保護膜20とについて説明するが、本発明は以下のような半導体記憶装置に限られるものではなく、様々な形態のMRAMにも適用することができ、さらReRAM(Resistance Change Random Access Memory)の有する抵抗変化素子等にも適用することができる。

【0011】

図1に示されるように、本実施形態にかかるMRAM1は、半導体基板11の上面に複数のMTJ素子10を有し、隣り合うMTJ素子10の間隔は例えば60nmであり、その間に層間絶縁膜30が埋め込まれている。MTJ素子10は、例えば、半導体基板11上に順次堆積された、下地層101、記憶層102、トンネル接合層103、参照層104、キャップ層105、コンタクト層106の積層構造からなるが、本実施形態のMTJ素子10はこのような構成の積層構造に限定されるものではなく、他の積層構造であっても良い。また、層間絶縁膜30は例えば酸化シリコン膜からなり、SOG(Spin On Glass)等を用いて各MTJ素子10の間に埋め込まれる。

【0012】

そして、各MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面とは、保護膜20で連続的に覆われている。なお、保護膜20が各MTJ素子10の上面の一部を覆っていても良い。詳細には、保護膜20は、MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面との上に連続的に形成された第1の保護膜21と、第1の保護膜21上に連続的に形成された第2の保護膜22とからなり、それぞれ、MTJ素子10の側面と半導体基板11の上面とを露出することのないコンフォーマルな膜である。さらに、第1の保護膜21と第2の保護膜22とを合わせた保護膜20の膜厚は、MTJ素子10の側面において10nm以下であることが好ましく、これより厚くなってしまうと、隣り合うMTJ素子10の間が狭くなってしまい、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことが難しくなるからである。また、このように保護膜20の膜厚が薄いため、MTJ素子10に保護膜20から大きな応力印加されることを避けることができ、この応力によるMTJ素子10の特性悪化を避けることができる。

【0013】

また、第1の保護膜21は、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなり、電気的な絶縁性を有し、且つ、誘電率が低い。従って、第1の保護膜21により、MTJ素子10を構成する各層間を電気的に絶縁し、且つ、隣り合うMTJ素子10の間に生じる寄生容量の増加を避けることができ、さらに、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。詳細には、第1の保護膜21を酸化シリコン膜から形成した場合には、寄生容量の増加を抑える効果がより高く、第1の保護膜21を窒化シリコン膜から形成した場合には、水分や酸素等がMTJ素子10に入り込むことを防ぐ効果がより高くなる。また、第1の保護膜21を酸窒化シリコン膜とした場合には、上記の酸化シリコン膜及び窒化シリコン膜の両方の効果を適度に兼ね備えることができる。

【0014】

また、第2の保護膜22は、結晶ボロン膜やアモルファスボロン膜といったボロン膜又は窒化ボロン膜からなる。ボロン膜又は窒化ボロン膜に含まれる原子結合は共有結合であるため、その結合は強く、よって第2の保護膜22は後の工程で行われるエッチングに対して耐性を有する。従って、第1の保護膜21と第2の保護膜22との膜厚、すなわち、保護膜20の膜厚が薄いものであっても、エッチング耐性を有する第2の保護膜がエッチングから第1の保護膜を保護しているため、MTJ素子10を構成する各層間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0015】

さらに、保護膜20において、第1の保護膜21は薄く、第2の保護膜22がそれに比べて厚い場合には、エッチング耐性のある膜が厚くなることから、コンタクトホール61の加工時のエッチングストップ膜として用いることができる。それに対して、第1の保護膜21が厚く、第2の保護膜22がそれに対して薄い場合には、低誘電率である膜が厚くなることから、隣り合うMTJ素子10の間の寄生容量をより抑えることができる。

【0016】

そして、図1に示されるように各MTJ素子10の上面の上には、各MTJ素子10と電気的に接続された配線50が配置されている。さらに、隣り合うMTJ素子10の間の層間絶縁膜30にはコンタクトホール61が形成されており、その中に、半導体基板11と、層間絶縁膜30上に位置する配線51とを電気的に接続するコンタクト60が形成されている。

【0017】

次に、図2から図5を用いて、本実施形態のMRAM1の製造方法の一例を説明する。図2から図5は、本実施形態の製造方法における各工程での断面図であり、図1に示すMRAM1の断面に対応するものである。ここでは、MTJ素子10を覆う保護膜20の製造方法について説明するが、本発明は以下の半導体記憶装置の製造方法に限られるものではない。

【0018】

図2(a)に示されるように、半導体基板11の上面に複数のMTJ素子10を周知の方法により形成する。隣り合うMTJ素子10の間隔は例えば60nmである。

【0019】

次に、図2(b)に示されるように、MTJ素子10の上面及び側面と、MTJ素子10の間に位置する半導体基板11の上面とを連続的に覆うように、窒化シリコン膜、酸化シリコン膜、又は、酸窒化シリコン膜(第1の保護膜)21を堆積する。すなわち、窒化シリコン膜、酸化シリコン膜、又は、酸窒化シリコン膜21は、MTJ素子10の側面と、半導体基板11の上面とを露出することのないコンフォーマルな膜として形成する。なお、窒化シリコン膜、酸化シリコン膜、又は、酸窒化シリコン膜21は、MTJ素子10の上面を覆っていても良い。以下、窒化シリコン膜21を形成するものとして説明するが、窒化シリコン膜21の形成は、熱ALD(Atomic Layer Deposition)法、プラズマALD(プラズマアシストALD)法、プラズマCVD(プラズマアシストCVD)法、スパッタ法等を用いて行うことができる。

【0020】

詳細には、熱ALD法は、カバレッジ率が例えば100%程度であるような、高いカバレッジ率を有する窒化シリコン膜21を容易に形成できる点で好ましく、しかしながら、プロセス温度が高温であるため、MTJ素子10が高温に弱い膜を含む場合には好ましいものではない。プラズマALD法は、熱CVD法により形成された膜に比べるとカバレッジ率は低くなるが、カバレッジ率が例えば60から80%程度であるようなシリコン窒化膜21を容易に形成することができ、さらに、プロセス温度が低温であってもコンフォーマルな膜を形成することができるという点で好ましい。プラズマCVD法は、カバレッジ率が例えば30から50%程度であるような窒化シリコン膜21が形成されやすいが、プロセス温度が低温であっても生産性(スループット)が高い膜が得られるという点で好ましい。スパッタ法は、カバレッジ率が例えば20から40%程度であるような窒化シリコン膜21が形成されやすいが、室温程度のプロセス温度であっても水素濃度が低い膜が得られる点で好ましい。

【0021】

そして、図3(c)に示されるように、窒化シリコン膜21を連続的に覆うように、ボロン膜又は窒化ボロン膜(第2の保護膜)22を周知の方法により堆積する。すなわち、ボロン膜又は窒化ボロン膜22は、窒化シリコン膜21の表面を露出することのないコンフォーマルな膜として形成する。この際様々な方法を選択することができるが、MTJ素子10が高温に弱い膜等を含む場合には、プロセス温度が高温とならない方法を選択することが好ましい。例えば、ジボラン、アンモニア、窒素等のガスを用いた300℃以下の熱CVD法を用いて形成する。なお、これらのガスの割合を変えることにより、所望の組成のボロン膜又は窒化ボロン膜22を形成することができる。

【0022】

なお、先に説明したように、窒化シリコン膜21とボロン膜又は窒化ボロン膜22とを合わせた保護膜20の膜厚がMTJ素子10の側面において10nm以下になるように、これらの膜を形成する。また、MTJ素子10の側面においてこれらの膜厚の合計が10nm以下になるような範囲であれば、窒化シリコン膜21、ボロン膜又は窒化ボロン膜22のそれぞれの膜厚は、保護膜20に対して求める性質に応じて変えることができる。なお、保護膜20をMTJ素子の上面に形成した場合には、MTJ素子10の上面における保護膜20の膜厚は、MTJ素子10の側面における膜厚よりも薄くても良い。

【0023】

さらに、図3(d)に示されるように、保護膜20に覆われたMTJ素子10の間を埋め込むように、SOGを用いて層間絶縁膜30を形成し、その上面をCMP(Chemical Mechanical Polishing)等を用いて平坦化する。

【0024】

次に、図4(e)に示すように、保護膜20に覆われたMTJ素子10の上面と層間絶縁膜30の上面との上にマスク70を形成する。このマスク70は、層間保護膜30の上面を覆い、且つ、保護膜20に覆われたMTJ素子10の上面を露出するように、形成されている。

【0025】

そして、マスク70から露出した保護膜20を、言い換えると、MTJ素子10の上面に位置する保護膜20を除去する。さらに、マスク70を除去し、層間絶縁膜30を平坦化すると、図4(f)に示すような構造を得る。

【0026】

次に、図5(g)に示すように、隣り合うMTJ素子10の間の層間絶縁膜30中に、RIE(Reactive Ion Etching)等のドライエッチングを用いてコンタクトホール61を形成する。

【0027】

そして、図5(h)に示すように、このコンタクトホール61中にコンタクト60を形成する。

【0028】

さらに周知の工程を経て本実施形態のMRAM1を形成する。

【0029】

本実施形態によれば、保護膜20の一部として、ボロン膜又は窒化ボロン膜からなる第2の保護膜22を設けることにより、これらの膜がエッチング耐性を有することから、保護膜20の膜厚が薄いものであっても、エッチング工程において保護膜20がエッチングされることを避け、MTJ素子10や半導体基板11をエッチングから保護することができる。

【0030】

詳細には、MRAM1等の半導体記憶装置に対しては微細化が求められており、これに対応するためにMTJ素子10を微細化した場合には、隣り合うMTJ素子10の間隔が狭くなるため、層間絶縁膜30を埋め込むための空間の幅が狭くなり、言い換えるとこの空間のアスペクト比が高くなる。このようなアスペクト比の高い空間に層間絶縁膜30を埋め込む際、層間絶縁膜30中にボイドが生じることを避けることは難しい。従って、MTJ素子10を微細化しつつMTJ素子10の間隔をより広げるために、MTJ素子10を覆う保護膜20をより薄くすることが好ましく、すなわち、MTJ素子10の間隔をより広げつつMTJ素子10を保護するために、保護膜20は、膜厚が薄く、且つ、MTJ素子10の側面と、MTJ素子10の間に位置する半導体基板11の上面とを露出することのない連続的なコンフォーマルな膜であることが好ましい。

【0031】

しかしながら、保護膜20を薄い膜、例えば薄い窒化シリコン膜のみで構成した場合には、窒化シリコン膜はエッチングに対する耐性が低く、さらに、その膜厚が薄いために、層間絶縁膜30中にドライエッチングを用いてコンタクトホール61を形成する際に、窒化シリコン膜のみで構成された保護膜20がエッチングされ、保護膜20がMTJ素子10を保護する機能を発揮することができなくなり、酸素や水分等により劣化されやすい膜からなるMTJ素子10の記憶層102、参照層104やトンネル接合膜103等が層間絶縁膜30からの酸素や水分等により劣化され、それによってMTJ素子10の磁気特性を劣化させてしまう可能性がある。また、コンタクトホール61が半導体基板11を突き抜けてしまう可能性がある。

【0032】

一方、本実施形態によれば、保護膜20の一部として、ボロン膜又は窒化ボロン膜からなる第2の保護膜22をMTJ素子10の側面と隣り合う各MTJ素子10の間の半導体基板11とを覆うように設けることにより、ボロン膜又は窒化ボロン膜の原子結合は共有結合であるため、その結合は強く、従ってエッチング耐性を有することから、保護膜20を薄く形成した場合であっても、エッチング工程において保護膜20がエッチングされることを避け、ひいては、MTJ素子10が劣化したり、半導体基板11がエッチングされたりすることを避けることができる。

【0033】

さらに、本実施形態によれば、保護膜20をMTJ素子10の側面において10nm以下の膜厚を持つ薄い膜とすることにより、保護膜20の存在により隣り合うMTJ素子10の間を狭くすることを避け、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことを容易にする。さらに、MTJ素子10に保護膜20から大きな応力が印加されることを避け、ひいてはMTJ素子10の特性を悪化させことを避けることができる。

【0034】

また、本実施形態によれば、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなるコンフォーマルな第1の保護膜21と、前記第1の保護膜21上に形成されたボロン膜又は窒化ボロン膜からなるコンフォーマルな第2の保護膜22とからなる積層構造の保護膜20により、MTJ素子10の側面と隣り合う各MTJ素子10の間の半導体基板11とを覆うことにより、MTJ素子10の各層間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0035】

そして、本実施形態によれば、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜21と、ボロン膜又は窒化ボロン膜からなる第2の保護膜22とからなる保護膜20を、先に説明した方法で形成することにより、このような保護膜20がMTJ素子10の側面上に存在することに起因して、もしくは、保護膜20の形成過程に起因して、MTJ素子10が酸化・還元されることはなく、従って、MTJ素子10の特性を劣化させることを避けることができる。さらに、保護膜20は、その形成におけるプロセス温度が例えば300℃以下といった低温であっても、コンフォーマルに形成することができるようなものであるため、保護膜20の形成の際の熱によりMTJ素子10の特性を悪化させることを避けることができる。

【0036】

(第2の実施形態)

第1の実施形態では保護膜20を第1の保護膜21と第2の保護膜22とからなるものとしていたが、本実施形態では、窒化ボロン膜のみからなる保護膜23を用いる点で、第1の実施形態と異なる。このように、窒化ボロン膜のみからなる保護膜23を用いることにより、MRAM1の製造コスト及び製造時間を減らすことができる。

【0037】

図6を用いて本実施形態のMRAM(半導体記憶装置)1を説明する。図6は、本実施形態のMRAM1の断面図である。ここでは、MTJ素子(記憶素子)10とそれを覆う保護膜20とについて説明するが、本発明は以下のような半導体記憶装置に限られるものではなく、様々な形態のMRAMにも適用することができ、さらにReRAMの有する抵抗変化素子等にも適用することができる。なお、以下の本実施形態の説明において、第1の実施形態と同じ構成および機能を有する部分は、第1の実施形態と同じ符号を付し、その説明は省略するものとする。

【0038】

図6に示されるように、本実施形態にかかるMRAM1は、第1の実施形態と同様に、半導体基板11の上面に複数のMTJ素子10を有し、隣り合うMTJ素子10の間に層間絶縁膜30が埋め込まれている。図6中のMTJ素子10は、第1の実施形態と同様の積層構造からなるが、本実施形態のMTJ素子10はこのような構成の積層構造に限定されるものではなく、他の積層構造であってもかまわない。

【0039】

そして、各MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面とは、保護膜23で連続的に覆われている。なお、保護膜23が各MTJ素子10の上面の一部を覆っていても良い。詳細には、保護膜23は、MTJ素子10の側面と各MTJ素子10の間の半導体基板11の上面との上に形成された窒化ボロン膜からなり、すなわち、保護膜23は、MTJ素子10の側面と半導体基板11の上面とを露出することのない連続したコンフォーマルな膜である。窒化ボロン膜は、絶縁性を有し、且つ、共有結合であることからエッチング耐性を有する。さらに、第1の実施形態と同様に、保護膜23の膜厚は、MTJ素子10の側面において10nm以下であることが好ましく、これより厚くなってしまうと、隣り合うMTJ素子10の間が狭くなってしまい、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことが難しくなるからである。また、このように保護膜23の膜厚が薄いため、MTJ素子10に保護膜23から大きな応力印加されることを避けることができ、この応力によりMTJ素子10の特性を悪化させることを避けることができる。なお、保護膜23をMTJ素子の上面に形成した場合には、MTJ素子10の上面における保護膜23の膜厚は、MTJ素子10の側面における膜厚よりも薄くても良い。従って、この第2の実施形態においても、第1の実施形態と同様に、保護膜23の膜厚が薄いものであっても、保護膜23はエッチングされることがないため、保護膜23は、MTJ素子10を構成する各層間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0040】

次に、図7及び図8を用いて、本実施形態のMRAM1の製造方法の一例を説明する。図7及び図8は、本実施形態の製造方法における各工程での断面図であり、図6に示すMRAM1の断面に対応するものである。ここでは、MTJ素子10を覆う保護膜23の製造方法について説明するが、本発明は以下の半導体記憶装置の製造方法に限られるものではない。なお、以下の本実施形態の説明においては、第1の実施形態と同じ個所についての説明は省略するものとする。

【0041】

図7(a)に示されるように、第1の実施形態と同様に、半導体基板11の上面に複数のMTJ素子10を周知の方法により形成する。

【0042】

次に、図7(b)に示されるように、MTJ素子10の側面と、MTJ素子10の間の半導体基板11の上面とを連続的に覆うように、窒化ボロン膜(保護膜)23を周知の方法により堆積する。すなわち、窒化ボロン膜23は、MTJ素子10の側面と、半導体基板11の上面とを露出することのないコンフォーマルな膜として形成する。なお、窒化ボロン膜23は、MTJ素子10の上面を覆っていても良い。この際様々な方法を選択することができるが、MTJ素子10が高温に弱い膜等を含む場合には、プロセス温度が高温とならない方法を選択することが好ましい。例えば、ジボラン、アンモニア、窒素等のガスを用いた300℃以下の熱CVD法により形成する。なお、これらのガスの割合を変えることにより、所望の組成の窒化ボロン膜23を形成することができる。

【0043】

また、第1の実施形態と同様に、窒化ボロン膜23の膜厚が、MTJ素子10の側面において10nm以下になるように形成する。なお、窒化ボロン膜23をMTJ素子の上面に形成した場合には、MTJ素子10の上面における窒化ボロン膜23の膜厚は、MTJ素子10の側面における膜厚よりも薄くても良い。

【0044】

さらに、第1の実施形態と同様に、保護膜23で覆われたMTJ素子10の間を埋め込むように、層間絶縁膜30を形成し、平坦化する。そして、保護膜20に覆われたMTJ素子10の上面と層間絶縁膜30の上面との上にマスク70を形成し、マスク70から露出したMTJ素子10の上面に位置する保護膜20を除去する。さらに、マスク70を除去して、層間絶縁膜30に対して平坦化を行うと、図8(c)に示すような構造を得る。

【0045】

次に、図8(d)に示すように、第1の実施形態と同様に、隣り合うMTJ素子10の間の層間絶縁膜30中に、ドライエッチングを用いてコンタクトホール61を形成し、このコンタクトホール61中にコンタクト60を形成する。さらに周知の工程を経て本実施形態のMRAM1を形成する。

【0046】

本実施形態によれば、保護膜23として、絶縁性を有し、且つ、エッチング耐性を有するコンフォーマルな窒化ボロン膜を用いることにより、保護膜23の膜厚が薄いものであっても、エッチング工程において保護膜23がエッチングされることを避け、ひいては、MTJ素子10が劣化したり、半導体基板11がエッチングされたりすることを避けることができる。さらに、MTJ素子10の各層の間を電気的に絶縁し、且つ、層間絶縁膜30からの水分や酸素等がMTJ素子10に入り込むことを防ぐことができる。

【0047】

また、本実施形態によれば、窒化ボロン膜のみからなる保護膜23を用いることにより、MRAM1の製造コスト及び製造時間を減らすことができる。

【0048】

さらに、本実施形態によれば、保護膜23をMTJ素子10の側面において10nm以下の膜厚を持つ膜とすることにより、保護膜23の存在により隣り合うMTJ素子10の間を狭くすることを避け、隣り合うMTJ素子10の間にボイドを生じることなく層間絶縁膜30を埋め込むことを容易にする。さらに、MTJ素子10に保護膜23から大きな応力が印加されることを避け、ひいてはMTJ素子10の特性を悪化させことを避けることができる。

【0049】

そして、本実施形態によれば、窒化ボロン膜からなる保護膜23を、先に説明した方法で形成することにより、このような保護膜23がMTJ素子10の側面上に存在すること、もしくは、保護膜23の形成過程に起因して、MTJ素子10が酸化・還元されることはなく、従って、MTJ素子10の特性を劣化させることを避けることができる。さらに、保護膜23は、その形成におけるプロセス温度が例えば300℃以下といった低温であっても、コンフォーマルに形成することができるような方法があるため、保護膜23の形成の際の熱によりMTJ素子10の特性を悪化させることを避けることができる。

【0050】

なお、本実施形態においては、保護膜23は各MTJ素子10の上面の一部を覆っていても良く、また、MTJ素子10の上面の一部を覆う保護膜23は、MTJ素子10の側面上の保護膜23の膜厚にくらべて薄くても良い。

【0051】

なお、上記の実施形態においては、半導体基板11は、必ずしもシリコン基板でなくてもよく、他の基板でも良い。また、このような種々の基板上に半導体構造等が形成されたものでも良い。また、上記の実施例においては、MRAMを例に説明したがこれに限るものではなく、抵抗変化素子を構成する層を酸化等から保護する必要があるReRAM等の半導体装置にも適用することができる。

【0052】

本発明の実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0053】

1 MRAM(半導体記憶装置)

10 MTJ素子(記憶素子)

11 半導体基板

20、23 保護膜

21 第1の保護膜

22 第2の保護膜

30 層間絶縁膜

50、51 配線

60 コンタクト

61 コンタクトホール

70 マスク

101 下地層

102 記憶層

103 トンネル接合層

104 参照層

105 キャップ層

106 コンタクト層

【特許請求の範囲】

【請求項1】

半導体基板の上面に形成された複数の記憶素子と、

隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、前記各記憶素子の前記側面において膜厚が10nm以下である保護膜と、

前記層間絶縁膜中に形成されたコンタクトと、

を備え、

前記保護膜は、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、前記第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する、

ことを特徴とする半導体記憶装置。

【請求項2】

半導体基板の上面に形成された複数の記憶素子と、

隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成された保護膜と、

前記層間絶縁膜中に形成されたコンタクトと、

を備え、

前記保護膜は、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、前記第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する、

ことを特徴とする半導体記憶装置。

【請求項3】

半導体基板の上面に形成された複数の記憶素子と、

隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、窒化ボロン膜からなる保護膜と、

前記層間絶縁膜中に形成されたコンタクトと、

を備える、

ことを特徴とする半導体記憶装置。

【請求項4】

前記保護膜の膜厚は、前記各記憶素子の側面において10nm以下であることを特徴とする請求項2又は3に記載の半導体記憶装置。

【請求項5】

前記記憶素子は、MTJ素子又は抵抗変化素子であることを特徴とする請求項1から4のいずれか1つに記載の半導体記憶装置。

【請求項6】

半導体基板の上面に複数の記憶素子を形成し、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜を連続的に堆積して、第1の保護膜を形成し、

前記第1の保護膜の上に、ボロン膜又は窒化ボロン膜を連続的に堆積して、第2の保護膜を形成し、

隣り合う前記各記憶素子の間に層間絶縁膜を埋め込み、

隣り合う前記各記憶素子の間の前記層間絶縁膜中にエッチングを用いてコンタクトホールを形成する、

ことを特徴とする半導体記憶装置の製造方法。

【請求項1】

半導体基板の上面に形成された複数の記憶素子と、

隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、前記各記憶素子の前記側面において膜厚が10nm以下である保護膜と、

前記層間絶縁膜中に形成されたコンタクトと、

を備え、

前記保護膜は、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、前記第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する、

ことを特徴とする半導体記憶装置。

【請求項2】

半導体基板の上面に形成された複数の記憶素子と、

隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成された保護膜と、

前記層間絶縁膜中に形成されたコンタクトと、

を備え、

前記保護膜は、前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、前記第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する、

ことを特徴とする半導体記憶装置。

【請求項3】

半導体基板の上面に形成された複数の記憶素子と、

隣り合う前記各記憶素子の間に埋め込まれた層間絶縁膜と、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に連続的に形成され、且つ、窒化ボロン膜からなる保護膜と、

前記層間絶縁膜中に形成されたコンタクトと、

を備える、

ことを特徴とする半導体記憶装置。

【請求項4】

前記保護膜の膜厚は、前記各記憶素子の側面において10nm以下であることを特徴とする請求項2又は3に記載の半導体記憶装置。

【請求項5】

前記記憶素子は、MTJ素子又は抵抗変化素子であることを特徴とする請求項1から4のいずれか1つに記載の半導体記憶装置。

【請求項6】

半導体基板の上面に複数の記憶素子を形成し、

前記各記憶素子の側面と、隣り合う前記各記憶素子の間の前記半導体基板の前記上面との上に、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜を連続的に堆積して、第1の保護膜を形成し、

前記第1の保護膜の上に、ボロン膜又は窒化ボロン膜を連続的に堆積して、第2の保護膜を形成し、

隣り合う前記各記憶素子の間に層間絶縁膜を埋め込み、

隣り合う前記各記憶素子の間の前記層間絶縁膜中にエッチングを用いてコンタクトホールを形成する、

ことを特徴とする半導体記憶装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−110275(P2013−110275A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−254158(P2011−254158)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]