Fターム[5F092BB81]の内容

Fターム[5F092BB81]の下位に属するFターム

SiO2 (201)

Fターム[5F092BB81]に分類される特許

1 - 20 / 271

磁気抵抗素子の製造方法

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

磁気記憶素子

【課題】書き込み電流を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層12と、記憶層12上に設けられた非磁性層13と、非磁性層13上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層14とを含む。記憶層12の面積は、参照層14の面積より大きく、記憶層12の端部の磁化は、記憶層12の中央部の磁化より小さい。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。保護膜は、絶縁体からなりフェンス層の側面に設けられている。フェンス層の上面および保護膜の上面は、側壁膜の上面よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

磁気センサ装置およびその製造方法

【課題】1つの基板に形成した複数の磁気抵抗素子部のピン磁性層を任意の方向に着磁させたとしても、着磁による熱拡散の影響を低減する。

【解決手段】基板10の一面11の上方に各磁気抵抗素子部50を形成する。次に、基板10のうち各磁気抵抗素子部50に対応する部分に溝13を形成して空間部14を形成する。この後、磁場の向きが第1の方向に設定された磁場中に、各磁気抵抗素子部50が形成された基板10を配置し、一方の磁気抵抗素子部50を局所的に加熱して磁場中アニールを行い、当該磁気抵抗素子部50のピン磁性層51の磁化の向きを第1の方向に着磁する。また、磁場の向きを第1の方向とは異なる第2の方向に設定した磁場中において、他方の磁気抵抗素子部50を局所的に加熱して磁場中アニールを行い、当該磁気抵抗素子部50のピン磁性層51の磁化の向きを第2の方向に着磁する。

(もっと読む)

磁気検出装置とその製造方法

【課題】本発明は、小型化に優れると共に高精度な電気抵抗の調整が可能である磁気検出装置とその製造方法を提供することを目的とする。

【解決手段】第一の短絡層41と第二の短絡層42とを、それぞれ第一の磁気抵抗効果素子層11と第一の抵抗素子層21とにのみ導通させ且つ一体に積層させて短絡することで、第一の磁気抵抗効果素子層11と第一の抵抗素子層21との電気抵抗を調整する。

(もっと読む)

磁気抵抗素子及びその製造方法

【課題】磁気抵抗素子の出力を低下させずに耐環境性の向上を図ること。

【解決手段】半導体に磁界を加えると抵抗が変化する磁気抵抗体10を備えている磁気抵抗素子で、磁気抵抗体10が、基板11上に設けられた薄膜状の半導体層12aからなる感磁部12と、感磁部12上に配置された複数の短絡電極13,13とを備え、半導体層12aの厚みが、0.4μm以上0.8μm以下である。半導体層12aの延在方向に対して垂直方向の半導体層の幅をW、複数の短絡電極間の一定間隔の距離をLとしたときに、距離Lと幅Wの比であるL/Wが、0.18以上0.22以下である。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の反射率に依存せず、アライメントマークの識別性を確保することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、シリコン基板24と、シリコン基板24上に少なくともNiCoパターン31とアルミ電極30とを含んで形成される回路部3と、シリコン基板24上に回路部3のNiCoパターン31と同工程において形成される低反射パターンとしてのNiCoパターン22と、NiCoパターン22上に形成され、回路部3のアルミ電極30と同工程において形成される高反射パターンとしてのアルミパターン20とを有する。

(もっと読む)

磁気センサ装置およびその製造方法

【課題】1つの基板に形成した複数の磁気抵抗素子部のピン磁性層を任意の方向に着磁させたとしても、磁気抵抗素子部の検出精度の低下を防止する。

【解決手段】基板10に各磁気抵抗素子部22に対応するヒータ部30をそれぞれ形成し、ヒータ部30の上方に各磁気抵抗素子部22を形成する。磁場の向きが基板10の一面13の面方向のうちの第1の方向に設定された磁場中において、一方の磁気抵抗素子部22に対応するヒータ部30を加熱して磁場中アニールを行い、当該磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きを第1の方向に着磁する。続いて、磁場の向きを第1の方向とは異なる第2の方向に設定した磁場中において、他方の磁気抵抗素子部22に対応するヒータ部30を加熱して磁場中アニールを行い、当該磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きを第2の方向に着磁する。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

半導体記憶装置

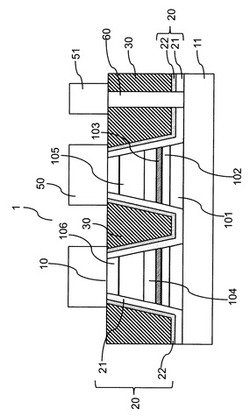

【課題】磁気抵抗効果素子間の磁気的な干渉作用を遮断し、安定した動作を可能にし、且つ、容易に製造することができる半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、半導体基板上にマトリックス状に配列した複数の磁気抵抗効果素子を有し、各磁気抵抗効果素子は、半導体基板上に形成された第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成された第2の磁性層とからなる積層構造を有し、隣り合う各磁気抵抗効果素子の間には、金属、又は、磁性体材料が分散された絶縁膜が埋め込まれている。

(もっと読む)

ハードバイアスのシード構造を有する磁気センサ

【課題】

ハードバイアスのシード構造を有する磁気センサを提供する。

【解決手段】

データ密度増加させるため縮小したギャップ間隔を提供する新規なハードバイアス構造を有する磁気センサ。本磁気センサは、磁気シールド上で形成される第1および第2の側面を備えるセンサ積層体を含む。薄い絶縁体層は、センサ積層体の側面上および最下部シールド上に形成される。Cu−Oを含む下地層は、絶縁体層上に形成され、ハードバイアス層は下地層上に形成される。下地層にCu−Oを使用することにより、下地層をより薄くすることができつつ、その上方に形成されるハードバイアス層中でも優れた磁気特性を維持することを可能にする。下地層の膜厚縮小により、ギャップ間隔(最上部および最下部磁気シールド間の間隔)が縮小され、そのことは次にデータ密度の増加を提供する。

(もっと読む)

記憶素子及びメモリ

【課題】書き込み電流を増大させることなく、熱安定性を改善することができるメモリを提供する。

【解決手段】情報を磁性体の磁化状態により保持する記憶層を有し、この記憶層に対して、中間層を介して磁化固定層が設けられ、中間層が絶縁体から成り、積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる記憶素子と、この記憶素子の積層方向に流す電流を供給する配線とを備え、記憶素子の上に隣接して積層された層に、記憶層と熱膨張係数の異なる、TiN,WN,TaN,Moのうちのいずれかの材料が用いられ、記憶層に歪が印加されているメモリを構成する。

(もっと読む)

磁気記憶装置の製造方法および磁気記憶装置

【課題】TMR素子間の特性のばらつきを低減でき、かつ製造歩留まりの高い不揮発性磁気メモリの製造方法およびその構造を提供する。

【解決手段】TMR素子を含む磁気記憶装置の製造方法が、配線層が設けられた層間絶縁膜の上に、絶縁膜を形成する工程と、絶縁膜に、配線層が露出するように開口部を形成する開口工程と、開口部を埋めるように、絶縁膜上に金属層を形成する金属層形成工程と、CMP法を用いて絶縁膜上の金属層を研磨除去し、開口部内に残った金属層を下部電極とするCMP工程と、下部電極上にTMR素子を形成する工程とを含む。

(もっと読む)

1 - 20 / 271

[ Back to top ]