Fターム[5F092CA03]の内容

Fターム[5F092CA03]に分類される特許

1 - 20 / 45

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

薄膜磁気センサ及びその製造方法

【課題】水分透過量が小さいSi系絶縁膜が回路表面に形成されており、Si系絶縁膜の密着性及び耐クラック性に優れた薄膜磁気センサ及びその製造方法を提供すること。

【解決手段】以下の工程を備えた薄膜磁気センサの製造方法及びこの方法により得られる薄膜磁気センサ。(1)基板表面に薄膜ヨーク、GMR膜、電極及び配線を備えた素子部を形成する素子部形成工程。(2)少なくとも電極の表面の全部又は一部を含む領域(薄膜ヨーク、GMR膜及び配線の表面を除く)にフォトレジスト膜を形成するフォトレジスト膜形成工程。(3)基板の表面にAl2O3膜を形成するAl2O3膜形成工程。(4)Al2O3膜の表面に、Cat−CVD法を用いてSi系絶縁膜を形成するSi系絶縁膜形成工程。(5)フォトレジスト膜、並びに、フォトレジスト膜の上に形成された余分なAl2O3膜及びSi系絶縁膜を除去する除去工程。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】安定して動作可能な磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】実施形態の磁気抵抗効果は、下部電極と、第1の磁性層と、第1の金属層と、第1の界面磁性層と、非磁性層と、第2の界面磁性層と、第2の金属層と、第2の磁性層と、上部電極層と、を持つ。前記第1の磁性層は、前記下部電極上に設けられて第1の金属原子を含む。前記第1の金属層は、前記第1の磁性層上に設けられて前記第1の金属原子を含む。前記第1の界面磁性層は、前記第1の金属層上に設けられる。前記非磁性層は、前記第1の界面磁性層上に設けられる。前記第2の界面磁性層は、前記非磁性層上に設けられる。前記第2の金属層は、前記第2の界面磁性層上に設けられ、第2の金属原子を含む。前記第2の磁性層は、前記第2の金属層上に設けられ、前記第2の金属原子を含む。前記上部電極層は、前記第2の磁性層上に設けられる。前記第1の界面磁性層は、前記非磁性層側と反対側の界面にアモルファス金属層を含む。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】安定して動作可能な磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】実施形態の磁気抵抗効果素子は、下部電極と、第1の磁性層と、第1の界面磁性層と、第2の界面磁性層と、第2の磁性層と、上部電極とを持つ。前記第1の磁性層は前記下部電極上に設けられる。前記第1の界面磁性層は、前記第1の磁性層上に設けられる。前記非磁性層は、前記第1の界面磁性層上に設けられる。前記第2の磁性層は前記第2の界面磁性層上に設けられる。前記上部電極は、前記第2の磁性層上に設けられる。前記第1および第2の磁性層は、それぞれ磁化記憶層および磁化参照層の一方および他方である。前記上部電極は、貴金属と遷移元素もしくは希土類元素の合金層もしくは混合物層、または導電性酸化物層を含む。

(もっと読む)

半導体記憶装置

【課題】安定した特性の磁気抵抗効果素子を有する半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、複数の磁気抵抗効果素子を有し、この各磁気抵抗効果素子は、半導体基板上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第2の磁性層と、からなる積層構造を有し、保護膜を介して各磁気抵抗効果素子の側壁を覆うように設けられ、且つ、磁気抵抗効果素子に対して、磁化容易軸に沿った方向に引張応力を与える側壁膜を備え、側壁膜のうちの第1の磁性層を覆う部分は、側壁膜のうちの第2の磁性層を覆う部分と比べて厚い。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

半導体記憶装置

【課題】 熱負荷によるTMR比の減少を抑制できる磁気抵抗効果を利用した半導体記憶装置を提供すること。

【解決手段】 実施形態の磁気抵抗素子は、非磁性元素を含む第1の垂直磁化磁性膜116と、第1の垂直磁化磁性膜上に設けられた絶縁膜119と、第1の垂直磁化磁性膜と絶縁膜との間に設けられた第1の中間磁性膜118と、絶縁膜上に設けられ、非磁性元素を含む第2の垂直磁化磁性膜123と、絶縁膜と第2の垂直磁化磁性膜との間に設けられた第2の中間磁性膜120と、第1の垂直磁化磁性膜と第1の中間磁性膜との間、および、第2の中間磁性膜と第2の垂直磁化磁性膜との間の少なくとも一方に設けられ、非磁性元素の拡散に対してバリア性を有する金属窒化物または金属炭化物で形成された拡散防止膜117,121を含む。

(もっと読む)

磁気デバイスおよびその製造方法

【課題】複数のトンネル接合素子の間隔を短縮すること。

【解決手段】上面に凹部26が形成された下地層24と、前記凹部の内面と前記凹部の両側の下地層上とに形成された下部電極28と、前記凹部の両側の前記下部電極上に形成され、トンネルバリア層と前記トンネルバリア層を上下に挟む磁化固定層および磁化自由層とを含む磁気トンネル接合層30と、前記磁気トンネル接合層上に形成され、前記凹部の上方において電気的に分離された複数の上部電極40と、を具備する磁気デバイス。

(もっと読む)

トンネル磁気抵抗素子

【課題】マグネタイト(Fe3O4)膜を一方の電極とし、マグネタイト本来のスピン依存電気伝導特性をより反映した、室温で20%以上の負のMR比を示すTMR素子を提供すること。

【解決手段】マグネタイト電極と、該マグネタイト電極上に成膜された酸化マグネシウム層と該酸化マグネシウム層上に成膜された2nm以下の厚さの酸化アルミニウム非晶質層とからなる障壁層と、を備えるトンネル磁気抵抗素子である。サファイア基板(00.1)面上に、マグネタイトを[111]方向にエピタキシャル成膜してマグネタイト電極を形成し、該電極上に酸化マグネシウム層を[111]方向にエピタキシャル成膜し、その上に酸化アルミニウム非晶質層を成膜して障壁層を形成する。

(もっと読む)

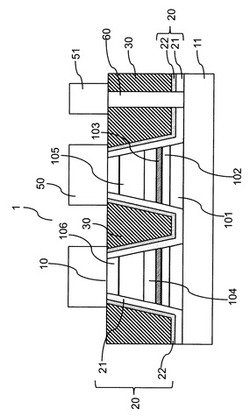

トンネル磁気抵抗効果素子およびその製造方法ならびに製造装置

【課題】基板上に、下部電極層、ピンド層、トンネルバリア層、フリー層、上部電極層を順次成膜してなるトンネル磁気抵抗効果素子において、極力小さい膜厚で良好な被覆性を確保できるトンネルバリア層を実現する。

【解決手段】基板10上に、下部電極層20、ピンド層30、トンネルバリア層40、フリー層50、上部電極層60が順次積層されてなるトンネル磁気抵抗効果素子1において、トンネルバリア層40は、原子層成長法により成膜されたアルミナなどからなり、膜厚を薄いものとしても、下地のピンド層30の表面に存在する凹凸の被覆性を高め、トンネルバリア層40の膜厚ばらつきを小さくできる。

(もっと読む)

トンネル接合素子の製造方法

【課題】大気に曝した半導体層の表面上にトンネル絶縁膜を形成した場合であっても、半導体層にスピン偏極率の大きなキャリアを注入できるトンネル接合素子を提供すること。

【解決手段】半導体層10の表面を大気に曝す工程と、前記半導体層10の前記表面を還元性ガスに曝す工程と、前記表面を還元性ガスに曝す工程の後前記半導体層10の前記表面を大気に曝すことなく、前記半導体層10の前記表面上にトンネル絶縁膜12を形成する工程と、前記トンネル絶縁膜12上に強磁性体層14を形成する工程と、を含むトンネル接合素子の製造方法。

(もっと読む)

磁気トンネル接合素子及びその製造方法

【課題】 イオンミリングを適用することなく、書込み電流の増加やリーク電流の増加を抑制することができる技術が望まれている。

【解決手段】 基板の上に磁化固定層が形成されている。磁化固定層の上に絶縁膜が形成され、絶縁膜を貫通する溝部が形成されている。溝部の底面にトンネル絶縁膜が形成されている。溝部の底面の上に、前記トンネル絶縁膜を介して第1の磁化自由層が形成されている。絶縁膜の上に、第1の磁化自由層と同一の磁性材料で形成された第2の磁化自由層が配置されている。溝部の側面に、第1の磁化自由層から第2の磁化自由層まで到達し、第1の磁化自由層を形成する磁性材料の酸化物で形成された非磁性膜が配置されている。第1の磁化自由層、非磁性膜、及び第2の磁化自由層の上に、第1の磁化自由層及び第2の磁化自由層に電気的に接続された上部電極が配置されている。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】磁壁移動型の磁気抵抗素子の微細化を実現する。

【解決手段】基板上に位置する第1の絶縁層24と、第1の絶縁層の24内部に位置し、互いに電気的に絶縁した一対の第1の磁化固定層20a、20bと、第1の絶縁層24上に位置し、平面視で一対の第1の磁化固定層20a、20bいずれとも重なり、かつ、一対の第1の磁化固定層20a、20bいずれとも電気的に接続している磁化自由層31と、磁化自由層31上に位置する第2の絶縁層33と、第2の絶縁層33に形成され、平面視で磁化自由層31と重なる孔と、当該孔の底面および側面に沿って形成された非磁性層41と、非磁性層41形成後の孔内に埋め込まれた第2の磁化固定層42と、を有し、第2の磁化固定層42は、平面視で一対の第1の磁化固定層20a、20bいずれとも重ならず、かつ、平面視で一対の第1の磁化固定層20a、20bの間に位置する半導体装置。

(もっと読む)

磁気抵抗素子の製造方法

【課題】磁気特性の低下の抑制を図る。

【解決手段】磁気抵抗素子の製造方法は、磁化の方向が不変の固定層4、コバルトまたは鉄を含み、磁化の方向が可変の自由層6、および前記固定層と前記自由層との間に挟まれる非磁性層5で構成される積層体を形成し、前記積層体上に、ハードマスク11を形成し、前記ハードマスクをマスクとして塩素を含むガスで前記積層体をエッチングし、エッチングされた前記固定層および前記自由層の側面に、ボロンと窒素とを含む絶縁膜14を形成する。

(もっと読む)

磁気抵抗効果素子の製造方法

【課題】形成された膜のステップカバレッジを大きくすることが可能であり、かつ低温領域で成膜することが可能な磁気抵抗効果素子の製造方法を提供すること。

【解決手段】本発明の一実施形態では、プラズマ源と成膜室を隔壁板により隔離したプラズマCVD装置により多層磁性層上に絶縁性の保護層を形成する。本方法によれば、磁気特性の劣化をもたらすことなく保護層を成膜でき、かつ、150℃未満の低温成膜も可能である。これにより、レジストを残留させたまま保護層の成膜が可能であり、多層構造の磁気抵抗効果素子の製造において工数低減も可能である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

ゲルマニウム・ホール・プレートを有する集積ホール効果素子

集積回路及びその集積回路を製造する方法は、ゲルマニウム・ホール・プレートを有するホール効果素子を提供する。このゲルマニウム・ホール・プレートは、シリコンと比較して増大した電子移動度を提供し、それ故、より高感度なホール効果素子を提供する。 (もっと読む)

磁気抵抗デバイス

【課題】大きな出力信号強度を得られるEMRデバイスに、既存のスライダ形成技術を利用して磁気ヘッドスライダが形成できるような、デバイス構造とデバイス製造方法を提供すること

【解決手段】磁気抵抗デバイスは、基板(4;64)と、第一方向(14)に伸びた細長半導体チャネル(11)素子と、チャネルへの接点の組(27)を提供する少なくとも2つの導電性リード(26)とを含んでいる。デバイスは、チャネルと接続したオプションの半導体シャント(8)を含んでいる。オプションのシャント、チャネル及び接点の組は、第一方向及び基板の表面に対して垂直な第二方向(15)に向かって、基板に対して積重ねられる。デバイスは、チャネルに沿って伸びる側面(30)を有している。デバイスは、側面に対して一般的に垂直な方向の磁場(31)に対して反応する。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】短絡や電流リークを生じさせること無く、しかも、MTJ構造にダメージを生じさせること無く、不揮発性メモリ素子におけるMTJ構造のパターニングを行い得る不揮発性メモリ素子の製造方法を提供する。

【解決手段】第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53が、順次、積層された積層構造体50を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法は、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53を順次形成し、次いで、第2磁性材料層53上にマスク層63を形成した後、マスク層63で覆われていない第2磁性材料層53の部分53’を酸化し、次いで、酸化された第2磁性材料層53の部分53’を還元する工程を備えている。

(もっと読む)

絶縁膜の成膜方法及びその成膜装置

【課題】 量産に適した、コンタミの少ない、組成制御された、ち密で、欠陥、粒界の極めて少ない、深さ方向に構造制御された、良好な絶縁特性を持つ絶縁膜の提供。

【解決手段】 O、N及びFから選ばれた少なくとも1種を含む気体状分子を該基板表面に供給し、吸着させた後排気する第1の工程の後に、Al、Si、Ta、又はTiを含む気体状分子を基板表面に供給し、吸着させた後排気する第2の工程を行い、その後にArを導入した後排気する第3の工程を行い、前記第1〜第3の工程を1つのサイクルとして、このサイクルを複数回行うことを特徴とする。

(もっと読む)

1 - 20 / 45

[ Back to top ]