Fターム[5F058BD18]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層がその他の無機物層 (225)

Fターム[5F058BD18]に分類される特許

1 - 20 / 225

半導体装置及びその製造方法

【課題】所望の領域に容易に第1の膜を形成して半導体装置の不良を低減する。また、スループットが向上して、製造コストの低減を図る。

【解決手段】半導体装置の製造方法では、半導体基板の第1及び第2の領域上に第1の膜を形成した後、第1の膜上にフォトレジストパターンを形成する。フォトレジストパターンをマスクに用いた第1の膜のエッチングにより、第2の領域上の第1の膜を除去すると共に第2の領域上を覆うように被覆膜を形成する。半導体基板に熱処理を行うことにより、被覆膜を除去すると共にフォトレジストパターンに焼き締め処理を行う。この後、フォトレジストパターンを除去する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

成膜装置及びその運用方法

【課題】処理容器内の処理空間に接する石英製の部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制することができる成膜装置の運用方法を提供する。

【解決手段】石英製の処理容器8内で保持手段22に保持された複数の被処理体Wの表面にカーボン膜を成膜する成膜工程を行うようにした成膜装置の運用方法において、処理容器内の処理空間に接する石英製の部材の表面にカーボン膜の密着性を向上させる密着膜70を形成する密着膜形成工程を行うようにする。これにより、処理容器内の処理空間に接する石英製の部材の表面に対するカーボン膜の密着性を向上させてパーティクルの発生を抑制する。

(もっと読む)

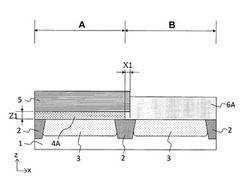

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

炭素薄膜成膜方法

【課題】水素フリーで緻密で硬質なダイヤモンドライクカーボン膜を容易に形成することができる炭素薄膜成膜法を提供する。

【解決手段】この炭素被膜成膜方法は、マグネトロンスパッタ法により試料基板電極上に配置された試料基板表面に炭素被膜を堆積させる炭素被膜成膜装置を用い、炭素ターゲット基板電極と試料電極に対し、下記1〜4の条件でそれぞれ電圧を印加させることを特徴とする。

1.ターゲット基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が40%以下であること。

2.ターゲット基板電極に印加するパルス電圧のパルス時間が20μs〜200μsであること。

3.試料基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が50%以下であること。

4.試料基板電極に印加する負パルス電圧の大きさが−20V〜−200Vであること。

(もっと読む)

大気圧プラズマ処理装置

【課題】被処理体以外の部位への成膜を抑制した大気圧プラズマ処理装置を提供する。

【解決手段】プラズマ処理装置は、誘電体内にアンテナとアースが形成された面放電型の誘電体バリア放電方式のプラズマ源において、被処理体を前記プラズマ源に略接触させ、被処理体に対してプラズマ源を設置した面とは反対の面にプラズマを生成するようにした。

(もっと読む)

吸収係数および応力を低減しつつ炭素膜のエッチング選択性を改善する方法

【課題】透明性が高く、エッチング選択性が高く、アッシング可能なハードマスク(AHM)を提供する。

【解決手段】プラズマ化学気相成長チャンバ内に基板を配置する段階を備える成膜方法を開示する。炭素系の第1のアッシング可能ハードマスク(AHM)層10を基板上に成膜する。第1のAHM層の成膜時に、シリコン、シラン、ホウ素、窒素、ゲルマニウム、炭素、アンモニア、および、二酸化炭素から成る群から選択される少なくとも1つのドーパントでドープを行う。少なくとも1つのドーパントの原子濃度は、第1のAHM層の5%以上である。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法及びハードマスクの形成方法

【課題】アモルファスカーボン膜のパターン寸法ばらつきが低減した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にアモルファスカーボン膜を成膜する工程と、アモルファスカーボン膜のパターンを形成する工程と、アモルファスカーボン膜をマスクにして下地膜をエッチングする工程を有する。アモルファスカーボン膜は、アモルファスカーボン膜の表面から下地膜に接する面に向かってその厚み方向を進むにつれて、アモルファスカーボン膜の膜密度を小さくする。

(もっと読む)

大面積CVDダイヤモンド単結晶の製造方法、及びこれによって得られた大面積CVDダイヤモンド単結晶

【課題】凹部のない大面積で高品質なCVDダイヤモンド単結晶及びこれを実現する製造方法の提供。

【解決手段】主面が{100}であるダイヤモンド単結晶基板の{100}側面同士を近接させて4枚以上配置し、該配置した単結晶基板の主面にダイヤモンドを気相合成により成長させた後、該単結晶基板を除去して1枚の大面積CVDダイヤモンド単結晶を製造する方法であって、前記ダイヤモンド単結晶基板の配置が、近接する任意の4枚の単結晶基板の、隣接する2枚の単結晶基板A1とA2とからなる単位Aと、他の2枚の単結晶基板B1とB2とからなる単位Bとにおいて、A及びBが対向する側の面がそれぞれ同一平面上にあり、かつA1とA2が対向する側面間の間隔の真中の面と、B1とB2が対向する側面間の間隔の真中の面とが、単位Aと単位Bが対向する面の方向にずれている配置であることを特徴とする大面積CVDダイヤモンド単結晶を製造する方法。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の多層配線において配線間隔を低減させても所定の低比誘電率を維持できるとともに、電気的特性の劣化などを抑制できる多孔性の層間絶縁膜の形成方法を提供する。

【解決手段】 半導体基板1上に形成される配線構造を構成し、空孔を有する多孔性絶縁膜13を得るための母体となる母体絶縁膜を気相成長法を用いて堆積する。この際、多孔性絶縁膜13の比誘電率、配線20間の間隔や絶縁耐圧のような、配線構造を決める因子に要求される設計値に応じて、多孔性絶縁膜13の分子骨格形成材料の流量に対する多孔性絶縁膜13の空孔形成材料の流量の比の、少なくとも範囲をまず決定する。この後、決定した流量比の範囲で母体絶縁膜を堆積し、この母体絶縁膜に熱や紫外線などのエネルギーを与えて空孔を有する多孔性絶縁膜13にする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CFx膜を層間絶縁膜として有する多層配線構造の半導体装置において、低誘電率であるCFx膜の利点を生かすことができ、かつCMP処理による特性の劣化を防止することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、CFx膜を成膜する工程(a)と、CFx膜に所定パターンの凹部を形成する工程(b)と、凹部を埋めかつCFx膜上にわたって配線層を設ける工程(c)と、凹部内以外の前記CFx膜上の余剰の配線層をCMP(化学機械研磨)によって除去してCFx膜の表面を露出させる工程(d)と、を有し、工程(b)の前または後において、CFx膜の表面を窒化する工程(e)を備える。

(もっと読む)

アモルファスカーボン膜の形成方法および形成装置

【課題】カバレッジ性能、及び、表面ラフネスの良好なアモルファスカーボン膜の形成方法および形成装置を提供する。

【解決手段】制御部100は、昇温用ヒータ16を制御して、複数枚の半導体ウエハWが収容された反応管2内を所定の温度に加熱する。次に、制御部100は、MFC制御部を制御して、加熱された反応管2内にアミノ系シランガスを供給する。そして、制御部100は、昇温用ヒータ16を制御して、反応管2内を所定の温度に加熱し、MFC制御部を制御して、加熱された反応管2内に処理ガス導入管17からエチレンを供給することにより、半導体ウエハWにアモルファスカーボン膜を形成する。

(もっと読む)

選択成膜方法、成膜装置、及び構造体

【課題】炭素を含む膜を選択成長させること。

【解決手段】主面上にトレンチとポストが形成された基板13上に、選択的に炭素を有した膜を、プラズマCVD法により堆積する選択成膜方法である。基板を設置する反応室11において、第1電力により、膜の原料ガスのプラズマを生成し、反応室と連通し、区画された補助空間21において、第2電力により、基板に対してエッチング性を有するガスのプラズマを生成して、反応室に、イオン及びラジカルを供給する。反応室において、基板の主面に垂直方向に電界を発生させるバイアス電圧を制御して、基板のポストの上面、トレンチの側面及び底面に至るイオン量を制御する。第1電力、第2電力、バイアス電圧を制御することにより、基板の前記ポストの上面、トレンチの側面及び底面のうちの選択された1つの面、又は、2つの面に対して、膜を成膜する。

(もっと読む)

成膜方法及び成膜装置

【課題】比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくでき、もってクリーニング時の膜厚の制御性を向上させることができる成膜方法を提供する。

【解決手段】被処理体Wが収容されて真空引き可能になされた処理容器4内に、シラン系ガスと窒化ガスと炭化水素ガスとを供給して前記被処理体の表面にSiCN膜よりなる薄膜を形成する成膜方法において、前記シラン系ガスと前記窒化ガスと前記炭化水素ガスとをそれぞれ一定の供給期間でパルス状に供給する供給工程と供給を停止する停止工程とよりなる1サイクルを複数回繰り返し実行してプラズマを用いることなく前記薄膜を形成する。これにより、比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくでき、もってクリーニング時の膜厚の制御性を向上させる。

(もっと読む)

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

1 - 20 / 225

[ Back to top ]