Fターム[5F092CA20]の内容

Fターム[5F092CA20]に分類される特許

1 - 20 / 101

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

シザーズ構造を有する磁気抵抗センサの磁気バイアス構造

【課題】 シザーズ構造を有する磁気抵抗センサの磁気バイアス構造を提供する。

【解決手段】 磁気バイアス付与の堅牢性を向上させる新規のハードバイアス構造を有するシザーズ型磁気センサ。当該センサは、電気絶縁障壁層または導電スペーサ層等の非磁性層により分離された第1の磁気層および第2の磁気層を含むセンサスタックを含む。第1の磁気層および第2の磁気層は、逆平行に結合されるが、磁気バイアス構造により、エアベアリング面に対して平行でも垂直でもない方向に傾けられた磁化方向を有する。磁気バイアス構造は、センサスタックの後縁から延在し、センサスタックの第1の側面および第2の側面に整列した第1の側面および第2の側面を有するネック部を含む。バイアス構造はまた、ネック部から後方に延在する先細または楔形部を含む。

(もっと読む)

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

磁気メモリ

【課題】磁気記録層の強磁性体膜が強い垂直磁気異方性を有する磁気メモリを提供する。

【解決手段】磁気メモリは、強磁性体の下地層51と、下地層51上にの第1非磁性52と、第1非磁性52上の垂直磁気異方性を有する強磁性体のデータ記憶層53と、第2非磁性層20を介してデータ記憶層53に接続された参照層30と、下地層51の下側に接した第1、第2磁化固定層41a、41bとを具備する。データ記憶層53は、反転可能な磁化を有し参照層30とオーバーラップする磁化自由領域13と、磁化自由領域13の端に接続され、第1磁化固定層41aに+z方向に磁化固定された第1磁化固定領域11aと、磁化自由領域13の他の端に接続され、第2磁化固定層41bに−z方向に磁化固定された第2磁化固定領域11bとを備える。磁化自由領域13下の第1非磁性52は、第1、第2磁化固定領域11a、11b下の第1非磁性52よりも厚い。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

耐食性スペーサ層を備え、より高い信号雑音比を有するCPP−GMRセンサ

【課題】耐食性スペーサ層を備え、より高い信号雑音比を有するCPP−GMRセンサを提供する。

【解決手段】膜面垂直通電(CPP)型巨大磁気抵抗効果(GMR)センサのスペーサ層を形成する材料の電気抵抗と耐食性を増大させるための方法と装置。スペーサ層および、それゆえCPP−GMRセンサの抵抗を大きくすることにより、より大きな電圧をセンサにかけることができ、信号対雑音比をより高くすることができる。スペーサ層の耐食性を高めることにより、製造中にスペーサ層を腐食性材料に曝す影響が最小限となる。たとえば、スズを銀に添加して金属合金スペーサ層を形成すれば、このスペーサ層の耐食性とCPP−GMRセンサの電気抵抗は、銀のみからなるスペーサ層の場合より増大する。Ag−Sn合金により、より大きな電流がセンサを流れ、これによって信号対雑音比が増大する。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

磁気抵抗センサ、装置および方法

【課題】 磁気抵抗読取センサを提供する。

【解決手段】 センサは、浮上面に沿って上部電極と下部電極との間に配置された磁気反応性スタックである。センサ内の電流がスタックと少なくとも1つの電極との間の第1の多層絶縁構造によって浮上面近くの領域に制限されることで、読取機の感度が向上する。

(もっと読む)

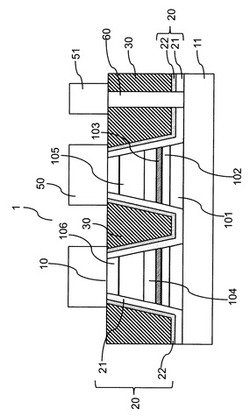

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

多層膜の製造方法

【課題】多層膜内の特定層だけに格子振動を与えてその多層膜の特性を向上させる。

【解決手段】実施形態に係わる多層膜の製造方法は、第1の層(CoFeB)を形成する工程と、第1の層(CoFeB)上に第2の層(MgO)を形成する工程と、第2の層(MgO)の表面に対してGCIB照射を行うことにより、第2の層(MgO)の結晶情報を第1の層(CoFeB)に転写する工程とを備える。

(もっと読む)

磁気メモリ及び磁気メモリ装置

【課題】 本発明の実施形態によれば、低電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供することができる。

【解決手段】 第1の磁性層と、第2の磁性層と、前記第1の磁性層と前記第2の磁性層とを結ぶ第1の方向において前記第1の磁性層と前記第2の磁性層との間に設けられた第3の磁性層と、前記第1の磁性層と前記第3の磁性層との間に設けられた第1の中間層と、前記第2の磁性層と前記第3の磁性層との間に設けられた第2の中間層と、前記第1の方向に直交する第2の方向において前記第3の磁性層に設けられた絶縁膜と、前記絶縁膜の前記第3の磁性層が設けられた側とは反対側に設けられた電極と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ロジック混載MRAMにおいて、LSIの多層配線形成プロセスがMRAMの特性変動を引き起こす不都合、また、MRAMの形成プロセスが多層配線の特性変動を引き起こす不都合を軽減すること。

【解決手段】多層配線層に含まれる配線層Aの中に、配線層Bに形成された第1の配線104bに接し、互いに絶縁している少なくとも2つの第1の磁化固定層50a及び50bと、2つの第1の磁化固定層50a及び50bと平面視で重なり、かつ、第1の磁化固定層50a及び50bと接続している磁化自由層10と、磁化自由層10の上に位置する非磁性層40と、非磁性層40の上に位置する第2の磁化固定層104aと、を有するMRAMが形成されている半導体装置。

(もっと読む)

半導体記憶装置

【課題】 熱負荷によるTMR比の減少を抑制できる磁気抵抗効果を利用した半導体記憶装置を提供すること。

【解決手段】 実施形態の磁気抵抗素子は、非磁性元素を含む第1の垂直磁化磁性膜116と、第1の垂直磁化磁性膜上に設けられた絶縁膜119と、第1の垂直磁化磁性膜と絶縁膜との間に設けられた第1の中間磁性膜118と、絶縁膜上に設けられ、非磁性元素を含む第2の垂直磁化磁性膜123と、絶縁膜と第2の垂直磁化磁性膜との間に設けられた第2の中間磁性膜120と、第1の垂直磁化磁性膜と第1の中間磁性膜との間、および、第2の中間磁性膜と第2の垂直磁化磁性膜との間の少なくとも一方に設けられ、非磁性元素の拡散に対してバリア性を有する金属窒化物または金属炭化物で形成された拡散防止膜117,121を含む。

(もっと読む)

磁気トンネル接合素子及び磁気ランダムアクセスメモリ

【課題】 書込み電流の低減のみならず、大きなMR比を有するMTJ素子の開発が望まれている。

【解決手段】 磁気トンネル接合素子が、磁化自由層と、磁化固定層と、磁化自由層と磁化固定層との間に配置されたトンネルバリア層とを有する。磁化自由層は、垂直磁化自由層、垂直磁化自由層とトンネルバリア層との間に配置された面内磁化自由層、及び垂直磁化自由層と面内磁化自由層との間に配置された非磁性中間層とを含む。垂直磁化自由層の磁化容易方向は膜面に対して垂直であり、面内磁化自由層の磁化容易方向は膜面に平行であり、垂直磁化自由層の磁化は、非磁性中間層を介して面内磁化自由層と交換結合することによって、面内方向を向いている。

(もっと読む)

スピン伝導型磁気センサ

【課題】 スピン伝導特性を改善可能なスピン伝導型磁気センサを提供することを目的とする。

【解決手段】 この磁気センサは、磁気シールド層10Bを有するベース基板10と、ベース基板10の磁気シールド層10B上の絶縁膜4を介して貼り付けられた単一ドメインからなる半導体の結晶層3と、半導体の結晶層3における絶縁膜4とは反対側の表面上に、第1トンネル障壁層を介して形成された第1強磁性層1と、半導体の結晶層3における絶縁膜4とは反対側の表面上に、第1強磁性層1から離間し、第2トンネル障壁層を介して形成された第2強磁性層2とを備えている。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気メモリにおいて、安定的且つ容易に磁壁を導入可能な構造とする。

【解決手段】磁気メモリは、磁気記録層10と、非磁性層11を介して磁気記録層10に接続された参照層12と、磁気記録層10より下方に設置された第1、2磁化固定層19、20とを具備する。磁気記録層10及び参照層11は垂直磁気異方性を有する。磁気記録層10は、反転可能な磁化を有し参照層11と重なる磁化反転領域2と、磁化反転領域2の第1境界に接続され、磁化の向きが第1方向に固定された第1磁化固定領域1と、磁化反転領域2の第2境界に接続され、磁化の向きが第1方向と反平行な第2方向に固定された第2磁化固定領域3とを備える。第1、2磁化固定層19、20は、第1、2磁化固定領域1、3の磁化を固定する。第2磁化固定層20が、第1磁化固定層19と比較して保磁力が低い。

(もっと読む)

磁気トンネル接合素子及び磁気ランダムアクセスメモリ

【課題】 GMR素子では、十分大きなMR比を得ることが困難である。大きなMR比を実現することが可能なMTJ素子において、反転電流を低減させることが望まれている。

【解決手段】 下部電極の上に、磁化容易方向が厚さ方向を向く垂直磁気異方性膜が形成されている。垂直磁気異方性膜の上に、非磁性材料で形成されたスペーサ層が配置されている。スペーサ層の上に、アモルファスの導電材料からなる下地層が配置されている。下地層の上に、磁化容易方向が面内方向を向く磁化自由層が配置されている。磁化自由層の上にトンネルバリア層が配置されている。トンネルバリア層の上に、磁化方向が面内方向に固定された磁化固定層が配置されている。スペーサ層は、垂直磁気異方性膜と磁化自由層との間に交換相互作用が働かない厚さであり、かつスピン緩和長よりも薄い。

(もっと読む)

1 - 20 / 101

[ Back to top ]