Fターム[4M119JJ12]の内容

MRAM・スピンメモリ技術 (17,699) | 製造方法 (929) | 加工方法 (452) | ドライエッチング (100)

Fターム[4M119JJ12]に分類される特許

1 - 20 / 100

プラズマ処理方法

磁気抵抗素子の製造方法

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

金属膜のドライエッチング方法

【課題】ハロゲンガスを用いることなく、かつ、ホールやトレンチの側壁形状をより垂直に近付けることのできる金属膜のドライエッチング方法を提供する。

【解決手段】白金を含む金属膜を、マスク層を介してドライエッチングする金属膜のドライエッチング方法であって、水素ガスと二酸化炭素ガスとメタンガスと希ガスとを含む混合ガスからなるエッチングガスのプラズマを発生させて、金属膜をドライエッチングする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。保護膜は、絶縁体からなりフェンス層の側面に設けられている。フェンス層の上面および保護膜の上面は、側壁膜の上面よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

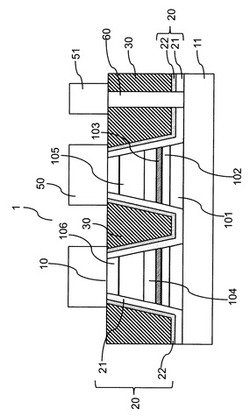

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

プラズマエッチング方法

【課題】CO含有プラズマの条件によらず、安定してクリーニングプラズマを生成する方法を提供する。

【解決手段】被エッチングウェハ802上に形成された磁性膜を、真空容器801内に導入されたCとOの元素を含むCO含有ガスにソース電力を印加することでCO含有ガスをプラズマ化し、生成したCO含有プラズマを用い加工する際に、該CO含有プラズマにて被エッチングウェハ802上に形成された磁性膜に所定の加工を施した後、ソース電力806を印加したまま、クリーニングガスを導入し、その後CO含有ガスの導入を停止することで、所定のクリーニングガスを用いたクリーニングプラズマを生成する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

エッチング装置及び半導体装置の製造方法

【課題】難エッチング材料を、高速、高精度及び低ダメージでエッチングする。

【解決手段】実施形態に係わるエッチング装置は、上面側に披処理基板19が搭載されるステージ11と、ステージ11の上面側を覆うチャンバー12と、ステージ11の下面側に付加され、開口部を有する下部電極13aと、チャンバー12内にエッチングガスを供給するガス供給部14と、下部電極13aに高周波を印加することにより、チャンバー12内のエッチングガスをプラズマ化する高周波電源部17と、下部電極13aの開口部を介して被処理基板19にマイクロ波を印加することにより、披処理基板19の温度を最適範囲内に設定するマイクロ波発生部15と、ガス供給部14、高周波電源部17及びマイクロ波発生部15を制御する制御部18とを備える。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】書き込み電流を低減させたまま、リテンション、特に固定磁化層の大きなリテンションを十分に確保することができ、熱的に安定な動作を可能とする信頼性の高い磁気抵抗素子を実現する。

【解決手段】MTJ10は、下部磁性層1と上部磁性層3とでトンネルバリア層2を挟持し、上部磁性層3上にキャップ層4が形成されてなり、下部磁性層1は、トンネルバリア層2と接するCoFeBからなる第1自由層1aと、第1自由層1aに接するTaからなる挿入層1bと、挿入層1bに接するRuからなるスペーサ層1cと、スペーサ層1cに接するCoPtからなる第2自由層1dとを有して構成される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】トレンチを均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、第1の材料からなる第1部分及び前記第1の材料とは異なる第2の材料からなる第2部分を含む被加工基材上に、前記第1部分の直上域に配置され第3の材料からなる第3部分及び前記第2部分の直上域に配置され前記第3の材料とは異なる第4の材料からなる第4部分を含み、前記第3部分及び前記第4部分の双方に開口部が形成されたマスク膜を形成する工程と、前記マスク膜をマスクとして、前記第4の材料のエッチングレートが前記第3の材料のエッチングレートよりも高く、前記第1の材料のエッチングレートが前記第2の材料のエッチングレートよりも高くなるような条件でエッチングを施すことにより、前記第1部分及び前記第2部分をそれぞれ選択的に除去する工程と、を備える。

(もっと読む)

垂直磁化磁気抵抗効果素子及び磁気メモリ

【課題】垂直磁気異方性を有する強磁性材料を用いて作製した磁気抵抗効果素子において、ビット情報に対応する磁化の平行状態及び反平行状態の熱安定性が不均衡になり、保存している情報により記録保持時間が異なる状態を改善する。

【解決手段】磁気抵抗効果素子を構成する参照層106と記録層107の面積を異ならせることにより、保存している情報に応じた記録保持時間の差を補正する。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】高い熱揺らぎ耐性を確保しつつ、スイッチング電流を低減するも、記憶保持特性を向上させ、更なる高速動作化及び高集積化を可能する信頼性の高い磁気抵抗素子及び磁気記憶装置を提供する。

【解決手段】反強磁性層51及び積層フェリー固定層50と、トンネルバリア層2と、非磁性層4を間に挟持した第1の磁性層3と第2の磁性層5とを有する積層磁化自由層11とを有してMTJ10が構成されており、MTJ10は、その周縁において、当該MTJ10の面内磁化容易軸の方向と垂直となる方向に一対の溝10a,10bが形成されている。

(もっと読む)

磁気記憶装置の製造方法および磁気記憶装置

【課題】TMR素子間の特性のばらつきを低減でき、かつ製造歩留まりの高い不揮発性磁気メモリの製造方法およびその構造を提供する。

【解決手段】TMR素子を含む磁気記憶装置の製造方法が、配線層が設けられた層間絶縁膜の上に、絶縁膜を形成する工程と、絶縁膜に、配線層が露出するように開口部を形成する開口工程と、開口部を埋めるように、絶縁膜上に金属層を形成する金属層形成工程と、CMP法を用いて絶縁膜上の金属層を研磨除去し、開口部内に残った金属層を下部電極とするCMP工程と、下部電極上にTMR素子を形成する工程とを含む。

(もっと読む)

磁気抵抗素子の製造方法及び製造装置

【課題】エッチングに用いられるハロゲン系成分による素子の腐食を防止することが可能な磁気抵抗素子の製造装置及び製造方法を提供すること

【解決手段】本発明の磁気抵抗素子10の製造方法は、基板上に強磁性材料からなる第1の強磁性層13を形成する。酸化マグネシウムからなる絶縁層14は、第1の強磁性層13上に形成される。Fe及びCoの少なくとも一方を含有する第2の強磁性層15は、絶縁層14上に形成される。ハロゲン系元素を含むプラズマによるエッチングは、基板11上に第1の強磁性層13、絶縁層14及び第2の強磁性層15が積層された積層体に対して施される。積層体は、H2Oを含むプラズマであるH2Oプラズマに曝露される。

(もっと読む)

1 - 20 / 100

[ Back to top ]