Fターム[4M119JJ15]の内容

MRAM・スピンメモリ技術 (17,699) | 製造方法 (929) | 加工方法 (452) | CMP、平坦化技術 (230)

Fターム[4M119JJ15]の下位に属するFターム

ダマシン技術 (70)

Fターム[4M119JJ15]に分類される特許

1 - 20 / 160

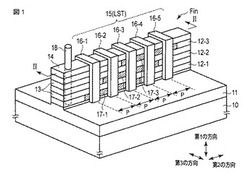

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

磁気メモリ素子

【課題】実施形態による、磁壁制御が容易な磁気メモリ素子を提供する。

【解決手段】磁気メモリ素子100は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線20と、前記磁性細線20に対して前記第1の方向又は前記第1の方向と逆方向に通電可能な一対の第1の電極30と、前記第1の方向に直交する第2の方向において、前記磁性細線20上に設けられた第1の絶縁層40と、前記第2の方向であって前記第1の絶縁層40上に離間して設けられた複数の第2の電極50と、複数の前記第2の電極50と電気的に接続された第3の電極60と、を備える。

(もっと読む)

磁気メモリ

【課題】磁気記録層の強磁性体膜が強い垂直磁気異方性を有する磁気メモリを提供する。

【解決手段】磁気メモリは、強磁性体の下地層51と、下地層51上にの第1非磁性52と、第1非磁性52上の垂直磁気異方性を有する強磁性体のデータ記憶層53と、第2非磁性層20を介してデータ記憶層53に接続された参照層30と、下地層51の下側に接した第1、第2磁化固定層41a、41bとを具備する。データ記憶層53は、反転可能な磁化を有し参照層30とオーバーラップする磁化自由領域13と、磁化自由領域13の端に接続され、第1磁化固定層41aに+z方向に磁化固定された第1磁化固定領域11aと、磁化自由領域13の他の端に接続され、第2磁化固定層41bに−z方向に磁化固定された第2磁化固定領域11bとを備える。磁化自由領域13下の第1非磁性52は、第1、第2磁化固定領域11a、11b下の第1非磁性52よりも厚い。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、MTJ素子がコンタクトプラグ内のシームまたはボイドの影響を受けることなく、MTJ素子の特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。複数のセルトランジスタは、半導体基板上に設けられている。コンタクトプラグは、隣接するセルトランジスタ間に埋め込まれ、該隣接するセルトランジスタ間にある拡散層に電気的に接続されている。層間絶縁膜は、複数のコンタクトプラグ間を埋め込む。記憶素子は、コンタクトプラグの上方に設けられておらず、層間絶縁膜の上方に設けられている。側壁膜は、記憶素子の側面の少なくとも一部を被覆し、半導体基板の表面上方から見たときに、コンタクトプラグに重複するように設けられている。下部電極は、記憶素子の底面と層間絶縁膜との間、および、側壁膜とコンタクトプラグとの間に設けられ、記憶素子とコンタクトプラグとを電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】書き込み電流を低減させたまま、リテンション、特に固定磁化層の大きなリテンションを十分に確保することができ、熱的に安定な動作を可能とする信頼性の高い磁気抵抗素子を実現する。

【解決手段】MTJ10は、下部磁性層1と上部磁性層3とでトンネルバリア層2を挟持し、上部磁性層3上にキャップ層4が形成されてなり、下部磁性層1は、トンネルバリア層2と接するCoFeBからなる第1自由層1aと、第1自由層1aに接するTaからなる挿入層1bと、挿入層1bに接するRuからなるスペーサ層1cと、スペーサ層1cに接するCoPtからなる第2自由層1dとを有して構成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

半導体装置の製造方法

【課題】トレンチを均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、第1の材料からなる第1部分及び前記第1の材料とは異なる第2の材料からなる第2部分を含む被加工基材上に、前記第1部分の直上域に配置され第3の材料からなる第3部分及び前記第2部分の直上域に配置され前記第3の材料とは異なる第4の材料からなる第4部分を含み、前記第3部分及び前記第4部分の双方に開口部が形成されたマスク膜を形成する工程と、前記マスク膜をマスクとして、前記第4の材料のエッチングレートが前記第3の材料のエッチングレートよりも高く、前記第1の材料のエッチングレートが前記第2の材料のエッチングレートよりも高くなるような条件でエッチングを施すことにより、前記第1部分及び前記第2部分をそれぞれ選択的に除去する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】面積の増大を抑えつつ、シリコン膜を用いて所望の特性を有する抵抗素子を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に延在するゲート積層構造膜100a上およびゲート側壁絶縁膜7上にレジスト膜を選択的に形成する。レジスト膜をマスクとして、メタル膜の表面が露出するように、ゲート側壁絶縁膜の上部およびハードマスク膜を、エッチングにより選択的に除去する。抵抗素子領域1000において、メタル膜の露出した表面から、ハードマスク膜が残存するシリコン膜上の領域まで、メタル膜およびメタル膜に繋がるバリアメタル膜を、ウエットエッチングにより除去した後、レジスト膜を除去する。レジスト膜を除去した後、残存するハードマスク膜の上面よりも上の高さまで、埋め込み絶縁膜を成膜する。埋め込み絶縁膜の上部を、残存するハードマスク膜をストッパとして、CMP法により平坦化する。

(もっと読む)

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

1 - 20 / 160

[ Back to top ]