Fターム[5F101BA16]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG形状構造 (858) | 複数FG(単一メモリセル内) (90)

Fターム[5F101BA16]に分類される特許

1 - 20 / 90

不揮発性半導体記憶装置及びその製造方法

【課題】 書き込み動作及び消去動作の両方の特性向上を図る。

【解決手段】 実施形態による不揮発性半導体記憶装置は、半導体基板11と、半導体基板上に形成されたゲート絶縁膜12と、ゲート絶縁膜上に形成され、13族元素であるP型不純物を含有するポリシリコンからなり、下部膜13aと下部膜上に積層された上部膜13bとを有するフローティングゲート電極13と、フローティングゲート電極上に形成された電極間絶縁膜16と、電極間絶縁膜上に形成されたコントロールゲート電極17と、を具備し、上部膜におけるP型不純物の濃度又は活性化濃度は、下部膜におけるP型不純物の濃度又は活性化濃度より高い。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】微細化されても、コントロールゲートとフローティングゲートとの間のカップリング容量比を増大させることができる半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。第1の絶縁膜は、半導体基板上に形成されている。フローティングゲートは、第1の絶縁膜上に設けられた第1のフローティングゲート部分、第1のフローティングゲート部分上に設けられた中間絶縁膜、および、中間絶縁膜上に設けられた第2のフローティングゲート部分を含み、電荷を蓄積可能に構成されている。第2の絶縁膜は、フローティングゲートの上面および側面に設けられている。コントロールゲートは、第2の絶縁膜を介してフローティングゲートの上面および側面に対向し、フローティングゲートの電圧を制御する。フローティングゲートの側面において中間絶縁膜が第1および第2のフローティングゲート部分に対して窪んでいる。

(もっと読む)

導電性側壁スペーサを有する不揮発性メモリ装置及びその製造方法

【課題】従来の窒化膜側壁を電荷トラップ媒体に利用する場合の信頼性劣化を改善した不揮発性メモリ装置を提供する。

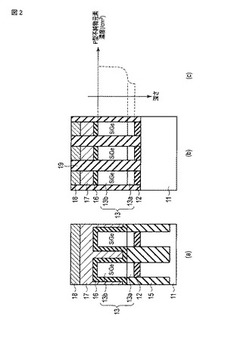

【解決手段】半導体基板21上のゲート絶縁膜22Aと、該ゲート絶縁膜上に順に積層して形成された第1電極膜23、第2電極膜24、及びハードマスク膜25を有するゲート100と、該ゲートの第1電極膜23及び第2電極膜24の両側壁に形成された一対の再酸化側壁スペーサ27と、該再酸化側壁スペーサ及びゲート100のハードマスク膜25の両側壁上に形成された一対の側壁スペーサ28Aと、一対の側壁スペーサ28A上に形成された、電荷を捕獲及び放出する一対の導電性側壁スペーサ29Bと、半導体基板21内に形成された一対のLDD領域26と、半導体基板21内に形成されたソース/ドレイン領域30とを備え、導電性側壁スペーサ29Bが、ゲート100及び側壁スペーサ28Aよりも低い高さを有する。

(もっと読む)

メモリ用シフトレジスタ及びその製造方法

【課題】大容量で、信頼性が高く、少ない工程数で製造可能なメモリ用シフトレジスタを提供する。

【解決手段】一の実施形態によれば、メモリ用シフトレジスタは、基板の主面に平行な第1方向に延び、前記第1方向に垂直な第2方向に向かい合う第1及び第2の制御電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第1の制御電極側に一列に設けられた複数の第1の浮遊電極を備える。さらに、前記レジスタは、前記第1及び第2の制御電極間において、前記第2の制御電極側に一列に設けられた複数の第2の浮遊電極を備える。さらに、前記第1及び第2の浮遊電極の各々は、前記第1方向に垂直な平面に対し、鏡面非対称な平面形状を有する。

(もっと読む)

半導体記憶装置

【課題】書き込み特性及び電荷保持特性に優れたメモリセル(セルトランジスタ)を具備する半導体記憶装置、或いは、メモリセルと共に製造するのに適した選択又は周辺トランジスタの提供。

【解決手段】セルトランジスタ201は、基板101上に、FNトンネル膜として機能するゲート絶縁膜111、最下層の浮遊ゲートに相当する第1の浮遊ゲート112を備える。更に、FNトンネル膜として機能する第1の浮遊ゲート間絶縁膜113を介して形成され、前記セルトランジスタ内の最下層の浮遊ゲートと最上層の浮遊ゲートとの間に介在する第2の浮遊ゲート114を備える。更に、FNトンネル膜として機能する第2の浮遊ゲート間絶縁膜115を介して形成され、前記セルトランジスタ内の最上層の浮遊ゲートに相当する第3の浮遊ゲート116を備える。更に、電荷ブロック膜として機能するゲート間絶縁膜117を介して形成された制御ゲート118を備える。

(もっと読む)

PMOS・NMOS・PMOS・NMOS構造を備えた4トランジスタ不揮発性メモリセル

半導体記憶装置

【課題】メモリセルの面積を縮小しつつ、選択トランジスタや周辺トランジスタの特性を良好にし、且つ製造方法を容易にすることが可能な半導体装置。

【解決手段】半導体記憶装置は、基板101と、基板上に順に形成された第1のゲート絶縁膜、第1の浮遊ゲート、第2のゲート絶縁膜、第2の浮遊ゲート、ゲート間絶縁膜、及び制御ゲートを含み、第1及び第2のゲート絶縁膜は、FN(Fowler-Nordheim)トンネル膜として機能し、ゲート間絶縁膜は、電荷ブロック膜として機能するセルトランジスタ201と、基板上に順に形成されたゲート絶縁膜及びゲート電極を含む選択又は周辺トランジスタ301とを備え、ゲート絶縁膜及びゲート電極は、基板上に形成された第1絶縁膜と、第1絶縁膜上に順に形成され、それぞれ第1の浮遊ゲート、第2のゲート絶縁膜、第2の浮遊ゲート、ゲート間絶縁膜、及び制御ゲートと同じ材料層から形成される。

(もっと読む)

半導体記憶装置

【課題】書込み速度や正気よ速度を向上させつつ、セルトランジスタの電荷保持特性を向上させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板101と、基板上に形成され、FNトンネル膜として機能する第1のゲート絶縁膜111と、第1のゲート絶縁膜上に形成された第1の浮遊ゲート112と、第1の浮遊ゲート上に形成され、FNトンネル膜として機能する第2のゲート絶縁膜113と、第2のゲート絶縁膜上に形成された第2の浮遊ゲート114と、第2の浮遊ゲート上に形成されており、電荷ブロック膜として機能するゲート間絶縁膜115と、ゲート間絶縁膜上に形成された制御ゲート116とを備え、第1及び第2の浮遊ゲートの少なくともいずれかは、メタル層を含んでいる。

(もっと読む)

メモリセルのアレイを作製する方法、メモリセルのアレイ及びメモリセルのアレイにおいてメモリセルを動作させる方法

【課題】安価なメモリデバイスを提供する。

【解決手段】1F2当り少なくとも1ビットを記憶するよう構成されたメモリセルのアレイは、アレイの最小ピッチの半分に等しい距離で離間した電子メモリ機能を与える実質的に縦型の構造を含む。電子メモリ機能を与える構造は、ゲート当り1ビットを超えて記憶するよう構成されている。また、アレイは、実質的に縦型の構造を含むメモリセルに対する電気接点も含む。セルは、第1のソース/ドレイン領域に隣接したゲート絶縁物にトラップされた多数の電荷レベルの1つを有するようプログラムすることができる。これにより、チャネル領域は第1のしきい値電圧領域と第2のしきい値電圧領域とを有し、プログラムされたセルが低減されたドレインソース電流で動作する。

(もっと読む)

Fin−FET型不揮発性メモリ・セル及びアレイ並びにその製造方法

不揮発性メモリ・セルが、基板層を有し、第1の導電型のフィン形状半導体部材が基板層上にある。フィン形状部材は、第2の導電型の第1の領域と、第1の領域から離間配置された第2の導電型の第2の領域とを有し、チャネル領域が第1の領域と第2の領域との間に延びている。フィン形状部材は、第1の領域と第2の領域との間に上面及び2つの側面を有する。ワード線が、第1の領域に隣接し、チャネル領域の第1の部分の上面及び2つの側面に容量結合される。浮遊ゲートが、ワード線に隣接し、上面から絶縁され、チャネル領域の第2の部分の2つの側面に容量結合される。 (もっと読む)

半導体装置と、それを用いた可変インピーダンス回路および共振回路

【課題】電源電圧が遮断されている場合でも記憶データに基づいてスイッチ回路を導通状態または非導通状態にすることが可能な半導体装置を提供する。

【解決手段】この半導体集積回路装置では、浮遊ゲートおよび制御ゲートを有するメモリトランジスタMAと、ゲートが浮遊ゲートに接続され、メモリトランジスタMAの記憶データに応じてオンまたはオフするNチャネルMOSトランジスタQAとを含む。したがって、電源電圧VCCが遮断されている場合でも、メモリトランジスタMAの記憶データに基づいてトランジスタQAをオンまたはオフさせることができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コントロールゲートが半導体基板に形成された不純物拡散層によって構成されている不揮発性半導体記憶装置において、信頼性を維持しつつ、カップリング比を大きくする。

【解決手段】P型の半導体基板1に、N型ウェル3とN型高濃度拡散層17からなるコントロールゲートと、コントロールゲートとは絶縁され、互いに間隔をもって形成された2つのN型拡散層からなるソース5及びドレイン7が形成されている。コントロールゲート表面に第1絶縁膜11が形成されている。ソース5及びドレイン7の間の半導体基板1表面に第2絶縁膜13が形成されている。第1絶縁膜11上からフィールド酸化膜9上を介して第2絶縁膜13上にわたって形成された半導体膜からなるフローティングゲート15が形成されている。コントロールゲートの一部分を構成するN型高濃度拡散層17は、フローティングゲート15下にも配置されている。

(もっと読む)

不揮発性半導体記憶装置、その製造方法、その書き込み方法、その読み出し方法、記録媒体並びに半導体記憶装置

【課題】 電荷捕獲量の調節を容易且つ確実に行い、情報ばけ等の不都合の発生を防止して所望の多値情報を記憶する。

【解決手段】 ソース領域3−ドレイン領域4間のチャネル領域Cとゲート電極6との間に、ゲート酸化膜11、シリコン窒化膜12、シリコン酸化膜13、シリコン窒化膜14、シリコン酸化膜15、シリコン窒化膜16及びシリコン酸化膜17が順次積層されてなる電荷捕獲膜5が配されて半導体記憶装置が構成される。ここで、各窒化膜12,14,16とその下層の各酸化膜11,13,15,17との間に存するトラップに電荷を蓄積することで、4値("00","01","10","11")の情報が記憶される。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】不揮発性メモリと画素TFTとを同一基板上に形成でき、且つ両者を良好に動作させることが可能な電気光学装置を提供する。

【解決手段】画素TFTのゲート絶縁膜18を不揮発性メモリのトンネル絶縁膜(第1の絶縁膜)35と、トンネル絶縁膜35よりも膜厚の大きい第2の絶縁膜37によって構成する。また、フローティングゲート電極36のコントロールゲート電極60側の面を凹凸とし、該凹凸によってフローティングゲート電極36の表面積を拡げる。これにより、フローティングゲート電極36とコントロールゲート電極60との間の容量を、フローティングゲート電極36と半導体層33との間の容量よりも大きくする。

(もっと読む)

EEPROM

【課題】データの書き込み効率の向上およびデータの書き込み時間の低減を達成することができる、EEPROMを提供する。

【解決手段】半導体層には、第1不純物領域5、第2不純物領域6、第3不純物領域7、第4不純物領域8および第5不純物領域9が形成されている。第1セレクトゲート11は、第1不純物領域5と第2不純物領域6との間の領域に、第1絶縁膜10を挟んで対向している。第1フローティングゲート12は、第2不純物領域6と第3不純物領域7との間の領域に、第1絶縁膜10を挟んで対向している。第2フローティングゲート19は、第3不純物領域7と第4不純物領域8との間の領域に、第1絶縁膜10を挟んで対向している。第2セレクトゲート20は、第4不純物領域8と第5不純物領域9との間の領域に、第1絶縁膜10を挟んで対向している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

EEPROM

【課題】2つのメモリトランジスタに同一のデータを確実に書き込むことができる、W(ダブル)セル方式のEEPROMを提供する。

【解決手段】半導体層には、第1不純物領域8、第2不純物領域9、第3不純物領域10、第4不純物領域11、第5不純物領域12および第6不純物領域13が形成されている。セレクトゲート15は、第1不純物領域8と第2不純物領域9との間の領域に、第1絶縁膜14を挟んで対向している。第1フローティングゲート16は、第2不純物領域9と第3不純物領域10との間の領域および第5不純物領域12に、第1絶縁膜14を挟んで対向している。第2フローティングゲート20は、第3不純物領域10と第4不純物領域11との間の領域および第6不純物領域13に、第1絶縁膜14を挟んで対向している。第5不純物領域12および第6不純物領域13は、第2不純物領域9と接続されている。

(もっと読む)

不揮発性半導体記憶素子とその製造方法

【課題】構造が簡単で、素子サイズを縮小でき、高集積化に適し、且つ欠陥の起こりにくい不揮発性半導体記憶素子を提供する。

【解決手段】不揮発性半導体記憶素子10は、1ビット又は多ビット分のデータを記憶する素子であり、チャネル領域14を挟んで配置されたソース領域12とドレイン領域13と、ゲート絶縁膜15,18と、保護絶縁膜20に埋設され、チャネル領域14上に並んで配置され、ソース領域12及びドレイン領域13に対向しない複数の浮遊ゲート電極16,17と、ゲート絶縁膜15,18上に、チャネル領域14に対向して配置されたコントロールゲート19と、を備える。各浮遊ゲート電極16,17は、物理的或いは電気的にチャネル幅と同等かそれ以上の大きさを有する。

(もっと読む)

1 - 20 / 90

[ Back to top ]