Fターム[5F101BA36]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 薄膜化又は絶縁膜材料の特徴部位 (1,645) | CGとFG間 (1,254)

Fターム[5F101BA36]に分類される特許

1,241 - 1,254 / 1,254

ピラー構造セルのフラッシュメモリ技術

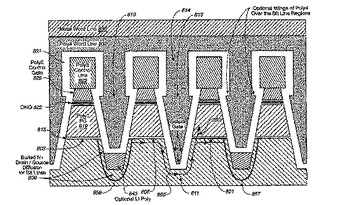

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

スタガー式ローカル接続構造を持つメモリセルアレイ

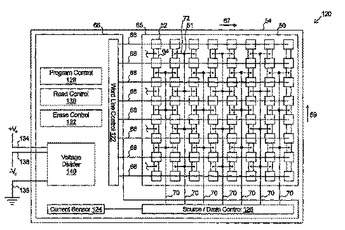

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

短チャネル効果を減少させる埋め込みチャネルフラッシュ構造

短チャネル効果を減少させたメモリセルを記載する。ソース領域(54)およびドレイン領域(56)を半導体ウェーハ(58)中に形成する。ソース領域(54)およびドレイン領域(58)の間にトレンチ領域(59)を形成する。このトレンチ領域、ソース領域およびドレイン領域の下に埋め込みチャネル領域(52)を形成する。半導体基板のトレンチ領域中にゲート絶縁層(60)を形成する。このゲート絶縁層は、埋め込みチャネル領域上に、およびソース領域とドレイン領域との間に形成される。埋め込みチャネル領域の上の半導体基板上に、制御ゲート層(70)を形成する。この制御ゲート層は、ゲート絶縁層によって埋め込みチャネルから分離される。  (もっと読む)

(もっと読む)

2−トランジスタメモリセル及びその製造方法

本発明は、メモリゲートスタック(1)を有する記憶トランジスタ(1)及び選択トランジスタを有する2-トランジスタメモリセルを基板(50)上に製造する方法であって、トンネル誘電層(51)が前記基板(50)と前記メモリゲートスタック(1)との間にもたらされる方法を提供する。前記方法は、第一の導電層(52)及び第二の導電層(54)をもたらし、前記第二の導電層(54)をエッチし、それによってコントロールゲートを形成し、前記第一の導電層(52)をエッチし、それによってフローティングゲートを形成することによって前記メモリゲートスタック(1)を形成するステップを有する。前記方法は更に、前記第一の導電層(52)がエッチされる前に、前記トンネル誘電層(51)の下に形成されるべきチャネルの方向で前記コントロールゲートに対してスペーサ(81)を形成するステップと、その後、前記第一の導電層(52)をエッチするために前記スペーサ(81)をハードマスクとして使用し、それによって前記フローティングゲートを形成し、それによってフローティングゲートをコントロールゲートに自己整合させるステップとを有することを特徴とする。本発明は、前記コントロールゲート(54)は前記フローティングゲート(52)よりも小さくなり、スペーサ(81)が、前記コントロールゲート(54)に隣接してもたらされるメモリセルも提供する。  (もっと読む)

(もっと読む)

電荷損失が減少された窒化物層を備えるメモリセル構造及びその製造方法

本発明の一実施形態に従って、半導体基板(210)、半導体基板上に配置された第1シリコン酸化物層(215)、第1シリコン酸化物層上に配置された電荷格納層(220)、電荷格納層上に配置された第2シリコン酸化物層(225)、及び第2シリコン酸化物層上に配置されたゲート層(230)がメモリセル構造に含まれる。例示的な実施形態では、例えば、水素含有量が約0at%〜約0.5at%の範囲に減少されたシリコン窒化物が電荷格納層(220)に含まれる。電荷格納層(220)における水素含有量が減少されることで、結果として電荷損失が減少される。電荷損失が減少された電荷格納層(220)が、メモリデバイスにおける閾電圧シフト、プログラミングデータ損失及びプログラミング性能損失を減少する利点を有し、その結果メモリデバイスパフォーマンスを改善する。  (もっと読む)

(もっと読む)

不揮発性メモリ装置を製造する方法及びそれによって得られるメモリ装置

本発明は、ダブル・ゲート・スタック及びシングル・アクセス・ゲートを備える不揮発性メモリ・セル(50)を加工する方法に関する。この方法は、アクセス・ゲートを加工する方法を、自己整合的な、ソース注入とは別のドレイン注入と組み合わせる。本発明の方法は、マスク位置合せ精度を考慮せずに、メモリ装置を消去するための延長されたドレインを自己整合的に注入することを可能にする。さらに、この方法は、さらなるマスクを使用せずにドレイン及びソース注入を互いに異なるドーピングで実施する方法を提供する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置、その製造方法、電子カード及び電子装置

【課題】 カップリング比のばらつきを小さくできるNAND型EEPROMを提供する。

【解決手段】 メモリセルの電荷蓄積層17の上層導電部23は、互いに間を設けて形成された一対の立上り部27により構成される内側面29及び外側面31を有する。内側面29側には底面高さ調節層43があり、外側面31側には素子分離絶縁層5がある。このため、半導体基板9の位置(A)のメモリセルと位置(B)のメモリセルとで、立上り部27の高さが異なっていても、電荷蓄積層17と制御ゲートCGとが対向する領域の面積を同じにできる。

(もっと読む)

UVチャージングを減少するPECVDシリコンリッチ・シリコン酸化物層

メタライゼーションの前に、UV透過を低減するシリコンリッチ・シリコン酸化物層(500)をPECVDにより層間絶縁膜(300)上にたい積する。これによりVtが減少する。実施形態は、1.7から2.0のR.I.を有するUVを透過しないシリコンリッチ・シリコン酸化物層(500)をたい積するステップを含んでいる。  (もっと読む)

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

垂直方向の突起部を有するフローティングゲート構造

基板面から離れて延在する突起部を有するフローティングゲート構造を開示する。この突起部によって、フローティングゲートとコントロールゲートとを結合するための増加した表面積をフローティングゲートに提供することが可能となる。1つの実施形態では、フローティングゲートの個々の側面でワードラインが下方へ延在して、同じ列の隣接するフローティングゲートを遮蔽する。別の実施形態では、突起部を有するフローティングゲートの組立て製造処理工程を開示する。残りのフローティングゲートに対して自己位置合せを行うために突起部を形成してもよい。  (もっと読む)

(もっと読む)

素子間分離のための半導体構造中の素子間のボイドの使用

記憶素子間の静電結合レベルを低減するために、隣接する電荷記憶素子を有するフラッシュEEPROMまたは他のタイプのメモリセルアレイを素子間にガスが充填されているボイドとともに形成し、これにより電荷記憶素子間の漏れ結合およびアレイから読み出されるデータ中に結果として生じるエラーを低減する。  (もっと読む)

(もっと読む)

フラッシュメモリデバイスの特性を改善する方法

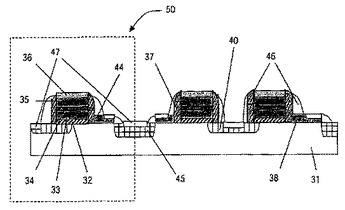

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

1,241 - 1,254 / 1,254

[ Back to top ]