Fターム[5F101BC04]の内容

不揮発性半導体メモリ (42,765) | 電荷注入 (1,823) | アバランシェ注入 (75)

Fターム[5F101BC04]の下位に属するFターム

ソースドレイン接合ブレークダウン (52)

Fターム[5F101BC04]に分類される特許

1 - 20 / 23

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

メモリセルのアレイを作製する方法、メモリセルのアレイ及びメモリセルのアレイにおいてメモリセルを動作させる方法

【課題】安価なメモリデバイスを提供する。

【解決手段】1F2当り少なくとも1ビットを記憶するよう構成されたメモリセルのアレイは、アレイの最小ピッチの半分に等しい距離で離間した電子メモリ機能を与える実質的に縦型の構造を含む。電子メモリ機能を与える構造は、ゲート当り1ビットを超えて記憶するよう構成されている。また、アレイは、実質的に縦型の構造を含むメモリセルに対する電気接点も含む。セルは、第1のソース/ドレイン領域に隣接したゲート絶縁物にトラップされた多数の電荷レベルの1つを有するようプログラムすることができる。これにより、チャネル領域は第1のしきい値電圧領域と第2のしきい値電圧領域とを有し、プログラムされたセルが低減されたドレインソース電流で動作する。

(もっと読む)

薄膜トランジスタを利用して不揮発性メモリとする方法およびその装置

【課題】薄膜トランジスタ(TFT)のベースを利用して電荷を保存し、不揮発性メモリとする方法を提供する。

【解決手段】薄膜トランジスタ10を利用し、そのうち薄膜トランジスタ10は中間がベース21、両端がそれぞれドレイン電極22、ソース電極23である半導体層20を備え、絶縁表面31を備えた基板30上に設置され、ゲート電極絶縁層41が前記半導体層20上に設置され、ゲート電極40がゲート電極絶縁層41上に設置され、電子がゲート電極40の電場作用下で、熱電子界放射により電子正孔対を形成し、電子正孔対がゲート電極40の垂直電場により分離され、複数のキャリア(nチャネルでいうと正孔)が薄膜トランジスタ10のベース21に注入され、薄膜トランジスタ10の閾値電圧の変化を引き起こし、書き込み動作が完了する。

(もっと読む)

半導体装置、TFT基板、表示装置、携帯機器

【課題】同一絶縁基板上に形成された2つのトランジスタの拡散層の抵抗値を同じにすることのできる新構造のトランジスタを搭載した半導体装置を提供する。

【解決手段】同一絶縁基板上に第1及び第2のトランジスタが形成された半導体装置において、第1のトランジスタ(図中左側のトランジスタ)は、第1のゲート電極104a下部に形成された第1の絶縁膜103aと、拡散層102a2,102a3領域上に形成された第2の絶縁膜103bとを備え、第2のトランジスタ(図中右側のトランジスタ)は、第2のゲート電極104b下部及び拡散層102b2,102b3領域上に形成された膜厚の厚い第2の絶縁膜103bを備え、これら第1の絶縁膜103b及び第2の絶縁膜103aより上層に第1及び第2のゲート電極104a,104bがそれぞれ配置されており、かつ、第1の絶縁膜103aが第2の絶縁膜103bよりも薄く形成された構造となっている。

(もっと読む)

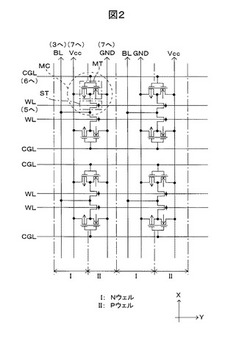

不揮発性半導体記憶装置及びその使用方法

【課題】 セル面積の著しい増加を招かず、しかし、ディスターブの問題を解決した不揮発性記憶素子を提供すること。

【解決手段】 半導体基板に形成され第1の端子に接続されたp型の第1のウェルと、第1のウェルに形成され、第2の端子と第3の端子の間に直列に接続された第1のNMOSトランジスタ及び第2のNMOSトランジスタと、半導体基板に形成され第4の端子に接続されたn型の第2のウェルと、第2のウェルに形成され、第5の端子と第6の端子の間に直列に接続された第1のPMOSトランジスタ及び第2のPMOSトランジスタとを含み、第1のNMOSトランジスタのゲートは第7の端子を構成し、第1のPMOSトランジスタは第8の端子を構成し、第2のNMOSトランジスタと第2のPMOSトランジスタのゲートは共通に接続され、かつ、フローティング状態にあることを特徴とするメモリセルを含む不揮発性半導体記憶装置。

(もっと読む)

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

不揮発性半導体記憶素子および不揮発性半導体記憶装置

【課題】読み出しマージンを大きくとることができ、且つ、スタンバイ状態において記憶トランジスタに電圧ストレスが印加されない書き換え可能な不揮発性半導体記憶素子を提供する。

【解決手段】TRUE側記憶トランジスタおよびBAR側記憶トランジスタと、両記憶トランジスタのドレインと対応するビット線との間に接続された選択トランジスタと、2つの選択トランジスタのゲートに接続されたワード線と、2つのCMOSインバータをクロス接続して構成されたフリップフロップと、各記憶トランジスタのドレインとフリップフロップの対応する入出力部との間に接続された2つのゲートトランジスタとを備える。

(もっと読む)

不揮発性メモリトランジスタ

【課題】書き換え可能な不揮発性メモリトランジスタであって、書き換えの繰り返しによる閾値電圧特性の変化が抑制された信頼性の高い不揮発性メモリトランジスタを提供する。

【解決手段】第1導電型の半導体基板31の表層部に、第2導電型のソース領域32とドレイン領域33が形成され、トンネル酸化膜41を介して、半導体基板31上でドレイン領域33に部分的に重なるようにして、浮遊ゲート電極51が設けられてなる書き換え可能な不揮発性メモリトランジスタ100であって、ソース領域32とドレイン領域33を最短距離で結ぶ断面において、ドレイン領域33と浮遊ゲート電極51の重なり寸法Lが、0.15μm以上、0.5μm以下、である不揮発性メモリトランジスタ100とする。

(もっと読む)

情報書込方法、情報読出方法、半導体装置、及び半導体装置の製造方法

【課題】半導体装置の製造工程数を少なくする為に、トランジスタを不揮発メモリ素子として利用する為の情報書込方法を提供する。

【解決手段】第1ゲート絶縁膜及び第1ゲート電極を具備する第1トランジスタ10b、並びに第1ゲート絶縁膜と同じ厚さの第2ゲート絶縁膜及び第1ゲート電極と同じ形状の第2ゲート電極を具備していて第1トランジスタと同一導電型の第2トランジスタ10bを具備する半導体装置に情報を書き込む情報書込方法であって、第1ゲート絶縁膜に電子又は正孔を捕捉させて、第1トランジスタの閾値電圧の絶対値を低下させて規定値超にし、かつ第2トランジスタの閾値電圧の絶対値を規定値未満に維持することにより、第1トランジスタ10b及び第2トランジスタ10bの一方に0を記憶させ、他方に1を記憶させて情報を書き込む。

(もっと読む)

不揮発性半導体記憶素子

【課題】データ消去動作によりメモリセルにホールトラップやゲート酸化膜の欠陥を生じさせにくく、素子特性の変動を抑制して動作の安定化を図った不揮発性半導体記憶素子を提供する。

【解決手段】単層のポリシリコン層を有する断面構造を有する不揮発性半導体記憶素子は、互いに絶縁分離されるメモリセル部a、データ消去部b、及びコントロールゲート部cを含む。メモリセル部a及びデータ消去部bはMOSトランジスタで構成され、コントロールゲート部cは、MOSキャパシタで構成される。これら3つの部位は、前記単一のポリシリコン層で構成される共通のフローティングゲートを有する。フローティングゲート6cの電位を制御してメモリセルaをオンにすることにより、フローティングゲート6aにデータを書き込み、フローティングゲート6cの電位を制御してデータ消去部bをオンにすることにより、フローティングゲート6bを通じてデータを消去する。

(もっと読む)

半導体装置及びその製造方法

【課題】周辺回路部における電荷蓄積膜への電荷の注入量を減らすことで、周辺回路のホットキャリアによる劣化を防止する。

【解決手段】半導体基板20に設定された第1領域23及び第2領域26に、それぞれ第1電界効果トランジスタ30及び第2電界効果トランジスタ60が形成されて構成される。第1電界効果トランジスタは、第1ゲート電極34に隣接して設けられていて、順次に積層して形成された第1下部絶縁膜52及び第1電荷蓄積膜54を有する第1側壁部50を備えている。第2電界効果トランジスタは、第2ゲート電極64に隣接して設けられていて、順次に積層して形成された第2下部絶縁膜82及び第2電荷蓄積膜84を有する第2側壁部80を備えている。第2下部絶縁膜は、ノンドープトシリケートガラスを含んでいる。さらに、第2側壁部の幅が第1側壁部の幅よりも大きく、第2下部絶縁膜の厚みが第1下部絶縁膜の厚みよりも大きい。

(もっと読む)

ポリシリコン浮遊ゲートにPN接合を形成した不揮発性メモリ・セル及びそのメモリ・セルを製造する方法

【課題】浮遊ゲート型の不揮発性メモリ・セル及びそのメモリ・セルを製造する方法を提供する。

【解決手段】ソース側(13B)上に軽くドーピングされたホウ素と、ドレイン側(13A)+チャネル領域(Ch)上に高度にドーピングされたヒ素又はリンとを有するP−N接合多結晶シリコン浮遊ゲート(13)により、ソース(11)とドレイン(12)とを有するメモリ・セル(10)のアレーを形成する。多結晶浮遊ゲート(13)におけるP−N接合(JU)を使用することにより、メモリ・セル(10)がデプリーションへ移行するのを阻止し、稠密な分布の消去しきい電圧VTを発生させることにより過消去特性を得ると共に、前記ゲート酸化物(30)を介する電子の移動が少ないので、デバイス寿命を改善する。

(もっと読む)

不揮発性半導体メモリ及びその動作方法

【課題】電荷蓄積層に対するホットホールの注入効率を向上させるNMOSトランジスタ型の不揮発性半導体メモリを提供する。

【解決手段】NMOSトランジスタ型の不揮発性半導体メモリは、P型シリコン層20中にソース/ドレインとして形成された第1及び第2N型拡散層21,22と、第1及び第2N型拡散層21,22に挟まれたチャネル領域CNL上に絶縁膜30を介して形成されたゲート電極50と、その絶縁膜30中に形成された電荷蓄積層40とを備える。第1N型拡散層21から第2N型拡散層22へ向かう方向は、P型シリコン層20の結晶方位<100>である。データ書き換え時、ホットホールが絶縁膜30のポテンシャル障壁を超えて電荷蓄積層40に注入される。

(もっと読む)

不揮発性メモリトランジスタおよびその駆動方法

【課題】低電圧で駆動でき、書換えによるダメージを抑制できると共に、セル数が多い場合であっても消去後の閾値電圧のバラツキを抑制することができる不揮発性メモリトランジスタおよびその駆動方法を提供する。

【解決手段】浮遊ゲート電極15が、ドレイン12近傍に偏って電荷蓄積が可能な構造を有してなり、書込み過程において、ソース13を基板電位と同電位とし、ドレイン12に正の電圧を印加した状態で、制御ゲート電極17に正の電圧を印加し、消去過程において、ソース13を浮遊電位とし、制御ゲート電極17を基板電位または負の電圧を印加した状態で、ドレインに書込み過程より高い正の電圧を印加し、読出し過程において、ドレイン12を基板電位とし、ソース13に正の電圧を印加した状態で、制御ゲート電極17に正の電圧を印加する、不揮発性メモリトランジスタ100およびその駆動方法とする。

(もっと読む)

半導体装置

【課題】他の半導体装置と一体形成が可能な不揮発性メモリを提供する。

【解決手段】不揮発性メモリを構成するメモリ素子、スイッチング素子,および他の周辺回路をTFTでもって基板上に一体形成する。メモリ素子TFTの半導体活性層の厚さが、他のTFTの半導体活性層の厚さよりも薄いので、メモリ素子TFTのチャネル領域でインパクトイオン化が起こりやすくなる。こうすることによって、メモリ素子の低電圧書込み/消去を実現することができ、劣化が起こりにくく、小型化が可能な不揮発性メモリが提供される。

(もっと読む)

不揮発性記憶装置および半導体集積回路装置

【課題】標準C−MOSプロセスの製造工程を変更せずに製造可能であり、ゲート酸化膜厚の影響を受けない廉価な不揮発性メモリを提供する。

【解決手段】負荷トランジスタT11,T21と記憶トランジスタT12,T22との直列回路一対を有して、それらをスタティックラッチ形態に接続してフリップフロップを構成し、このフリップフロップの入出力部P1,P2とビットラインBLT,BLBとの間にトランスファゲートT13,T23を接続し、さらにフリップフロップの2つの入出力部P1,P2にバッファ回路であるC−MOSインバータINV1,INV2を接続する。また、フリップフロップの2つの負荷トランジスタT11,T21のソースと電源ラインVCCとの間にリーク電流遮断素子T16,T26を設け、書き込み時にT16,T26を遮断する。

(もっと読む)

High−K誘電体における正孔トラップを用いるメモリ

ゲート誘電体を備えるメモリセルを有する不揮発性メモリが記載される。ゲート誘電体は、トランジスタのコントロールゲートとチャネル領域との間の、正に帯電した正孔をトラップする多層電荷トラップ誘電体である。多層電荷トラップ誘電体は、少なくとも1つのHigh−K(高誘電体定数)層を含む。 (もっと読む)

半導体装置

【課題】新規な構造を有する一層ゲート型の不揮発性メモリ素子を含む半導体装置を提供する。

【解決手段】半導体装置は、不揮発性メモリ素子C100を含む半導体装置であって、第1領域10Aと、該第1領域10Aに隣接した第2領域10Bと、該第2領域10Bに隣接した第3領域10Cとを含み、さらに、半導体層10に設けられ、不揮発性メモリ素子C100の形成領域を画定する分離絶縁層20と、前記第1領域10Aに形成された第1拡散層12と、前記第2領域10Bに形成されたP型の第1ソース領域及び第1ドレイン領域36と、前記第3領域10Cに形成されたP型の第2ソース領域及び第2ドレイン領域38と、前記半導体層10上方に形成された絶縁層30と、前記絶縁層30上方に形成された導電層32とを含む。

(もっと読む)

1 - 20 / 23

[ Back to top ]