Fターム[5F101BC13]の内容

不揮発性半導体メモリ (42,765) | 電荷注入 (1,823) | チャンネル注入 (848) | キャリア走行方向、段差 (12)

Fターム[5F101BC13]に分類される特許

1 - 12 / 12

半導体装置

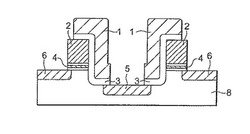

【課題】電荷トラップを含むゲート電極と、電荷トラップを含まないゲート電極とを有する半導体装置において、両ゲート電極下のチャネル層にポテンシャルバリアが形成されないようにする。

【解決手段】基体8上に絶縁膜を介して第一のゲート電極1、第二のゲート電極2が形成され、両ゲート電極1、2を挟んで第一の拡散層5と第二の拡散層6が形成され、両拡散層5、6の間にチャネル層が形成されている。前記絶縁膜は、第一の拡散層5から第二の拡散層6の方向に第一の絶縁領域3、第二の絶縁領域4が配設された、両絶縁領域3、4のうち第二の絶縁領域4が電荷トラップを含み、第一の絶縁領域3を介して第一のゲート電極1が、第二の絶縁領域4を介して第二のゲート電極2が形成され、両ゲート電極1、2底部下に形成されるチャネル層の高さが相互に異なり、第二の拡散層6の先端部は、第二のゲート電極2直下の領域にまで到達している。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】従来の半導体記憶装置では、十分に半導体チップの面積を削減することができない問題があった。

【解決手段】本発明の半導体記憶装置は、半導体基板の平坦部に形成されたドレイン領域13と、半導体基板に形成された凸部の上端部に形成されたソース領域10と、ドレイン領域13の一部と重なる領域であって、かつ、平坦部の上層に形成されるコントロールゲート12と、コントロールゲート12と隣り合った領域であって、平坦部、凸部の壁面及びソース領域10の一部を覆う領域に形成されるフローティングゲート11と、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】N+型ソース層とフローティングゲートとのカップリング比を高くしてプログラム特性を改善すると共にメモリーセルの面積の縮小化を図る。

【解決手段】N+型ソース層4の両側にトレンチ3を形成する。トレンチ3の側壁は2つの素子分離層STI2の端面と平行なトレンチ側壁2a、トレンチ側壁2bと、STI2に垂直な面からなるトレンチ側壁3a、及びトレンチ側壁3aと平行でないトレンチ側壁3bから構成される。かかる構成のトレンチ3の上部からトレンチ側壁3aに平行で、且つP型ウエル層1に垂直又は角度をもった砒素イオン等のイオン注入を行い、トレンチ3底面からトレンチ側壁3bに延在するフローティングゲートFG6と広い面積で対峙するN+型ソース層4を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極下で電荷蓄積層が分離した半導体装置と、容易に製造する方法を提供する。

【解決手段】半導体基板10に設けられた2つの溝部12と、2つの溝部12のそれぞれの側面に設けられ、溝部12の底面で分離された絶縁体からなる電荷蓄積層24と、2つの溝部12のそれぞれの底面の半導体基板10に設けられたビットライン14と、を具備し、半導体基板10のうち、2つの溝部12の一方の側面から2の溝部12の間に設けられた凸部13の上面を介し2つの溝部12の他方の側面にかけてチャネル領域30が形成される。

(もっと読む)

半導体素子及びこの半導体素子を用いた装置

【課題】高速な書込み及び消去動作を比較的低電圧で行い、かつ書換え劣化を抑えることで、メモリウインドウが大きく信頼性の高いメモリ素子を、低コストで提供する。

【解決手段】メモリ素子は、絶縁基板上に設けられた半導体層と、P型の導電型を有する第1の拡散層領域及び第2の拡散層領域と、第1の拡散層領域と第2の拡散層領域との間のチャネル領域を覆い、チャネル領域より電荷を注入され得る電荷蓄積膜と、電荷蓄積膜をはさんでチャネル領域とは反対側に位置するゲート電極とを有する。

(もっと読む)

不揮発性メモリーとその製造方法および操作方法

【目的】より簡単な工程で製造コストを削減し、単一メモリーセルに2ビットデータを蓄積してデバイスの集積度を向上させるとともに、不都合な第2ビット効果やパンチスルーを抑止する不揮発性メモリーとその製造方法および操作方法を提供する。

【解決手段】基板上に形成したメモリーセルを有する不揮発性メモリーの製造を提供する。基板中にトレンチが形成される。メモリーセルが第1ゲートと第2ゲートと電荷蓄積層と第1ソース/ドレイン領域と第2ソース/ドレイン領域とを有する。第1ゲートが基板のトレンチ中に配置される。第2ゲートが基板上のトレンチ一側に配置される。電荷蓄積層が第1ゲートおよび基板間ならびに第2ゲートおよび基板間に配置される。第1ソース/ドレイン領域が基板中のトレンチボトムに配置される。第2ソース/ドレイン領域が基板中の第2ゲート一側に配置される。

(もっと読む)

不揮発性半導体メモリ装置及びその製造方法

【課題】書き込み特性や読み込み特性に優れ、かつ製造が容易な不揮発性半導体記憶装置及びその製造方法を提供すること。

【解決手段】ほぼ平行に形成された複数のソース/ドレイン領域11、及び、前記複数のソース/ドレイン領域11の間に凹部12が形成された半導体基板1と、前記半導体基板1の前記凹部12に形成される電荷蓄積ゲート3と、前記複数のソース/ドレイン領域11に交差し、かつ、前記蓄積ゲート3上に絶縁層を介して配置される複数の導電ゲート6と、を有する不揮発性半導体記憶装置とする。

(もっと読む)

半導体不揮発性メモリ、半導体不揮発性メモリへの情報の記録方法及び半導体不揮発性メモリの製造方法

【課題】電荷注入効率を高め、少ない電流及び低い電圧での書込みを可能にする。

【解決手段】制御電極34は、第1導電型の半導体基板20の一方の主表面上に絶縁膜32を介して設けられている。一対の不純物拡散領域24a、24bは、半導体基板の表層領域の制御電極を挟む領域部分に形成されている。抵抗変化部22は、半導体基板の表層領域の、制御電極の下側の領域部分と不純物拡散領域との間に形成されている。抵抗変化部は、第2導電型であり、不純物拡散領域よりも不純物濃度が低い。主電極は、半導体基板の不純物拡散領域上に設けられている。第1電荷蓄積部40aは、半導体基板上の、第1主電極36aと制御電極とによって挟まれる部分に設けられている。第2電荷蓄積部40bは、半導体基板上の、第2主電極36bと制御電極とによって挟まれる部分に設けられている。

(もっと読む)

トレンチに形成された選択ゲートの上に制御ゲートを備えるプログラム可能な構造

半導体記憶セルは、半導体層に形成された第1トレンチの下の第1ソース/ドレイン領域(102)を備える。第2ソース/ドレイン領域は、半導体層の第2トレンチの下に位置する。第1トレンチ(108)における第1選択ゲート(130−1)および第2トレンチ(108)における第2選択ゲート(130−2)は、選択ゲート誘電体によってライナーを施される。電荷貯蔵スタックは選択ゲートの上に位置し、制御ゲートはスタックの上に位置する。DSEは、ポリシリコンの慎重な堆積物を含んでもよい。第1および第2の選択ゲートの上面は、第1および第2のトレンチの上面より低い。制御ゲートは、選択ゲートに対し垂直に延び、選択ゲートを横切る連続した制御ゲートであってもよい。このセルは、半導体層に対する接点を含んでもよい。制御ゲートは、第1選択ゲートの上の第1制御ゲートと、第2選択ゲートの上の第2制御ゲートとを含んでよい。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 セクタ単位での消去を可能とした半導体記憶装置を提供する。

【解決手段】 セルアレイ2内のワード線を8本ごとに区分し、各ブロックに消去セクタES0〜ES15を構成する。シリコン基板に所定の負電圧を印加した状態で、消去対象の消去セクタに属する8本のワード線に所定の正電圧を印加するとともに、その他の消去対象外の消去セクタに属するワード線を接地することにより、消去対象の消去セクタに属するメモリセルには消去動作を行わせ、消去対象外の消去セクタに属するメモリセルには消去動作を行わせない。これにより上記消去セクタ単位でのセクタ消去が実現される。セルアレイ2内にはメモリセルが2次元マトリクス状に配列されている。メモリセルは、1対のフローティングゲートを有し、2ビット以上のデータを書き替え自在に保持することができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 製造が容易であり、かつ動作の信頼性が高い半導体記憶装置を提供する。

【解決手段】 セルトランジスタ11は、p型シリコン基板、コントロールゲートCG、及び電気的に孤立した一対のフローティングゲートFG1,FG2からなる。シリコン基板には、コラム方向に延在した帯状の凸部13が形成されており、ソース又はドレインとして機能する一対の帯状のn型拡散領域14a,14bが凸部13を挟む表層に形成されている。コントロールゲートCGは、凸部13及びフローティングゲートFG1,FG2の上に絶縁膜を介して形成され、帯状にロウ方向に延在している。コラム方向に関するフローティングゲートFG1,FG2の幅W1はコントロールゲートCGの幅W2より大きい。フローティングゲートFG1,FG2及びコントロールゲートCGは、技術的課題のあるコラム方向におけるセルフアラインプロセスを用いずに簡単に形成することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】スプリットゲート型の不揮発性半導体記憶装置のメモリセルを確実に形成できると共に、該メモリセルをMOSトランジスタと同一の半導体基板上に形成する際に、本発明のメモリセルがMOSトランジスタの動作特性に影響を与えないようにする。

【解決手段】シリコンからなる半導体基板11上に、ゲート酸化膜12を介して多結晶シリコンからなる制御ゲート電極13が形成されている。制御ゲート電極13の両側面上には、膜厚がそれぞれ7nm程度のシリコン酸化膜及びシリコン窒化膜の積層体が堆積されてなり、浮遊ゲート電極15が形成される際に制御ゲート電極13を保護する保護絶縁膜14が形成されている。制御ゲート電極13の一方の側面上には、保護絶縁膜14を介して対向し且つ制御ゲート電極13と容量結合する浮遊ゲート電極15が形成されている。

(もっと読む)

1 - 12 / 12

[ Back to top ]