Fターム[5F101BD38]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 分離 (2,126) | ガードリング寄生チャンネル防止拡散 (21)

Fターム[5F101BD38]に分類される特許

1 - 20 / 21

半導体記憶装置及びその製造方法

【課題】素子分離層の幅を狭くしつつ、素子分離層の底部を介した電流のリークを抑制する。

【解決手段】基板111と、ゲート絶縁膜121と、第1のゲート電極層122と、トランジスタ間の第1のゲート電極層122及びゲート絶縁膜121を貫通し、基板111とゲート絶縁膜121との界面S1よりも深い位置に底面を有する素子分離溝Tと、素子分離溝Tに埋め込まれた素子分離層131と、ゲート間絶縁膜123と、選択トランジスタ102を構成するゲート間絶縁膜123を貫通する第1の穴H1と、周辺トランジスタ103を構成するゲート間絶縁膜123を貫通する第2の穴H2と、素子分離層131上のゲート間絶縁膜123を貫通し、素子分離層131とゲート間絶縁膜123との界面S2よりも深い位置に底面を有する第3の穴H3と、第1から第3の穴H3に埋め込まれた部分を有する第2のゲート電極層124とを備える。

(もっと読む)

不揮発性半導体記憶装置

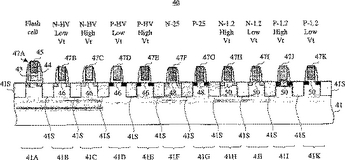

【課題】NAND型フラッシュメモリにおけるアクティブロウデコーダの端部からガードリング領域へのリーク成分を抑制し、アクティブロウデコーダ内端部のトランスファゲートトランジスタの転送能力の低下を防止し、チップの歩留まりを改善する。

【解決手段】NAND型フラッシュメモリにおいて、メモリセルアレイ10の行方向端近傍に形成され、行列状に配置された素子領域にワード線あるいは選択ゲート線に電圧を転送するためのトランスファゲートトランジスタ341 、342 が形成されたアクティブロウデコーダ40と、アクティブロウデコーダとセルアレイとの間に配置されたガードリング領域43と、ガードリング領域とアクティブロウデコーダとの間に形成されたダミー用ロウデコーダ44とを具備し、ダミー用ロウデコーダ44のダミー用素子領域45に形成されたダミー用トランスファゲートトランジスタ461 、462 のソースノードはワード線WLi 及び選択ゲート線SGD 、SGS には接続されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離領域の深さを抑制しながら耐圧の低下を抑制できるNAND型フラッシュメモリ等の半導体装置を提供する。

【解決手段】ゲート電極PGが、隣り合う素子分離膜間のアクティブエリアAA上にゲート絶縁膜11を介してゲート長方向に離間して並設されている。ゲート電極PGを構成する多結晶シリコン層14は、アクティブエリアAAの片脇に位置する素子分離膜の上面上に張り出す一端部14aと、アクティブエリアAAの逆脇に位置する素子分離膜の上面上に張り出す他端部14bとを備えており、一端部14aの長さL1と一端部14bの長さL2が互いに異なっている。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 同一半導体基板上にメモリセルとショットキーバリアダイオードを混載した、ショットキーバリアダイオードのガードリング層によって形成される寄生バイポーラトランジスタによる電流損失を抑制した高信頼度の半導体装置を提供する。

【解決手段】 第1導電型の半導体基板1上に、メモリセルを形成するためのメモリセル領域と、ショットキーバリアダイオードを形成するためのショットキーバリアダイオード領域を相互に分離して備え、メモリセルを構成するトランジスタの閾値電圧を不純物濃度により調整するためのトランジスタのチャンネル領域に形成された第1導電型の不純物拡散層5と、ショットキーバリアダイオードのショットキーバリアを形成する第1導電型と異なる第2導電型の不純物拡散層4の表面の周囲に第1導電型の不純物拡散層で形成されたガードリング層6を、同一工程で同時に形成された不純物拡散層とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】補助パターンでダミーコンタクトが形成されてもゲート電極SGとの間で短絡不良が発生するのを防止できるNAND型フラッシュメモリ装置等の半導体記憶装置を提供する。

【解決手段】ビット線コンタクト4a(CB)の形成時にマスクパターンに補助パターン4b、4cを形成する場合に、メモリセル領域MAから延長して形成される補助パターン4bの端部に位置する補助パターン4cの対応領域について、ビット線コンタクト4a(CB)を形成する領域のスペーサを除去するのと同時にその部分のスペーサを除去する。ゲート電極SLG−SLGの間のパターンニングに余裕を持たせることができ(オフセットを確保することができ)、解像した補助パターン4cの部分でダミーコンタクトホールが形成された場合でも、両脇のゲート電極SLGとの間で短絡不良が発生するのを防止することが出来る。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化に有利な、二重ウェル、及びこの二重ウェルから離れたウェルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板1内に形成された第1導電型の第1ウェル10と、第1ウェル10に形成された複数のメモリセルトランジスタQ5−1、Q5−2と、第1ウェル10の側面領域を囲む第1部分7、及び第1ウェル10の下部領域を囲む第2部分9を有し、第1ウェル10を半導体基板1から電気的に分離する第2導電型の第2ウェルと、半導体基板1内に形成された第2導電型の第3ウェル領域5と、を備える。

(もっと読む)

FLOTOX型EEPROM

【課題】Wセル方式のFLOTOX型EEPROMの設計においては、微細化のため、セルのレイアウトを工夫することが必須であるという課題があった。

【解決手段】Wセル方式のFLOTOX型EEPROMとするため、対をなす2つのフローティングゲート25a,25bと、2つのトンネルウインドウ30a,30bと、2つのソース26a,26bと、共有のコントロールゲート31と、共有のセレクトゲート32とを設けるとともに、ドレイン27も共有とした。

【効果】高信頼性設計、高耐圧設計が実現されたWセル方式のFLOTOX型EEPROMを実現できる。

(もっと読む)

半導体装置

【課題】膜厚の異なるゲート絶縁膜のトランジスタを備えると共に素子形成領域の周囲にガードリングを設ける構成で、フォトリソグラフィ工程を追加することなく、高濃度の不純物拡散領域の形成とCMP処理のディッシング対策を行えるようにする。

【解決手段】シリコン基板3のメモリセル領域1のメモリセルトランジスタ形成部分に薄いゲート酸化膜8が形成され、周辺回路領域2の高耐圧を必要とする領域に厚いゲート酸化膜12、高濃度不純物領域に対応する部分に薄いゲート酸化膜8が形成されている。ガードリング15部分に厚いゲート酸化膜12が形成され、ガードリング16、17部分に薄いゲート酸化膜8が形成されている。この構成とすることで、STI14の形成時のディッシング発生を抑制でき、高濃度不純物導入工程では、酸化膜のエッチング処理を省略でき、しかもガードリング16、17にも導入できる。

(もっと読む)

半導体記憶装置

【課題】半導体装置、特にフラッシュメモリ等の不揮発性半導体メモリの周辺回路部において抵抗素子と基板との容量を小さくすることが可能な半導体記憶装置を提供する。

【解決手段】フラッシュメモリは、半導体基板1内に形成され、素子領域を区画する素子分離絶縁膜2と、素子分離領域2により分離された素子領域3にゲート酸化膜4、フローティングゲート(FG)として機能する第1のゲート電極5、第1の絶縁膜6上に、セルトランジスタの制御ゲート(CG:ワード線)として機能する第2のゲート電極材7が形成されている。周辺回路部において、素子分離絶縁膜2上に第1の絶縁膜6を介して第2のゲート電極材からなる抵抗素子7aとを備える。抵抗素子7a下の半導体基板1の不純物濃度は、バルクと同等かあるいはバルクの不純物濃度以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】セルアレイ形成領域の活性領域もしくは浮遊ゲート電極層の形成領域を第1領域とし当該第1領域の幅寸法よりも広い幅寸法を有する領域を第2領域としたときに、第2領域の耐圧特性を向上できるようにする。

【解決手段】第2領域R2のうちの少なくとも一部の領域R2a(もしくは全領域R2)の導電層間絶縁膜5は、その膜厚が第1領域R1の導電層間絶縁膜5の膜厚に比較して厚く形成されている。これにより、第2領域の耐圧特性を向上できる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体基板に形成した溝部の側壁部分を用いる半導体記憶装置において、ワード線(ゲート電極)の加工を容易にし、高集積化を図れるようにする。

【解決手段】半導体記憶装置は、溝部1aを有する半導体基板1と、該半導体基板1に互いに間隔をおき且つ溝部1aと交差して形成された一対の不純物拡散層からなるソース・ドレイン領域11と、溝部1aの一壁面上に形成され、絶縁性を有するトラップ膜7と、半導体基板1におけるトラップ膜7と対向する領域に形成されたチャネル領域8と、溝部1aにトラップ膜7と接するように形成されたゲート電極9と、半導体基板1における溝部1aの底部又は溝部1aの下側に形成された素子分離領域6とを有している。

(もっと読む)

不揮発性半導体記憶装置

【課題】寄生バイポーラとしての動作を防止でき、かつ高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】支持基板1と埋め込み絶縁層2と半導体層3とからSOI基板が構成されている。1poly型メモリセル10は、1対のソース/ドレイン領域11と、フローティングゲート電極層13と、コントロールゲート用不純物拡散領域14とを有している。分離絶縁層6は、半導体層3の表面から埋め込み絶縁層2に達しながらコントロールゲート用不純物拡散領域14の周囲を取り囲むことで、ソース/ドレイン領域11が形成された領域とコントロールゲート用不純物拡散領域14とを分け隔てている。

(もっと読む)

トレンチに形成された選択ゲートの上に制御ゲートを備えるプログラム可能な構造

半導体記憶セルは、半導体層に形成された第1トレンチの下の第1ソース/ドレイン領域(102)を備える。第2ソース/ドレイン領域は、半導体層の第2トレンチの下に位置する。第1トレンチ(108)における第1選択ゲート(130−1)および第2トレンチ(108)における第2選択ゲート(130−2)は、選択ゲート誘電体によってライナーを施される。電荷貯蔵スタックは選択ゲートの上に位置し、制御ゲートはスタックの上に位置する。DSEは、ポリシリコンの慎重な堆積物を含んでもよい。第1および第2の選択ゲートの上面は、第1および第2のトレンチの上面より低い。制御ゲートは、選択ゲートに対し垂直に延び、選択ゲートを横切る連続した制御ゲートであってもよい。このセルは、半導体層に対する接点を含んでもよい。制御ゲートは、第1選択ゲートの上の第1制御ゲートと、第2選択ゲートの上の第2制御ゲートとを含んでよい。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 隣り合う配線間で起きやすい電気的短絡不良を抑制し、高歩留り及び高信頼性を実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体記憶装置はメモリセル部10、及びダミーセル部14、及びウエルコンタクト部12を備える。メモリセル部10は、微細な平面パターン幅のメモリセル活性領域20及びメモリセル素子分離領域18を有する。ウェルコンタクト部12は、メモリセル活性領域20よりも平面パターン幅の広いウェルコンタクト活性領域34を有する。

ダミーセル部14では、ダミーセル活性領域38及びこれを区画するダミーセル素子分離領域40の各々の平面パターン幅が最適化されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細、高集積で、素子分離能力に優れ、寄生抵抗、容量の小さいたフラッシュメモリを提供する。

【解決手段】SOI基板上にNAND型フラッシュEEPROMが形成される。素子領域(活性層)は、格子パターンで、その間の溝は、絶縁材により埋め込まれる。ロウ方向の素子同士は、完全に絶縁材により分離される。メモリセルが形成されるシリコン薄膜は、微量のn型不純物を含み、真性半導体に近い。周辺回路や選択ゲートトランジスタが形成されるシリコン薄膜は、p型である。メモリセル及び選択ゲートトランジスタの拡散層は、n型である。NANDストリングを構成する各メモリセルのチャネルは、しきい値の異なる少なくとも2つの領域から構成される。

(もっと読む)

フラッシュメモリ素子およびその製造方法

【課題】セル領域と周辺回路領域との境界部の半導体基板を第1トレンチおよび第2トレンチの形成のためのエッチング工程から保護することができ、半導体基板の損傷で発生する漏れ電流の増加を防止することができる、フラッシュメモリ素子およびその製造方法を提供する。

【解決手段】セル領域Aの素子分離膜24aを定義するためのパターンを介してパターニングし、第1トレンチを形成するが、前記セル領域Aの素子分離膜24aのパターンは境界部にも形成されるようにする段階と、前記周辺回路領域Bの素子分離膜24bを定義するためのパターンを介してパターニングし、前記第1トレンチより深い第2トレンチを形成するが、前記周辺回路領域Bの素子分離膜24bのパターンは前記境界部にも形成されるようにすることにより、前記第1トレンチおよび第2トレンチの形成のためのパターニングの際、前記境界部にダミー活性領域Cを定義する段階とを含む。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 不揮発性半導体記憶素子がマトリックス状に配置されている仮想グラウンドアレイの半導体集積回路装置において、ビット線間およびワード線間のリーク電流を効率よく抑制する。

【解決手段】 ビット線BL1〜4である拡散層とワード線WL1〜3であるゲート電極に囲まれた領域にある半導体基板の表面上に、不揮発性半導体記憶素子とは分離された状態で、シリコン酸化膜を介してシリコン窒化膜(電荷トラップ層)を形成し、さらに基板全体をプラズマ雰囲気に晒すことで、このシリコン窒化膜に電子を意図的にトラップさせる。その結果、この領域の半導体基板表面には正電荷が蓄積状態となり、ビット線間およびワード線間のリーク電流を抑制することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】コンタクトレス方式が採用されたメモリセルアレイにおける共用コンタクト領域においてリーク電流を抑制する。

【解決手段】不揮発性半導体記憶装置は、複数の埋め込み拡散ビット線2と、埋め込み酸化膜と、複数のワード線5と、ワード線5とビット線2間領域との交差領域に形成された電荷保持膜からなる複数のメモリセルと、コンタクト7を上面に有する複数の拡散層8があり、複数のブロックに区分されたビット線2同士は拡散層8を介して電気的に接続されており、コンタクト領域となる拡散層8の近傍領域に形成されたビット線2間に形成された素子分離領域9とを備える。さらに、ビット線2上及び素子分離領域9上に跨り、側壁絶縁膜を有するダミーワード線14を備え、側壁絶縁膜は、素子分離領域9と、埋め込み酸化膜と、ビット線2との境界領域上を覆う。

(もっと読む)

パンチスルー耐性を向上させた半導体集積回路装置およびその製造方法、低電圧トランジスタと高電圧トランジスタとを含む半導体集積回路装置

集積回路装置は、フラッシュメモリ素子が形成されるメモリセルウェルと、それぞれ高電圧トランジスタが形成される、互いに逆導電型の第1のウェルと第2のウェルと、それぞれ低電圧トランジスタが形成される、互いに逆導電型の第3のウェルと第4のウェルとを含み、前記第1および第2のウェルの少なくとも一方、および前記第3および第4のウェルの少なくとも一方は、前記メモリセルウェルの不純物濃度分布プロファイルよりも急峻な不純物濃度分布プロファイルを有する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

所望の特性を果たす複数種類のトランジスタを少ない工程数で製造する。 半導体装置は、第1の深さに達する素子分離領域と、第1導電型の第1および第2のウェルと、第1のウェルに形成され、第1の厚さのゲート絶縁膜と、第2導電型のソース/ドレイン領域およびゲート電極とを有する第1のトランジスタと、第2のウェルに形成され、第1の厚さより薄い第2の厚さのゲート絶縁膜と、第2導電型のソース/ドレイン領域およびゲート電極とを有する第2のトランジスタと、を有し、第1のウェルは、第1の深さと同等又はより深い深さにのみ極大値を有する第1の不純物濃度分布を有し、第2のウェルは、第1のウェルと同一の第1の不純物濃度分布に第1の深さより浅い第2の深さに極大値を有する不純物濃度分布を重ね合わせ、全体としても第2の深さにも極大値を示す第2の不純物濃度分布を有する。  (もっと読む)

(もっと読む)

1 - 20 / 21

[ Back to top ]