Fターム[5F102GB05]の内容

接合型電界効果トランジスタ (42,929) | 主電流経路 (2,759) | 基板表面に垂直(縦型FET) (311) | メサ側面を流れるもの (36)

Fターム[5F102GB05]に分類される特許

1 - 20 / 36

炭化珪素半導体装置およびその製造方法

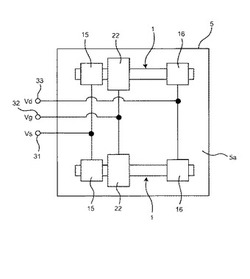

トランジスタ装置および電子デバイス

【課題】1本の棒状素子が破壊しても、他の棒状素子が正常に動作し、正常動作を続けるトランジスタ装置を提供する。

【解決手段】トランジスタ装置は、基板5と、この基板5上に配置された2本の棒状素子1とを有する。このため、一方の棒状素子1が破壊しても、他方の棒状素子1が正常に動作し、トランジスタ装置は、正常動作を続ける。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

窒化物半導体電子デバイス、窒化物半導体電子デバイスを作製する方法

【課題】チャネルリークを低減可能な窒化物半導体電子デバイスが提供される。

【解決手段】

【0097】ヘテロ接合トランジスタ11によれば、電流ブロック層27はp導電性を有する。ドープ半導体層17が開口部16の側面16aに設けられると共にドープ半導体層17が電流ブロック層27とチャネル層19との間に設けられるので、チャネル層19が、エッチングの際に開口部16の側面16aに形成されている可能性があるドナー性欠陥を含む半導体に直接に接触することがない。また、ドープ半導体層17は、電流ブロック層27とチャネル層19との間に設けられると共にチャネル層19はキャリア供給層21とドープ半導体層17との間に設けられるので、ドープ半導体層17の追加により、チャネル層19及びキャリア供給層21の配列は変更されることがない。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置

【課題】ソース・ゲート間およびドレイン・ゲート間に発生する2次元電子ガスの濃度を最適にしたまま、オン抵抗を低くして、消費電力の低い半導体装置を提供する。

【解決手段】第2のAlGaN層6のAlの組成比は、第1のAlGaN層5のAlの組成比よりも大きい。このため、ゲート電極8に電圧を印加したとき、GaN層3の凹溝30の内面の側面31と第2のAlGaN層6との第1の界面S1に2次元電子ガスを発生させつつ、第2のAlGaN層6における凹溝30の内面の側面31に平行な部分と絶縁層7との第2の界面S2に2次元電子ガスを発生させることを抑制できる。

(もっと読む)

半導体ヘテロ電界効果トランジスタ

【課題】ピエゾ電界により発生するシートキャリアの利用とチャネル部におけるピエゾ電界により深いディプレッション形成の抑制とを提供できる半導体ヘテロ電界効果トランジスタを提供する。

【解決手段】第1及び第3の領域23a、23cの主面24a、24cの法線ベクトルNV1、NV3は、該III族窒化物半導体のc軸Cxに直交する面に対して有限な角度で傾斜する。第2の領域23bの主面24bの法線ベクトルNV2は、該III族窒化物半導体のc軸Cxに直交する面に沿って延在する。第2の領域23bにおけるチャネル層25の第2の領域25bのピエゾ分極PZC2は、III族窒化物半導体領域23からバリア層27への方向に向いている。第1及び第3の領域23a、23cにおけるチャネル層25の第1及び第3の領域25a、25cのピエゾ分極PZC1、PZC3は、バリア層27からIII族窒化物半導体領域23への方向に向いている。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

ヘテロ接合トランジスタ、及びヘテロ接合トランジスタを作製する方法

【課題】チャネル層内の抵抗の不均一を避けることを可能にする構造を有するヘテロ接合トランジスタを提供する。

【解決手段】半導体積層15が、半極性を示すIII族窒化物主面13a上に設けられ、半導体積層15が主面13aに到達する開口16を有する。開口16の側面16aは、III族窒化物半導体のa面に対して大きな角度を成すと共にIII族窒化物半導体のm面に対しても大きな角度を成して、III族窒化物半導体のc面に非常に近い面から構成される。開口16の側面16aの傾斜角は、m面やa面よりもc面に近い。この開口16の側面16aにドリフト層17及びチャネル層19が成長されるので、その成長中に不可避的に取り込まれる不純物量を小さくできる。これ故に、ドリフト層17及びチャネル層19における抵抗の不均一を避けることができる。

(もっと読む)

電界効果トランジスタの製造方法

【課題】ゲート長が短い電界効果トランジスタを低コストで製造できる電界効果トランジスタの製造方法を提供すること。

【解決手段】基板上に、窒化物系化合物半導体からなるチャネル層および該チャネル層上に積層した上部層を含む半導体層を形成する工程と、半導体層の一部領域を少なくとも上部層からチャネル層に到る深さまでエッチングして、該チャネル層の表面の一部を底面部とし、エッチングによって露出した半導体層の側面を側壁部とする段差部を形成する工程と、段差部を含む半導体層の表面を覆うようにマスク層を形成し、該マスク層をエッチバックして該段差部のマスク層を残留させたマスク部を形成する工程と、イオン注入法によって、底面部のマスク部を除く領域にコンタクト領域を形成する工程と、マスク部を除去した後に、少なくとも段差部の底面部と側壁部とを覆うようにゲート絶縁膜およびゲート電極を順次形成する工程と、を含む。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】 パワーデバイスに必要な特性を確保しながら、コストを低減することができる窒化物半導体素子およびその製造方法を提供すること。

【解決手段】 CAVET1において、シリコン基板2上に、AlN構造8を有するバッファ層4、電子走行層6、および電子供給層7を積層した構造を有し、電子走行層6および電子供給層7に跨る壁面16を有する積層構造部3を形成する。バッファ層4と電子走行層6との間には、開口部13を有するマスク層12を形成する。ソース電極18は、電子供給層7上に形成し、ゲート電極20は、電子供給層7上におけるソース電極18よりも壁面16寄りの位置に設ける。ドレイン電極30は、シリコン基板2の裏面22側からシリコン基板2およびバッファ層4を貫通するように設ける。そして、壁面16に沿って埋込電極17を設け、開口部13を介してドレイン電極30に電気的に接続する。

(もっと読む)

窒化物半導体素子

【課題】本発明は、低オン抵抗でノーマリーオフ型の窒化物半導体素子を提供する。

【解決手段】本発明の一態様によれば、p型窒化物半導体の第1の半導体層と、第1の半導体層上に設けられたアンドープ窒化物半導体の第2の半導体層と、第2の半導体層上に選択的に設けられたアンドープまたはn型窒化物半導体の第3の半導体層と、第3の半導体層上に設けられた第1の主電極と、第3の半導体層上に設けられた第2の主電極と、第2の半導体層上に設けられた絶縁膜と、絶縁膜上に設けられた制御電極と、を備え、第3の半導体層のバンドギャップは、第2の半導体層のバンドギャップよりも大きく、制御電極は、第1の主電極と第2の主電極との間に位置することを特徴とする窒化物半導体素子が提供される。

(もっと読む)

半導体装置の製造方法

【課題】安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上にGaN系半導体層を形成する工程と、ALD装置内で、ゲート絶縁膜の成長温度に比べ高い温度で熱処理を実施し、前記GaN系半導体層の表面のフッ素を除去する工程S20と、前記フッ素を除去する工程S20の後、前記ALD装置内で、前記GaN系半導体層の表面に前記ゲート絶縁膜を形成する工程S16と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

1 - 20 / 36

[ Back to top ]