Fターム[5F102GL04]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 3−5族 (2,210)

Fターム[5F102GL04]の下位に属するFターム

GaAs (175)

Fターム[5F102GL04]に分類される特許

1 - 20 / 2,035

ヘテロ接合電界効果型トランジスタおよびその製造方法

電界効果トランジスタ

評価方法

化合物半導体装置及びその製造方法

半導体装置、高電子移動度トランジスタ、および、複数のチャネルによりソースからドレインに電子を送るための方法

高電子移動度トランジスタ構造及び方法

パワートランジスタ装置のための多層構造を作製する方法、ヘテロ接合電界効果トランジスタ装置のための多層構造を作製する方法、および窒化物系ヘテロ接合電界効果トランジスタ装置

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

高周波半導体装置

【課題】半導体チップを実装できる幅を増大し、実装基板上を有効に使用可能な高周波用半導体装置を提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置されたマルチセル構成の半導体チップと、導体ベースプレート上に配置され、半導体チップを内在する矩形のキャビティを形成する金属壁と、金属壁の入出力部に設けられた貫通孔とを備え、半導体チップを、金属壁に囲まれた矩形のキャビティ内において、半導体チップの長手方向が、貫通孔の設けられていない金属壁の延伸方向から0度より大で、90度より小の所定の角度に配置した半導体装置。

(もっと読む)

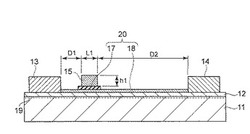

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置とその製造方法

【課題】特性ばらつきの少ない絶縁ゲートを備えた窒化物半導体の半導体装置を提供すること。

【解決手段】 半導体装置が備える絶縁ゲートは、窒化物半導体層1上に設けられているアモルファスの酸化シリコン膜2と、酸化シリコン膜2上に設けられているゲート電極8を有している。ゲート電極8に対向する窒化物半導体層1が酸化されている。

(もっと読む)

高周波半導体装置

【課題】ボンディングワイヤの長さを長くすることなくインダクタンスの値を大きくできる高周波用半導体装置を提供する。

【解決手段】高周波半導体装置1は、マルチセル構成の半導体チップ24と、整合回路と、半導体チップ24と整合回路間に並列に接続された複数本のボンディングワイヤ12、14とを備え、複数本のボンディングワイヤ12、14は、半導体チップ24に対して平面上で90°以下の所定の角度を有する。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

窒化物半導体装置

【課題】櫛型形状のソース電極とドレイン電極が交差指状に配置された電極構造を有し、各櫛形電極の先端部での電界集中が緩和された窒化物半導体装置を提供する。

【解決手段】ゲート電極5と電気的に接続され、ゲート電極5とドレイン電極4間で絶縁膜7上に配置されたゲートフィールドプレート50と、ソース電極3と電気的に接続され、絶縁膜8を介して窒化物半導体層と対向するようにゲートフィールドプレート50とドレイン電極4間の上方に配置されたソースフィールドプレート30とを備え、ゲート電極5とドレイン電極4間の距離、ゲートフィールドプレート50のドレイン側端部とゲート電極5のドレイン側端部間の距離、及びソースフィールドプレート30のドレイン側端部とゲートフィールドプレート50のドレイン側端部間の距離の少なくともいずれかが、ソース電極3とドレイン電極4の、歯部分の直線領域よりも歯部分の先端領域において長い。

(もっと読む)

半導体装置の製造方法

【課題】GaN系半導体を用い耐圧の異なるトランジスタを作り分ける。

【解決手段】基板1上方に第1、第2GaN系半導体層3,4、電極層5、第1絶縁膜6を積層し、電極層5及び第1絶縁膜6をパターニングして、第1ゲート電極5と第1絶縁膜6が積層された第1構造と、第2ゲート電極5と第1絶縁膜6が積層された第2構造を形成し、第1、第2構造を覆って第2絶縁膜7を形成し、第1ゲート電極5とその両側領域を露出する第1開口8SD、第2ゲート電極5を挟んでそれぞれ一方側、他方側に配置された第2、第3開口8S,8Dを有する第1マスクを用いて、第2絶縁膜7を異方性エッチングし、第1開口内8SDにおいて、第1構造の側面上にサイドウォール絶縁膜7SWを残しつつ、第1ゲート電極を挟んでコンタクトホール9S,9Dを形成し、第2、第3開口内に、それぞれコンタクトホール9S,9Dを形成し、各コンタクトホールに電極を形成する。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

1 - 20 / 2,035

[ Back to top ]