Fターム[5F102GL17]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 材質が不均質なもの (162) | 厚さ方向(基板垂直)に変化 (41)

Fターム[5F102GL17]に分類される特許

21 - 40 / 41

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

窒化物系半導体ウエハ及び窒化物系半導体デバイス

【課題】高い絶縁性を有する窒化物系半導体層を有する窒化物系半導体ウエハを安定的に提供する。

【解決手段】絶縁性基板上に、抵抗率が10MΩcm以上100MΩcm以下、膜厚が0.1μm以上1.5μm以下である半絶縁性窒化物系半導体層を有する。

(もっと読む)

窒化物半導体エピタキシャルウェハおよびその製造方法ならびに電界効果型トランジスタ素子

【課題】 高耐圧化とカレントコラプス現象の低減ないしは解消との両立を可能とした窒化物半導体エピタキシャルウェハおよびその製造方法ならびに電界効果型トランジスタ素子を提供する。

【解決手段】 基板1と、前記基板1の上に形成された第1の窒化物半導体層3と、前記第1の窒化物半導体層3の上に形成された、前記第1の窒化物半導体層3よりも電子親和力の小さい第2の窒化物半導体層5とを有し、前記第1の窒化物半導体層3には、その表面から深さ方向に、近似式;NFe=A×exp(B×C)、(NFe:第1の窒化物半導体層における鉄濃度、A:1E14〜1E17[cm−3]、B:3〜8[μm−1]、C:第1の窒化物半導体層における表面からの深さ)によって表わされる深さ方向プロファイルで鉄がドーピングされており、かつ前記第1の窒化物半導体層の表面側には、前記鉄の濃度よりも高い濃度でシリコンをドーピングしてなるシリコンドーピング領域4が設けられている。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】基板の放熱性が高くて基板に形成される窒化物半導体層の結晶欠陥が少ない窒化物半導体装置及びその製造方法を提供する。

【解決手段】

HEMT10の製造方法は、サファイア基板11の表面にGaNの薄膜12を形成する成膜工程と、薄膜12の上端からサファイア基板11の内部に達する深さの溝を形成する溝形成工程と、溝形成工程の後に、薄膜12を種結晶としてGaN層13を成長させる成長工程と、成長工程の前又は後に、サファイアよりも熱伝導性が高い高熱伝導性材料としてのAuを溝17に充填する充填工程とを備えている。

(もっと読む)

電子デバイス用エピタキシャル基板およびその製造方法

【課題】横方向リーク電流の低減と横方向耐圧特性を両立させ、縦方向耐圧を向上させる電子デバイス用エピタキシャル基板を提供する。

【解決手段】Si基板1上のバッファ3上にIII族窒化物層をエピタキシャル成長させた、チャネル層4aおよび電子供給層4bを有する主積層体4を具え、前記バッファは、Si基板と接する初期成長層5および初期成長層上の超格子多層構造からなる超格子積層体6を有し、初期成長層はAlN材料からなり、前記超格子積層体はBa1Alb1Gac1Ind1N材料からなる第1層6aおよび第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N材料からなる第2層6bを積層してなり、前記超格子積層体と、前記主積層体を構成するチャネル層のバッファ側の部分は、C濃度が1×1018/cm3以上であり、チャネル層の電子供給層側の部分は、C濃度が4×1016/cm3以下であることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】ノーマリオフ型動作を実現しながら、寄生抵抗が小さい電界効果トランジスタを得られるようにする。

【解決手段】電界効果トランジスタは、基板1の上に形成された、GaNからなるバッファ層2と、該バッファ層2の上に形成された、InxAlyGa1−x−yN(但し、0≦x≦1、0≦y≦1、0<x+y≦1)からなる電子供給層3と、該電子供給層3の上に形成され、電子供給層3とは異なる組成を有し且つ高濃度のn型不純物が添加された、InsAltGa1−s−tN(但し、0≦s≦1、0≦t≦1、0≦s+t≦1)からなるキャップ層4とを有している。キャップ層4にはリセス4aが形成されており、キャップ層4におけるリセス4aの両側方の領域には、ソース電極5及びドレイン電極7が形成され、キャップ層4のリセス4aには、ゲート電極6が絶縁膜8を介在させて形成されている。

(もっと読む)

ヘテロ接合電界効果トランジスタ、その製造方法

【課題】ゲート電極下の電子の走行方向が基板表面に略平行であるようにデバイス構造を改良しながらも各種弊害を解消したヘテロ接合電界効果トランジスタを提供する。

【解決手段】n型導電層は選択的にイオン注入されているシリコン(Si)などのn型不純物をアニール処理で活性化することにより形成されており、n型導電層は、イオンが200keV以上の加速エネルギーで注入されており、p型窒化物半導体層より深く、かつドレイン電極114と導通する半導体層にまで注入イオンが達する選択的イオン注入によって形成されており、n型導電層とn型不純物が注入されていないチャネル領域との接続部115に注入されているn型不純物濃度が1×1018cm−3以下である。

(もっと読む)

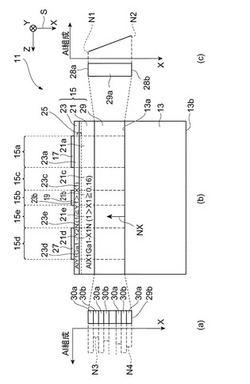

化合物半導体装置及びその製造方法

【課題】縦型構造のHEMTにおけるオン抵抗を低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1の上方に形成された電子供給層4及び電子走行層2と、電子供給層4及び電子走行層2の上方に形成されたソース電極21s及びゲート電極21gと、基板1の裏面に形成されたドレイン電極21dと、が設けられている。そして、電子供給層4の少なくとも一部と電子走行層2の少なくとも一部とが、基板1の表面に平行な面から傾斜した面を境にして互いに接している。

(もっと読む)

半導体装置とその製造方法

【課題】 転位の発生を抑制しながら、p型半導体領域に含まれるp型不純物が隣接する他の半導体領域に拡散する現象を抑制する技術を提供する。

【解決手段】 Mg(p型不純物)を含む窒化ガリウムのp型半導体領域24と、窒化ガリウムのn型半導体下領域20と、p型半導体領域24とn型半導体下領域20との間に設けられている不純物拡散抑制領域22を備えている。不純物拡散抑制領域22は、Inx1Al1-x1N(但し、0<X1<1)である。

(もっと読む)

半導体装置

【課題】化合物半導体機能層に生成される二次元キャリアガスチャネルにおいてキャリア密度及び電界をキャリア走行方向に変調する半導体装置を提供する。

【解決手段】半導体装置(HEMT)1において、二次元キャリアガスチャネル23を有する第1の化合物半導体層21と、第1の化合物半導体層21上に配設され、バリア層として機能する第2の化合物半導体層22と、二次元キャリアガスチャネル23の一端に接続された第1の主電極3と、二次元キャリアガスチャネル23の一端に離間する他端に接続された第2の主電極4とを備え、第1の主電極3と第2の主電極4との間において、第2の化合物半導体層22の組成元素の組成比が二次元キャリアガスチャネル23方向に異なる。

(もっと読む)

半導体装置

【課題】所望のキャリア移動度、ドレイン電流を得ることができ、高出力動作することができる、かつ、ゲートの漏れ電流を減少することができるMESFETを用いた半導体装置を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置20は、第1導電型の半導体基板2と、半導体基板2上に形成され、第2導電型の半導体層よりなるドレイン領域3およびソース領域3と、半導体基板2上であってドレイン領域3とソース領域3の間に形成され、第2導電型の2層以上の半導体層よりなるチャネル領域4と、チャネル領域4上に形成され、チャネル領域4とショットキー接触をなすゲート電極5とを備える。

(もっと読む)

半導体装置

【課題】良好なトランジスタ特性を保ちつつ衝突イオン化により生成した正孔を外部に放出することができる半導体装置を提供する。

【解決手段】基板100と、基板100上に設けられたIII族窒化物半導体多層膜と、III族窒化物半導体多層膜の上部に設けられた、ゲート電極112、ソース電極110およびドレイン電極114とを備え、III族窒化物半導体多層膜は、正孔走行層104、電子走行層106および電子供給層108を含み、正孔走行層104とゲート電極112とが導電体により電気的に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリオフ特性を有することをはじめ良好な電気特性を有する半導体装置を提供する。

【解決手段】ヘテロ界面135において2次元電子ガス層137を生じている半導体基体に、ソース電極151を、2次元電子ガス層137との接触部171が生じる深さまで埋め込む。そして、該接触部の上方にゲート電極153が位置するようにする。これにより、良好な電気特性を得る。ソース電極151は半導体基体とショットキー接合しているため、ドレイン電極155に電圧を印加してもノーマリオン特性は生じない。

(もっと読む)

III族窒化物系化合物半導体縦型トランジスタ及びその製造方法

【課題】新規なIII族窒化物系化合物半導体縦型トランジスタを提供する。

【解決手段】n型Si基板31上に、Al/Ti/Pt/Au多重金属層32、AuSnはんだ層33、Au/Ni/Al/Ti多重金属層15、n+コンタクト層(n+−GaN)14、ドリフト部(n−GaN)13が形成されている。ドリフト部13は、厚さ約0.5μmの電流狭窄部13bnを有しており、その左右には、AlN層21とp層(p−GaN)22が形成されている。ドリフト部13(電流狭窄部13bn)の最上部と、p層(p−GaN)22の最上部は同一平面となっている。それらの上には、チャネル層(n−GaN)12、電子供与層(AlGaN)11が形成されている。HEMT100は、サファイア基板にエピタキシャル成長させた後、シリコン基板を貼り付けてレーザーリフトオフ法でサファイア基板を除去すると得られる。

(もっと読む)

高電子移動度トランジスタ用エピタキシャルウェハ及び高電子移動度トランジスタ

【課題】高電子移動度トランジスタ用エピタキシャルウェハの格子不整合を解消して、このウェハから作製される高電子移動度トランジスタのソース電極−ドレイン電極間の縦方向抵抗を低減する。

【解決手段】GaAs基板1上に、AlGaAs又はGaAsの電子供給層3とInGaAsのチャネル層4とを有する高電子移動度トランジスタ用エピタキシャルウェハWにおいて、電子供給層3とチャネル層4との間に、チャネル層4側から電子供給層3側へIn組成を徐々に小さくしたグレーデッドInGaAs電子供給層7又は8が設けられている。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、容易にノーマリオフとなる半導体装置を実現すること。

【解決手段】半導体装置は、n−GaN層11、n−GaN層11上にp−GaN層12とn−GaN層13、p−GaN層12上にn- −GaN層14、n−GaN層13上にn−GaN層21、で構成されている。n- −GaN層14の不純物濃度を低くすることで、ノーマリオフを容易にしている。また、n−GaN層13とn−GaN層21の不純物濃度を高くすることで、オン抵抗を低くしている。

(もっと読む)

ミリメートル波動作のための窒化物ベースのトランジスタ

【課題】ミリメートル波動作のために設計された広バンドギャップのトランジスタの提供。

【解決手段】第III族窒化物チャネル層と;第III族窒化物チャネル層の上のスペーサ層と;第III族窒化物チャネル層の上にあり、かつ30GHzを超える周波数において印加される電圧に応じてチャネル層の伝導率を変調するのに十分なゲート長を有するゲート接点と;ゲート接点と電気的に接続され、スペーサ層を横断してドレイン接点に向かう方向に少なくとも約0.1μm延びる下部フィールドプレートと;第III族窒化物チャネル層の上のソース接点およびドレイン接点とを含み、少なくとも30GHzの周波数における動作時に約5W/mmより大きな電力密度を示すことを特徴とする電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ、半導体素子、及びエピタキシャル基板

【課題】 ショットキ接合電極からのリーク電流が低減される電界効果トランジスタ及び半導体素子を提供する。また、ショットキ接合電極からのリーク電流が低減される電界効果トランジスタまたは半導体素子を作製するためのエピタキシャル基板を提供する。

【解決手段】 HEMT1は、支持基体3と、支持基体3上に設けられたGaN系化合物層5と、GaN系化合物層5上に設けられたAlXGa1−XN(0<X<1)層7と、AlXGa1−XN層7にショットキ接合を成すゲート電極9と、AlXGa1−XN層7上に設けられたソース電極11及びドレイン電極13とを備える。そして、GaN系化合物層5は、GaN結晶からなる高純度GaN層5aと、AlドープGaN層5bとを含む。AlドープGaN層5bにおけるAl濃度は、2×1020cm−3以上5×1021cm−3以下である。

(もっと読む)

半導体装置形成用ウエハ、その製造方法、および電界効果型トランジスタ

【課題】オフ耐圧を従来よりも高めることで、大きな出力電力を得ること。

【解決手段】基板12と、基板の主面12a側に形成されたGaNからなる電子走行層16と、電子走行層上に形成されたAlGaNからなる電子供給層18とを備え、電子走行層の厚みが、0.2〜0.9μmであることを特徴とする。

(もっと読む)

電界効果トランジスタ用エピタキシャルウェハ及びそれから作製した電界効果トランジスタ

【課題】InGaAsチャネル層とAlGaAsキャリア供給層の間の構造を工夫することにより、電界効果トランジスタ用エピタキシャルウェハ又は電界効果トランジスタのチャネル電子移動度とシートキャリア濃度を向上させることを可能にする。

【解決手段】半絶縁性基板上に少なくともAlGaAsキャリア供給層とInGaAsチャネル層を有する電界効果トランジスタ用エピタキシャルウェハにおいて、InGaAsチャネル層とAlGaAsキャリア供給層の間に、InGaAsチャネル層に接するかたちで、In組成を徐々に変化させたグレーデッドInGaAsスペーサ層を挿入し、このグレーデッドInGaAsスペーサ層のIn組成を、InGaAsチャネル層から遠ざかる方向にチャネルIn組成から0まで変化させた構造とする。

(もっと読む)

21 - 40 / 41

[ Back to top ]