Fターム[5F102GN01]の内容

接合型電界効果トランジスタ (42,929) | 表面半導体層(ゲートメタル電極底面より高い位置にある層) (914) | 単一半導体層 (704)

Fターム[5F102GN01]の下位に属するFターム

Fターム[5F102GN01]に分類される特許

1 - 7 / 7

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で、シート抵抗及びゲートリーク電流の増加、出力の低下等の不都合を生ぜしめることなく、所期のノーマリ・オフを実現する。

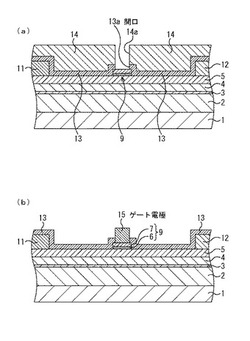

【解決手段】化合物半導体層が電子走行層2、中間層3、電子供給層4、及びキャップ層5を有して構成され、キャップ層5上にゲート絶縁膜9を介してゲート電極15が形成されており、ゲート絶縁膜9は、キャップ層5の表面に酸素プラズマが照射されて形成されたGa2O3を含む極性反転層6と、極性反転層6の存在でO極性のZnOとなった逆極性層7とが積層されてなる。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】窒化物系III‐V化合物半導体からなるHFETのノーマリオフ化を図る。

【解決手段】GaNチャネル層3上に積層されたAl0.2Ga0.8N障壁層4に大きさおよび形状がランダムに形成された凹部8内を埋めるようにゲート電極7を形成している。こうして、2次元電子ガス(2DEG)が発生する面積を減少させ、全体の2DEG密度を低減させて、ノーマリオフ化を図ることができる。その際に、AlGaN障壁層4における転位部分(結晶欠陥部分)を選択的にウェットエッチングすることにより、ダメージを生じさせることなく大きさおよび形状がランダムな凹部8を形成し、チャネル移動度の低下を抑制してチャネル領域でのオン抵抗の増大を防止する。

(もっと読む)

半導体素子

【課題】ドナー元素を含む半導体層を備えた半導体素子を形成する場合に、このドナー元素が上層に拡散することを抑制することができる半導体素子を提供する。

【解決手段】ZnO基板上にGaドープMgZnO層、アンドープMgZnO層、窒素ドープMgZnO層、アンドープ活性層、窒素ドープMgZnO層と積層した積層体でGaの拡散を分析した。アンドープMgZnO層の次の窒素ドープMgZnO層で、拡散してきたGaの濃度が表面側になるにつれて、急激に減少しており、この窒素ドープMgZnO層の上層にGaは拡散していない。このように、ドナー元素を含む同一組成のドナー含有半導体層の一部に、アクセプタ元素を含み前記ドナー含有半導体層と同一組成のアクセプタ含有半導体層を形成することで、ドナー元素の拡散を防止できる。

(もっと読む)

ZnO系トランジスタ

【課題】高性能、高品質のチャ領域を構成することができるZnO系トランジスタを提供する。

【解決手段】MgZZnO基板1上に、MgXZnO層2、MgYZnO層3が積層されている。MgXZnO層2とMgYZnO層3の界面で2次元電子ガスが発生する。4はゲート絶縁膜又は有機物電極であり、MgYZnO層3に接して形成されている。ゲート絶縁膜又は有機物電極4上にはゲート電極5が、ドナードープ部3a上には各々ソース電極6、ドレイン電極7が形成されている。このように、トランジスタのチャネル領域をMgZnO層で形成する。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】ソース/ドレイン電極の下側のポテンシャル障壁を低くして、ソース/ドレイン電極下側の寄生抵抗を低減することを目的とする。

【解決手段】本発明に係るヘテロ接合電界効果型トランジスタは、窒化物半導体からなるヘテロ接合電界効果型トランジスタであって、チャネル層30と、チャネル層30上にスペーサ層40を介して形成されたバリア層50とを備える。バリア層50上に形成されたゲート電極80と、バリア層50上に、ゲート電極80を挟んで形成されるソース/ドレイン電極70とを備える。そして、ソース/ドレイン電極70下側の少なくとも一部の領域、例えば、バリア層50、スペーサ層40、チャネル層30のに形成されるn型不純物領域90を備える。

(もっと読む)

ヘテロ接合電界効果トランジスタの製造方法

【課題】窒化ガリウム系化合物半導体層を備え、ノーマリオフ化したヘテロ接合電界効果トランジスタを簡略に製造する方法を提供することを課題とする。

【解決手段】基板上に半導体層を備え、前記半導体層が基板側から、窒化ガリウム系化合物半導体からなるチャネル層と、障壁層とをこの順で備え、前記半導体層上にソース電極及びドレイン電極と、前記ソース電極と前記ドレイン電極間に位置するゲート電極とを備えたヘテロ接合電界効果トランジスタの製造方法であって、前記半導体層が、フッ素系ガスプラズマによる処理に付されて、ドライエッチングされ、かつフッ素導入され、前記ドライエッチングにより、処理前の半導体層の表面から障壁層の下面までの厚さの10%以上の厚さで半導体層が除去されることを特徴とするヘテロ接合電界効果トランジスタの製造方法により上記課題を解決する。

(もっと読む)

ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ

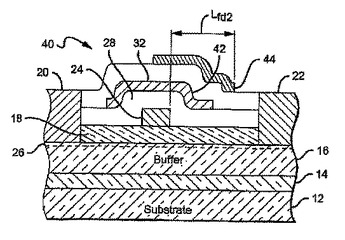

本発明に係るトランジスタは、チャネル層を有する活性領域を含み、この活性領域と接触してソースおよびドレイン電極が形成され、このソース電極とドレイン電極との間にあって活性領域と接触したゲートが形成される。ゲートとドレイン電極との間およびゲートとソース電極との間の複数の活性領域の表面の少なくとも一部分上にスペーサ層がある。このスペーサ層上にはフィールドプレートがあり、活性領域の上のスペーサ上をドレイン電極に向かって延びる。このフィールドプレートはさらに、活性領域の上のスペーサ層上をソース電極に向かって延びる。少なくとも1つの導電性経路が、フィールドプレートをソース電極またはゲートに電気的に接続する。  (もっと読む)

(もっと読む)

1 - 7 / 7

[ Back to top ]