Fターム[5F102GT01]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688)

Fターム[5F102GT01]の下位に属するFターム

Al (180)

高融点金属(Mo、Ti、Ta、W、Cr、Nb、Hf、V、Zr) (912)

合金 (49)

Fターム[5F102GT01]に分類される特許

161 - 180 / 547

窒化物半導体装置及びその製造方法

【課題】ノーマリオフ特性が安定的に得られる窒化物半導体装置を提供すること。

【解決手段】基板1と、基板1上に形成され、且つ、ヘテロ接合界面22aを有する窒化物半導体層2と、窒化物半導体層2に形成されたリセス3と、を備える窒化物半導体装置であって、

窒化物半導体層2は、基板1上に形成されたAlx1Inx2Ga1−x1−x2N(0≦x1<1、0≦x2≦1、0≦(x1+x2)≦1)からなるキャリア走行層22と、キャリア走行層22上に形成されたAlyGa1−yN(0<y≦1、x1<y)からなる第1の層231、第1の層231上に形成されたGaNからなる第2の層232、及び、第2の層上に形成されたAlzGa1−zN(0<z≦1、x1<z)からなる第3の層233を有するキャリア供給層23と、を備え、

凹部3は、第3の層233を貫通し、凹部底面31において第2の層232の主面が露出するように形成される。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】工程増を最小限とした簡便な手法で、基板に反りを生ぜしめることなく、また基板上方の化合物半導体層の結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い装置構成を得る。

【解決手段】SiC基板1上の素子分離領域に相当する部位にマスク2を形成し、マスク2を覆うようにSiC基板1上に緩衝層3を第1の温度で形成し、第1の温度より高い第2の温度で加熱処理して緩衝層3のうちSiC基板1上の部位を結晶化し、緩衝層3の上方に化合物半導体層10を形成して、化合物半導体層10のマスク2の上方に相当する部位を素子分離領域とする。

(もっと読む)

窒化物半導体装置

【課題】シリコン基板の上に形成され、優れた高周波特性を有する窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、シリコン基板101と、シリコン基板101の上に形成された窒化物半導体からなるバッファ層102と、バッファ層102の上に形成された窒化物半導体からなる能動層103とを備えている。バッファ層は、シリコン基板101と接して形成された第1の層121と、第1の層121及び能動層103と接して形成された第2の層122とを含む。第1の層121と第2の層122との界面における炭素濃度は、1×1019原子/cm3以上且つ1×1021原子/cm3以下であり、第2の層122は、炭素濃度が第1の層121と接する部分において最も高く、能動層103と接する部分において最も低い。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合FETは、窒化物半導体からなるヘテロ接合FETであって、バリア層40とバリア層40の上に形成されたキャップ層50を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極100と、ゲート電極100の両側に離間して半導体層上に夫々設けられたソース電極80及びドレイン電極90とを備える。キャップ層50は、少なくとも表面側で、少なくともゲート電極100のドレイン電極90側の側面に接する領域に、アクセプタ準位を形成する不純物がドーピングされるドーピング領域60を備える。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】 第1半導体層と第2半導体層とのヘテロ接合により第1半導体層に二次電子ガス層を生じさせつつ、ソース電極とドレイン電極との間の通電状態を切り換えるためのゲート電圧のしきい値を所定の値に調整することができる電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタ10では、サファイア基板11上に、i型のGaNからなるGaN層13と、i型のGaNと格子定数が異なるi型のAlGaNからなるAlGaN層14と、i型のAlGaNよりもエッチングレートが小さいi型のAlInNからなるAlInN層15とが順に形成されている。AlInN層15の上端から途中まで伸びている溝25が形成されており、その溝25の底部の少なくとも一部にゲート電極26がショットキー接続されている。

(もっと読む)

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数に分割された接続部とこれらの接続部の間に形成された抵抗体とが、電極パッドにより良好に接続される半導体装置の製造方法を提供すること。

【解決手段】複数のFET12が化合物半導体基板11上に並列に形成され、ゲートパッド27が複数に分割された半導体装置の製造方法であって、化合物半導体基板11上に抵抗体22を形成する工程と、抵抗体22上にこの抵抗体22を保護する保護パターン23を形成する工程と、複数のFET12、抵抗体22および保護パターン23を含む化合物半導体基板11上に保護膜24を形成する工程と、複数のFET12の各電極13、14、15をそれぞれ接続する電極接続部17、18、21上および保護パターン23上の保護膜24をエッチングにより除去する工程と、エッチングにより除去した位置に電極パッド25、26、27を形成する工程と、を具備する。

(もっと読む)

半導体装置

【課題】電界緩和効果が大きいフィールドプレート構造を有する半導体装置を提供する。

【解決手段】半導体装置10は、基板11上に形成された窒化物半導体層と、窒化物半導体層と電気的接触をして形成されたソース電極15と、窒化物半導体層と電気的接触をして形成されたドレイン電極16と、ソース電極とドレイン電極との間の窒化物半導体層上に形成されたゲート電極17と、ゲート電極とドレイン電極との間の窒化物半導体層の表面に形成されたキャップ層18と、キャップ層を覆うパシベーション層19と、キャップ層18とパシベーション層19から成る層の上にゲート電極の一部として形成されたフィールドプレート20と、を備え、キャップ層は、窒化物半導体層の材料の組成の一部の組成を含む組成から成る材料から成り、2〜50nmの厚さを有し、キャップ層のゲート電極側の端部には、60°以下のテーパ角が設けられ、斜面が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

へテロ接合電界効果トランジスタ及びその製造方法

【課題】ゲートリーク電流の増大を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明の窒化物半導体からなるヘテロ接合電界効果トランジスタは、バリア層4と、バリア層4上に設けられたキャップ層5と、キャップ層5に下部を埋没するようにしてキャップ層5上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたソース電極9及びドレイン電極8と、を備える。ゲート電極10とドレイン電極8の間である第1領域及びゲート電極10とソース電極9の間である第2領域のうち、少なくとも第1領域のキャップ層5において少なくとも1箇所にトレンチが形成される。

(もっと読む)

縦型パワートランジスタ装置、半導体チップ、および縦型パワートランジスタ装置の製造方法

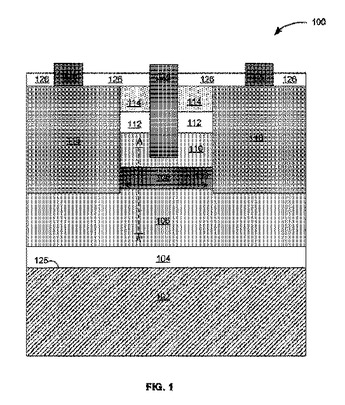

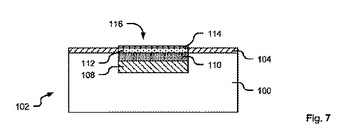

縦型トランジスタ装置は、III−V族半導体材料から形成される基板(100)と、少なくとも部分的に基板内に収容される多層スタック(116)とを備える。多層スタックは、基板(100)に隣接して配置される半絶縁層(108)と、第1のIII−V族半導体材料から形成されており、半絶縁層に隣接して配置される第1の層(110)とを備える。多層スタック(116)はまた、第2のIII−V族半導体材料から形成されて、第1の層(110)に隣接する第2の層(112)と、第1の層と第2の層との界面に形成されるヘテロ接合部とを備える。  (もっと読む)

(もっと読む)

半導体素子

【課題】窒化物半導体による分極接合を用いた半導体素子において、高い歩留まりで高性能な素子を作製する。

【解決手段】InaGa1−aNチャネル層9、AlxInyGa1−x−yNバリア層10、およびInbGa1−bNキャップ層11により分極接合を形成する(0≦a、b、c<0.02)。また、上記バリア層の膜厚T及びAl組成xは、41<T<310(単位:nm)、0.08≦x<0.12、又は30<T<150、0.12≦x<0.16、又は24<T<92、0.16≦x<0.20、又は19<T<62、0.20≦x<0.24、又は16<T<45、0.24≦x<0.28、又は14<T<34、0.28≦x<0.32、又は12<T<27、0.32≦x<0.36、又は11<T<22、0.36≦x<0.40のいずれかの範囲にある。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

高電子移動度トランジスタ、エピタキシャル基板、及び高電子移動度トランジスタを作製する方法

【課題】ノーマリオフ特性を実現する高電子移動度トランジスタを提供する。

【解決手段】チャネル層25が第1のバリア層27上に設けられると共に第1のバリア層27と第1のヘテロ接合33を成す。また、チャネル層25は圧縮歪みを内包して、チャネル層25のピエゾ電界PZC2は支持基体13から第1のバリア層27への方向に向く。第1のヘテロ接合33がIII族窒化物領域23のc軸方向に対して40度以上85度以下及び140度以上180度未満の角度範囲の傾斜角αで傾斜した基準軸ベクトルに垂直な平面に沿って延在するとき、ゲート電極19直下におけるチャネル層25におけるピエゾ電界PZC2の大きさをc面上のトランジスタにおけるピエゾ電界の大きさに比べて小さくできて、有限な大きさのピエゾ電界を残しながらノーマリオフ特性が実現される。

(もっと読む)

電子スピン共鳴生成装置および電子スピン共鳴の生成方法

【課題】外部磁場を用いることなく、電子スピン共鳴を生じさせること。

【解決手段】本発明は、半導体からなり、電子の走行方向に対し交差する方向に第1のスピン軌道相互作用に起因した一定の第1有効磁場が生じるチャネル18と、前記チャネル内に前記第1有効磁場に起因して生じた前記電子のスピン分離エネルギに対応する周波数の交流電界を生じさせることにより、前記チャネル内に前記電子の走行方向および前記第1有効磁場の方向に交差する方向に第2スピン軌道相互作用に起因した交流の第2有効磁場を発生させる電極24と、を具備する電子スピン共鳴生成装置である。

(もっと読む)

半導体素子用エピタキシャル基板、ショットキー接合構造、およびショットキー接合構造の漏れ電流抑制方法

【課題】ショットキー接合の逆方向特性についての信頼性が高い半導体素子を実現可能な、半導体素子用のエピタキシャル基板を提供する。

【解決手段】下地基板1の上にIII族窒化物層群を(0001)結晶面が基板面に対し略平行となるよう積層形成した半導体素子用エピタキシャル基板10が、Inx1Aly1Gaz1N(x1+y1+z1=1、z1>0)なる組成の第1のIII族窒化物からなるチャネル層3と、Inx2Aly2N(x2+y2=1、x2>0、y2>0)なる組成の第2のIII族窒化物からなる障壁層5とを備え、第2のIII族窒化物が、短距離規則度パラメータαが0<α<1の範囲をみたす短距離規則混晶であるようにする。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】本発明は、耐圧特性を維持したままアクセス抵抗を低減して高速動作が可能な窒化物半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明による窒化物半導体装置は、窒化物半導体を用いたヘテロ接合電界効果型の半導体装置であって、基板1上に順次積層して形成されたチャネル層3およびバリア層4と、バリア層4上に離間して形成されたソース電極5およびドレイン電極6とを備え、ソース電極5およびドレイン電極6のそれぞれの下方であり、かつ、バリア層4の表面からチャネル層3の少なくとも一部までの領域に対して、不純物拡散を行うことによって不純物拡散領域22を設け、バンドギャップを変化させることを特徴とする。

(もっと読む)

半導体素子用エピタキシャル基板、半導体素子、および、半導体素子用エピタキシャル基板の作製方法

【課題】オーミックコンタクト特性が優れており、かつ、良好なデバイス特性を有する半導体素子を実現することができるエピタキシャル基板を提供する。

【解決手段】下地基板の上に、少なくともAlとGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層を形成し、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層を、表面近傍部におけるIn組成比が表面近傍部以外の部分におけるIn組成比よりも大きくなるように形成する。

(もっと読む)

161 - 180 / 547

[ Back to top ]