Fターム[5F102GT01]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688)

Fターム[5F102GT01]の下位に属するFターム

Al (180)

高融点金属(Mo、Ti、Ta、W、Cr、Nb、Hf、V、Zr) (912)

合金 (49)

Fターム[5F102GT01]に分類される特許

121 - 140 / 547

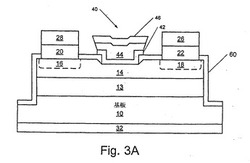

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

多重フィールドプレートトランジスタ

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能

するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレ

イン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間

にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のス

ペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプ

レートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペー

サ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、

第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】電界集中を緩和させることにより、高耐圧、高信頼性を得ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板と、半導体基板上に設けられるゲート電極と、ゲート電極を挟んで半導体基板上に設けられるソース電極及びドレイン電極と、ゲート電極の少なくともドレイン電極側のエッジの下部に設けられるリセスと、を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層のクラックをより一層低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基材1と、基材1の上方に形成された初期層2と、初期層2上に形成され、III−V族化合物半導体を含むコア層3と、が設けられている。初期層3として、コア層3に含まれるIII-V族化合物半導体のIII族原子の層が形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因する反り等を抑制しつつ良好な結晶性の電子走行層及び電子供給層を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層3と、電子走行層3上方に形成された電子供給層4と、基板1と電子走行層3との間に形成され、AlxGa1-xN(0≦x≦1)を含むバッファ層2と、が設けられている。xの値は、バッファ層2の厚さ方向で複数の極大及び複数の極小を示し、バッファ層2中の厚さが1nmの任意の領域内では、xの値の変化量が0.5以下となっている。

(もっと読む)

半導体発光素子

【課題】GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成された窒化物系III−V族化合物半導体からなる活性層15とを備え、n型積層構造(11〜14)がSiを5x1017cm-3以上2x1019cm-3以下の濃度で含有し、厚さが0.3nm以上200nm以下のドープ層10と、ドープ層10よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

直列接続式の高電子移動度トランジスターデバイス及びその製造方法

【課題】等価回路により電圧の累積効果を達成することが可能であって、ハイブレークダウン電圧の特性を有する高電子移動度トランジスターデバイスを提供する。

【解決手段】本発明は、製造プロセスで高電子移動度トランジスターを定義し、内部接続の方法で前記高電子移動度トランジスターを直列接続させた直列接続式の高電子移動度トランジスターデバイス及びその製造方法。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 ゲート電極からソース及びドレインまでの領域を覆う絶縁膜が、寄生容量増大の要因になっている。

【解決手段】 半導体層を有する基板の上にゲート電極が形成されている。半導体層の上に、ゲート電極から相互に反対側に離れて、ソース電極及びドレイン電極が形成されている。ソース電極とドレイン電極との間の半導体層の上に、ソース電極及びドレイン電極から離れて配置されたゲート横絶縁膜が形成されている。ゲート横絶縁膜には、ゲート電極の下端が充填されたゲート用開口が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】

本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】

化合物半導体装置は、基板と、前記基板上に形成された窒化ガリウム系半導体と、前記窒化ガリウム系半導体上に形成された窒化ガリウム系保護層と、前記窒化ガリウム系保護層上にタンタルとアルミニウムが任意の順に積層されてなるオーミック電極とを備え、前記オーミック電極が形成された箇所の前記窒化ガリウム系保護層の膜厚は、前記オーミック電極が形成されていない箇所の前記窒化ガリウム系保護層の膜厚よりも薄い。

(もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

【課題】窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。

【解決手段】パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

半導体装置の製造方法および半導体基板

【課題】所望のレジストパターンが形成可能な、インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域を有する半導体装置の製造方法を提供する。

【解決手段】インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域と、第1の層および第1の層とは異なる半導体層からなるメサ領域と、を備える半導体基板を用いた半導体装置の製造方法であって、フィールド領域表面に、半導体基板表面から半導体基板上に形成する電子ビーム露光用レジストへのインジウムおよびアルミニウムを含む成分の拡散を抑制する被覆層を形成する工程と、フィールド領域表面に被覆層が形成された半導体基板上に電子ビーム露光用レジストを塗布し、メサ領域の一部に電子ビームを露光し、現像することでメサ領域に開口部を有するレジストパターンを形成する工程と、メサ領域に開口部を有するレジストパターンを用いて半導体基板を修飾する工程とを有する製造方法。

(もっと読む)

半導体基板および絶縁ゲート型電界効果トランジスタ

【課題】絶縁ゲート型(MIS型)のP−HEMT構造において、チャネル層のキャリア移動度を向上し、界面準位の影響を低減した、良好なトランジスタ性能を実現できる技術を提供する。

【解決手段】ベース基板と、第1結晶層と、絶縁層とを有し、前記ベース基板、前記第1結晶層および前記絶縁層が、前記ベース基板、前記第1結晶層、前記絶縁層の順に位置し、前記第1結晶層が、GaAsまたはAlGaAsに擬格子整合できるInxGa1−xAs(0.35≦x≦0.43)からなる半導体基板を提供する。前記第1結晶層は、電界効果トランジスタのチャネル層に適用できる層であってもよく、前記絶縁層は、前記電界効果トランジスタのゲート絶縁層に適用できる層であってもよい。前記第1結晶層の77Kにおけるフォトルミネッセンス発光のピーク波長が、1070nmより大きいものであってもよい。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】ゲートのリーク電流を少なくする。

【解決手段】サファイアからなる基板11上に膜厚が30nmのGaNからなる核形成層12を形成し、核形成層12上に膜厚が2μmのGaNからなるバッファ層13を形成し、バッファ層13上に膜厚が20nmでありかつIn組成が0.25のInAlNからなるバリア層16の第1の層14を形成し、第1の層14上に膜厚が20nmでありかつIn組成が0.15のInAlNからなるバリア層16の第2の層15を形成し、第2の層15上にAl/TiまたはTi/Auからなるソース電極17、ドレイン電極18をオーミック接合により形成し、第2の層15が除去された部分にNi/Auからなるゲート電極19を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaAsデバイスにおいて、空洞上に浮遊するGaAs層に素子形成を行うことにより、浮遊容量を抑え、高速化・低電力化を図ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板11上に形成される空洞14と、空洞14上に形成されるGaAsエピタキシャル層13と、GaAsエピタキシャル層13上に形成されるゲート電極15と、それぞれGaAsエピタキシャル層13上に形成され、隣接するゲート電極15を挟むように形成される一対のソース電極16及びドレイン電極17と、を備える。

(もっと読む)

121 - 140 / 547

[ Back to top ]