Fターム[5F102GT01]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688)

Fターム[5F102GT01]の下位に属するFターム

Al (180)

高融点金属(Mo、Ti、Ta、W、Cr、Nb、Hf、V、Zr) (912)

合金 (49)

Fターム[5F102GT01]に分類される特許

141 - 160 / 547

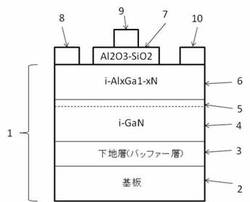

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】検波できる周波数が高く、トンネル電流が流れやすい半導体装置を提供する。

【解決手段】第1の導電型の第1の半導体層と、前記第1の半導体層に接して形成された第2の半導体層と、前記第2の半導体層に接して形成された第2の導電型の第3の半導体層と、を有し、前記第1の半導体層において、前記第1の半導体層と前記第2の半導体層との界面より所定の距離離れた位置には第1の半導体領域が形成されており、前記第1の半導体領域における不純物濃度は、前記第1の半導体領域を除く前記第1の半導体層における不純物濃度よりも高いものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】電流コラプスを抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、窒化物半導体からなるチャネル層14と、前記チャネル層14上に設けられた窒化物半導体からなる電子供給層16と、前記電子供給層16上に設けられた窒化ガリウムからなるキャップ層18と、を形成する成長工程と、前記キャップ層18の上面に、パワー密度が0.0125〜0.15W/cm2である酸素プラズマ処理を行う工程と、を有する半導体装置の製造方法である。本発明によれば、酸素をゲッタリングすることで、電流コラプスを抑制することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、剥離液の残渣を除去できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板上に開口を有するレジストマスクを形成する工程と、該基板のうち該開口により露出した部分に所定の処理を施す工程と、アリールスルホン酸を含む剥離液を用いて該レジストマスクを剥離する工程と、リンス液を用いて該剥離液の残渣を除去する工程と、該基板上に膜を形成する工程と、を備える。そして、該リンス液の溶解度パラメータは12.98から23.43までのいずれかの値であることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】GaN系半導体層内に形成される電子トラップ濃度を低減する。

【解決手段】Si基板10上に接して形成されたAlNを主成分とする下地層12と、前記下地層12上に形成され、前記下地層12上に形成され、前記下地層12から圧縮応力を受ける第1バッファ層14と、前記第1バッファ層14上に形成された第2バッファ層16と、前記第2バッファ層16上に形成されたAlの組成比が0.1以下のGaN系半導体層18と、を具備し、前記第2バッファ層16における前記第1バッファ層14側の面の結晶軸長に対し前記第1バッファ層14と反対の面の結晶軸長が前記GaN系半導体層18に近く、前記第2バッファ層16の伝導帯底エネルギーが前記GaN系半導体層18より高い半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電位の位相差を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板と、基板上方に形成された電子走行層と、電子走行層上方に形成された電子供給層と、電子供給層上方に形成された複数のゲート電極5gと、複数のゲート電極5gが接続されたゲートパッド8gと、が設けられている。ゲート電極5gのゲート幅がゲートパッド8gから離間するほど小さくなっている。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】デバイス特性に優れたHEMT構造またはMIS(MOS)型HEMT構造の半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群を有する半導体積層構造において、バッファー層3と第1の半導体層4とをMOCVD法で形成し、第2の半導体層6をMBE法で形成する。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38及びソース電極34はドレイン電極36を囲み、ソース電極34の上部に、ゲート電極38の上方を通過してドレイン電極36側に庇状に突き出したフィールドプレート170が形成され、GaN系エピタキシャル基板32の表面層とフィールドプレート170との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート170の直下領域においてフィールドプレート終端面と面一状態となるように切れ込み、その下端からドレイン電極36に接続するようにドレイン電極36に向かって延びている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】2つのオーミック電極、及び、それらの間に配置されたゲート電極を備えた、ゲート電極形成用電子線の揺らぎに起因するゲート電極形成不良が生じない形で製造できる半導体装置を提供する。

【解決手段】半導体装置1の、ゲート電極20により近い方のオーミック電極(ソース電極14s)として、ゲート電極20と対向する側の少なくとも一方の隅(電子線の描画開始位置側の隅)がカットされた矩形形状のものを採用しておく。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】シリコン基板上に優れた結晶性の窒化物半導体層が形成された窒化物半導体装置を提供する。

【解決手段】シリコン基板10と、シリコン基板10に接するとともにシリコン基板10上の一部分に形成された窒化シリコンからなる選択成長マスク層20とを備え、選択成長マスク層20が形成されていないシリコン基板10上に、当該シリコン基板10に接するように窒化物半導体層30が形成されている。

(もっと読む)

半導体装置

【課題】高周波モジュール中におけるスイッチング素子として用いられるHEMT素子を小型化する。

【解決手段】GaAsからなる基板1の主面上の素子分離部9で規定された活性領域内において、ゲート電極17は、1本で形成し、ソース電極13とドレイン電極14との間では紙面上下方向に延在し、それ以外の部分では左右方向に延在するようにパターニングすることにより、活性領域外に配置されるゲート電極17の割合を減じ、ゲートパッド17Aの面積を減じる。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法、および半導体装置の動作方法

【課題】電界集中を緩和し、高い耐圧を得ることが可能な半導体装置を提供する。

【解決手段】

半導体層上において、第1フィールドプレートFAは、第1絶縁膜上に、第1電極102と第2電極103との間に相互に間隔を置いて配置され、第2フィールドプレートFBは、第2絶縁膜上に、第1電極102上方から第2電極103上方までの間に相互に間隔を置いて配置され、

第1電極および第2電極側末端のFBは、第1電極または第2電極およびそれに隣り合うFAに重なり、

前記第1電極および第2電極側末端FB以外の一方のFAまたはFBは、第1電極から第2電極への方向と垂直方向に隣り合う複数の他方のFAまたはFBに重なり合い、前記第1電極および第2電極側末端FB以外の他方のFAまたはFBは、第1電極から第2電極への方向に隣り合う2つの前記一方のFAまたはFBに重なり合う半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

半導体装置

【課題】高電圧を印加した際に逆バイアスにおけるリーク電流が少なく、順方向電圧降下Vfが低い整流素子を有する単一基板上にトランジスタ素子と整流素子を一体にした半導体装置を提供する。

【解決手段】半導体装置10は、単一の基板11上にトランジスタ素子12と整流素子13とを備える半導体装置10であって、トランジスタ素子12は、基板11上に形成された活性層14と、活性層14に接合されたソース電極15とドレイン電極16とゲート電極17を備え、整流素子13は、活性層14に接合されたアノード電極18と、ドレイン電極16を用いたカソード電極と、アノード電極18とカソード電極の間に第1の補助電極19を備えた。

(もっと読む)

半導体装置

【課題】本発明は、ゲート電極の端部に発生する電界集中を緩和し、高いオフ耐圧と優れた高周波特性を有する半導体装置を提供するを目的とする。

【解決手段】実施形態によれば、チャネル層3上に互いに離間して設けられ、それぞれがチャネル層3に電気的に接続されたソース電極4およびドレイン電極5と、ソース電極4とドレイン電極5との間においてチャネル層3に接して設けられたゲート電極6と、ゲート電極6とドレイン電極5との間においてチャネル層3上に設けられたパッシベーション膜7と、ゲート電極6に接触し、且つ、ドレイン電極5と離間してパッシベーション膜7上に設けられたパッシベーション膜7よりも誘電率が高い高誘電率膜8と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

広バンドギャップショットキー障壁デバイス用の多層拡散障壁

141 - 160 / 547

[ Back to top ]