Fターム[5F102GT01]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688)

Fターム[5F102GT01]の下位に属するFターム

Al (180)

高融点金属(Mo、Ti、Ta、W、Cr、Nb、Hf、V、Zr) (912)

合金 (49)

Fターム[5F102GT01]に分類される特許

101 - 120 / 547

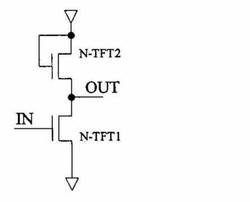

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体装置

【課題】基板の反りを抑制しつつ、バッファ層及び化合物半導体の厚さを稼ぐことができ、素子耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置は、基板2と、バッファ層3と、窒化物系化合物半導体4とを備える。バッファ層3は、AlN層とGaN層とを積層した第1のバッファ領域321,331と、GaN層を有する第2のバッファ領域322,332とを交互に積層して構成される。バッファ層3において窒化物系化合物半導体4側の第1のバッファ領域331とそれに隣接する第2のバッファ領域332との1組の全体のAl組成は基板側の1組のAl組成に対して大きく設定されている。

(もっと読む)

低1cらせん転位の3インチ炭化珪素ウェハ

【課題】製造された結晶にある欠陥総数を低減するために、種結晶を用いた昇華システムにおいて形成された結晶の1cらせん転位欠陥レベルが低く、より大きく、高品質の炭化珪素バルク単結晶を製造する方法を提供する。

【解決手段】3C、4H、6H、2H、および15Rポリタイプからなる群から選択されるポリタイプであって、少なくとも75mm(3インチ)の直径と、約2000cm−2未満の1cらせん転位密度とを有する高品質のSiC単結晶ウェハ。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体発光素子

【課題】平坦性が向上した半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成されたInGaNからなる多重井戸構造を備える活性層15とを備え、n型積層構造が、GaN層11と、GaN層11上に形成されたドープ層10と、ドープ層10上に設けられた窒化物系III−V族化合物半導体層12と、窒化物系III−V族化合物半導体層12よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】電子移動度の低下が抑制され、かつ二次元電子ガスの閉じ込めが高められた半導体装置およびその製造方法を提供する。

【解決手段】AlaInbGa1-(a+b)N(0≦a,b≦1、0≦a+b≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが大きい第1の窒化物半導体層2、AlcIndGa1-(c+d)N(0≦c,d≦1、0≦c+d≦1)から成る第2の窒化物半導体層3、IneGa1-eN(0<e≦1)から成り、第2の窒化物半導体層3よりもバンドギャップが小さいバックバリア層4、AlfIngGa1-(f+g)N(0≦f,g≦1、0≦f+g≦1)から成り、第2の窒化物半導体層3とバンドギャップが等しいチャネル層5、AlhIniGa1-(h+i)N(0≦h,i≦1、0≦h+i≦1)から成り、チャネル層5よりもバンドギャップが大きいバリア層6を、この順に基板1に積層する。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

アクティブ発振防止付き複合半導体デバイス

【課題】アクティブ発振防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、アクティブ発振制御付き複合半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、例えば修正したボディ打込み領域により低減した出力抵抗、及び例えば修正した酸化物の厚さにより低減したトランスコンダクタンスの一方または両方を含むように構成されて、複合半導体デバイスのゲインを約10,000以下にすることができる。

(もっと読む)

パッシブ発振防止用のIII族窒化物トランジスタ

【課題】パッシブ発振制御を有する半導体素子を提供する。

【解決手段】ソース電極202、ゲート電極208およびドレイン電極204を有するIII族窒化物トランジスタ200を含む。ダンピング抵抗器270がパッシブ発振制御をIII族窒化物トランジスタ200に提供するように構成される。ダンピング抵抗器270が少なくとも一つの集中抵抗器R1を含む。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ

【課題】電子トラッピングによる、DC特性とRF特性の差を低減する。

【解決手段】トランジスタ10は、チャネル層を有する活性領域を含み、この活性領域と接触してソースおよびドレイン電極20,22が形成され、このソース電極とドレイン電極との間にあって活性領域と接触したゲート24が形成される。ゲートとドレイン電極との間およびゲートとソース電極との間の複数の活性領域の表面の少なくとも一部分上にスペーサ層28がある。このスペーサ層上にはフィールドプレート32があり、活性領域の上のスペーサ上をドレイン電極に向かって延びる。このフィールドプレートはさらに、活性領域の上のスペーサ層上をソース電極に向かって延びる。少なくとも1つの導電性経路34,36が、フィールドプレートをソース電極またはゲートに電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

高電子移動度トランジスタ(HEMT)

【課題】高周波特性を改善する。

【解決手段】III族窒化物系高電子移動度トランジスタ(HEMT)20は、GaNバッファ層26を備えており、Ganバッファ層26上にAlyGa1−yN(y=1又は≒1)層28がある。AlxGa1−xN(0≦x≦0.5)バリア層30が、GaNバッファ層26の反対側でAlyGa1−yN層28上にあり、該層28のAl濃度は、バリア層30よりも高い。GaNバッファ層26とAlyGa1−yN層28との間の界面に2DEG38が形成されている。バリア層30上に、ソース、ドレイン、及びゲート・コンタクト32、34、36が形成されている。また、AlyGa1−yN層28の反対側において、バッファ層26に隣接する基板22も含み、GaNバッファ層26と基板22との間に、核生成層24を含むことができる。

(もっと読む)

半導体素子

【課題】低オン抵抗で、ノーマリーオフ動作を有し、高信頼性の半導体素子を提供する。

【解決手段】半導体素子1Aは、支持基板10上にN面成長されたAlXGa1−XN(0≦X<1)を含む第1半導体層11と、前記第1半導体層上に形成されたノンドープもしくは第1導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層15と、前記第2半導体層上に形成されたAlZGa1−ZN(0≦Z<1、Z<Y)を含む第3半導体層16と、を備える。半導体素子1Aは、第3半導体層16に接続された第1主電極20と、第3半導体層16に接続された第2主電極21と、第1主電極と第2主電極とのあいだの第3半導体層16の上に設けられたゲート電極31と、を備える。第3半導体層16の厚さは、ゲート電極31下において選択的に薄い。

(もっと読む)

101 - 120 / 547

[ Back to top ]