Fターム[5F102GT04]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | 金属 (1,688) | 合金 (49)

Fターム[5F102GT04]に分類される特許

1 - 20 / 49

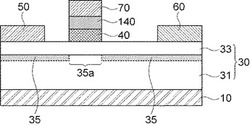

窒化物半導体素子及びその製造方法

【課題】ノーマリーオフ特性を具現すると共にゲートリーク電流を抑制する窒化物半導体素子及びその製造方法を提供する。

【解決手段】第1の窒化物層31とその材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、その上にオミック接触されたソース電極50と、これから離間して窒化物半導体30層上にオミック接触されたドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に、これらから離間して形成されたP型窒化物層40と、この上に形成されたN型窒化物層140と、ソース側の側壁が、P型窒化物層40及びN型窒化物層140のソース側の側壁と整列するようにN型窒化物層140上に接触させたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

トランジスタ

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

高電子移動度トランジスタ(HEMT)

【課題】高周波特性を改善する。

【解決手段】III族窒化物系高電子移動度トランジスタ(HEMT)20は、GaNバッファ層26を備えており、Ganバッファ層26上にAlyGa1−yN(y=1又は≒1)層28がある。AlxGa1−xN(0≦x≦0.5)バリア層30が、GaNバッファ層26の反対側でAlyGa1−yN層28上にあり、該層28のAl濃度は、バリア層30よりも高い。GaNバッファ層26とAlyGa1−yN層28との間の界面に2DEG38が形成されている。バリア層30上に、ソース、ドレイン、及びゲート・コンタクト32、34、36が形成されている。また、AlyGa1−yN層28の反対側において、バッファ層26に隣接する基板22も含み、GaNバッファ層26と基板22との間に、核生成層24を含むことができる。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

半導体トランジスタおよびその製造方法

【課題】FETの閾値電圧のばらつきのない半導体トランジスタおよびその製造方法を提供する。

【解決手段】半導体トランジスタ100は、基板1と、基板1の上方に形成された第1化合物半導体層103と、第1化合物半導体層103上に形成され、第1化合物半導体層103よりもバンドギャップの大きい第2化合物半導体層104と、第2化合物半導体層104内の少なくとも一部に、酸素がドープされた酸素ドープ領域105と、第2化合物半導体層104上に形成された第3化合物半導体層106と、第1化合物半導体層103に電気的に接続されたソース電極107およびドレイン電極109と、酸素ドープ領域105の上方に、酸素ドープ領域105に接するように形成されたゲート電極108とを有する。

(もっと読む)

化合物半導体装置

【課題】ゲート電極のリーク電流の増大を抑制して、長期間にわたって安定した高電圧動作を実現する。

【解決手段】GaNからなる化合物半導体層100上に形成されたゲート電極103において、GaNからなる化合物半導体層100上でショットキー接合してなるNi層41と、Au、Cu及びAlからなる群から選択された1種の金属からなる低抵抗金属層42と、Ni層41と低抵抗金属層42との間に形成されたPd層44を設けるようにする。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

化合物半導体装置

【課題】閾値電圧の高い良好なノーマリオフ特性を有する化合物半導体装置を提供する。

【解決手段】キャリア走行層21とキャリア供給層22を有し、二次元キャリアガス層211が形成される化合物半導体層2と、化合物半導体層2上に互いに離間して配置され、二次元キャリアガス層211とオーミック接続する第1の主電極3及び第2の主電極4と、第1の主電極3と第2の主電極4間で、化合物半導体層2上に配置された金属酸化物半導体膜8と、金属酸化物半導体膜8上に配置された、金属酸化物半導体膜8に接するチタン膜又はチタンを含む化合物膜を有する制御電極5とを備える。

(もっと読む)

窒化物系ダイオード

【課題】高耐圧でかつ低オン電圧動作が可能な窒化物系ダイオードを提供する。

【解決手段】窒化物系ダイオード10は、シリコン基板11の(111)面上に形成されたバッファ層12と、アンドープのGaNからなるチャネル層13と、チャネル13層上に形成されたアンドープのAlGaNからなる電子供給層14と、電子供給層14上に形成されたカソード電極15およびアノード電極16とを備える。窒化物系ダイオード10はさらに、電子供給層14を、チャネル層13に達する深さまで部分的に除去したメサ18を備え、メサ18の一方の側面部18aにアノード電極16が接触している。アノード電極16がメサ18の側面部18aに接触することで、アノード電極16と2次元電子ガス層17とが電気的に接続されている。

(もっと読む)

窒化物系化合物半導体装置、及びその製造方法

【課題】オーミック電極のオーミックコンタクト抵抗を確実に低減させる。

【解決手段】各オーミック電極3、4は、GaNキャップ層26表面のリセス28周辺部位に接触する第1電極51と、第1電極51に接触して、リセス28を介して2次元電子ガス層27に及ぶ第2電極52とを有している。第1電極51は、リセス28の開口部を囲む環状のものである。第2電極52は、第1電極51に重なる頭部52a、及びリセス28内に形成された柱状部52bからなる。第1及び第2電極51、52を第1及び第2温度でそれぞれ熱処理しているので、第1及び第2電極51、52のオーミックコンタクト抵抗を共に低減させ、各オーミック電極3、4そのもののオーミックコンタクト抵抗を低減させることができる。

(もっと読む)

半導体素子

【課題】窒化物半導体による分極接合を用いた半導体素子において、高い歩留まりで高性能な素子を作製する。

【解決手段】InaGa1−aNチャネル層9、AlxInyGa1−x−yNバリア層10、およびInbGa1−bNキャップ層11により分極接合を形成する(0≦a、b、c<0.02)。また、上記バリア層の膜厚T及びAl組成xは、41<T<310(単位:nm)、0.08≦x<0.12、又は30<T<150、0.12≦x<0.16、又は24<T<92、0.16≦x<0.20、又は19<T<62、0.20≦x<0.24、又は16<T<45、0.24≦x<0.28、又は14<T<34、0.28≦x<0.32、又は12<T<27、0.32≦x<0.36、又は11<T<22、0.36≦x<0.40のいずれかの範囲にある。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

1 - 20 / 49

[ Back to top ]