Fターム[5F110BB11]の内容

Fターム[5F110BB11]に分類される特許

321 - 325 / 325

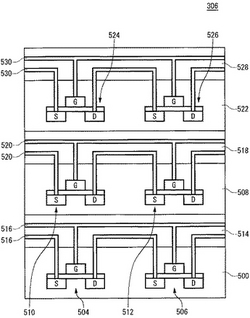

半導体集積回路、及び半導体集積回路の製造方法

【課題】回路面積の小さく、配線長の短い、小型の半導体集積回路を提供する。

【解決手段】多層構造で構成される半導体集積回路であって、第1半導体層と、第1半導体層に形成された第1半導体層トランジスタと、第1半導体層上に堆積され、金属配線が形成された配線層と、配線層上に堆積された第2半導体層と、第2半導体層に形成された第2半導体層トランジスタとを備える。なお、第1半導体層トランジスタのゲート絶縁膜の絶縁性と、第2半導体層トランジスタのゲート絶縁膜の絶縁性とは概ね同等であり、第2半導体層トランジスタのゲート絶縁膜は、ラジカル酸化又はラジカル窒化により形成される。

(もっと読む)

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

独立して歪むNチャネル型及びPチャネル型トランジスタ

第一ウェハ上に形成された第一の複数のトランジスタと、第二ウェハ上に形成された第二の複数のトランジスタとを備えた集積回路。第一トランジスタのうち少なくとも実質的に大部分が第一導電型であり、第二の複数のトランジスタのうち少なくとも実質的に大部分が第二導電型である。ウェハ同士が結合された後、第二ウェハの一部が除去されて、第二の複数のトランジスタのチャネルの歪みの圧縮性が、第一の複数のトランジスタのチャネルの歪みの圧縮性よりも高くなる。  (もっと読む)

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

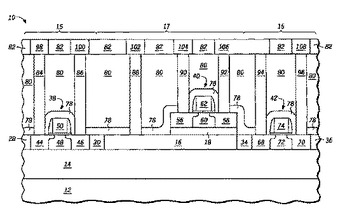

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

321 - 325 / 325

[ Back to top ]