Fターム[5F110BB11]の内容

Fターム[5F110BB11]に分類される特許

121 - 140 / 325

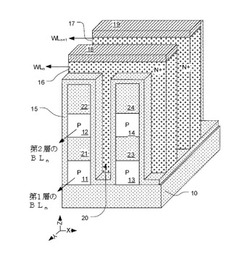

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

ノードコンタクト構造体

【課題】ノードコンタクト構造体を有する半導体素子と、その製造方法を提供する。

【解決手段】半導体基板の上に形成されソース/ドレイン領域を有するバルクモストランジスタを備える。該バルクモストランジスタ上に層間絶縁膜が形成され、該層間絶縁膜上にソース/ドレイン領域を有する薄膜トランジスタが形成される。該バルクモストランジスタのソース/ドレイン領域上に半導体プラグが形成され、該半導体プラグは該層間絶縁膜の少なくとも一部を介して延長される。該薄膜トランジスタのソース/ドレイン領域及び該半導体プラグは金属プラグと接触し、該金属プラグは該層間絶縁膜の少なくとも一部を介して延長される。該半導体プラグ及び該金属プラグは多層のプラグを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜に酸素ドープ処理を行って、第2の絶縁膜中に酸素原子を供給し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】半導体基板中の複数の素子層間を有効に絶縁分離する。

【解決手段】裏面照射型の固体撮像装置において、受光部側と回路側との素子分離層を所定のマスクパターンを介した酸素イオン注入と、その後の熱処理によって半導体基板中に酸化膜を形成することにより実現する。例えばSOI基板のような支持基板部(絶縁体層)の上にシリコン層を設けた半導体基板に対し、シリコン基板(表面)側から光電変換素子層、素子分離層としての酸素イオン注入層、画素トランジスタ等の回路層を順次形成し、その後、シリコン層上に配線層を形成する。そして、裏面側の絶縁体層を除去することにより、シリコン層の受光部を露出させ、薄型のシリコン基板よりなる固体撮像装置を形成できる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミスを防ぐことが可能である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

結晶性半導体膜の形成方法、および、半導体デバイスの製造方法

【課題】結晶粒界の方向とチャネル領域の方向とが直交しているトランジスタの性能を向上させるとともに、各トランジスタの特性のバラツキを少なくする。

【解決手段】本発明の結晶性半導体膜の形成方法は、基板11上にアモルファスシリコン膜(非晶質半導体膜)12を形成する工程と、第1のレーザ光20aおよび基板11のうちの少なくとも一方を移動させながら、アモルファスシリコン膜12に対して第1のレーザ光20aを照射し、その移動方向に沿って半導体膜の結晶を成長させてアモルファスシリコン膜12から多結晶シリコン膜(結晶性半導体膜)13を得る工程と、多結晶シリコン膜13に対して、第1のレーザ光20aよりもエネルギー量の小さい第2のレーザ光30aを照射して、半導体膜の厚さ方向に対して結晶を成長させて、再結晶化後の多結晶シリコン膜(結晶性半導体膜)14を得る工程と、を含む。

(もっと読む)

半導体装置

【課題】フォトセンサにおいて、入射光を正確に電気信号に変換することを目的の一とする。

【解決手段】フォトダイオード、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタを有し、第2のトランジスタは、第1のトランジスタのゲートに蓄積された電荷を保持する機能を有し、第3のトランジスタは、第1のトランジスタのゲートに蓄積された電荷を放電する機能と、第1のトランジスタのゲートに蓄積された電荷を保持する機能を有し、第2のトランジスタ及び第3のトランジスタを非導通状態とする期間において、第2のトランジスタ及び第3のトランジスタのゲートに印加される電圧レベルを、第2のトランジスタ及び第3のトランジスタのソース及びドレインの低電圧の側の電圧レベルより小さくする。

(もっと読む)

121 - 140 / 325

[ Back to top ]