Fターム[5F110BB11]の内容

Fターム[5F110BB11]に分類される特許

101 - 120 / 325

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

非単結晶トランジスタ集積回路

【課題】更に多機能化した非単結晶トランジスタ集積回路を提供する。

【解決手段】非単結晶トランジスタ集積回路は、第1の高分子フィルム11と、高分子フィルム11に設けられた共通電極12と、共通電極12に設けられた誘電体13と、誘電体13に設けられた第2の高分子フィルム14と、第2の高分子フィルム14に設けられ、圧力が加えられた際に、誘電体13の厚さの変化量を容量の変化として読み出す圧力センサ15と、第2の高分子フィルム14に設けられ、圧力センサ15を読み出すための非単結晶トランジスタ16とを具えることを特徴とする。

(もっと読む)

半導体装置

【課題】非晶質上に低コストで高性能な半導体装置を形成する技術を提供する。

【解決手段】GeがSi濃度よりも高濃度に含まれた疑似Ge領域(2)を含有し、該領域のGe濃度は初期SiGe薄膜中のGe濃度よりも高濃度であり、リボン形状をした結晶粒(1)は、互いに平行で且つ直線状に配置している疑似Ge領域(2)に挟まれる構造を有し、結晶粒(1)内においてGe濃度はSi濃度よりも低濃度であり、且つ結晶粒(1)内のGe濃度は初期SiGe薄膜中のGe濃度よりも低濃度であり、さらに各々の結晶粒(1)は相互に同一の方位を有する結晶粒から成っていることを特徴とする非晶質上の半導体薄膜からなる半導体装置。

(もっと読む)

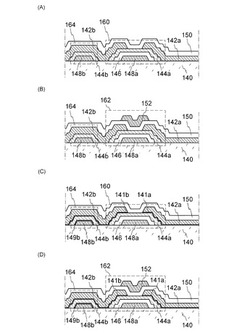

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ソース線と、ビット線と、信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセル1100と、ソース線及びビット線とスイッチング素子を介して電気的に接続された第1の駆動回路1111と、ソース線とスイッチング素子を介して電気的に接続された第2の駆動回路1112と、信号線と電気的に接続された第3の駆動回路1113と、ワード線と電気的に接続された第4の駆動回路1114と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留まりの低下を抑制する半導体装置及びその製造方法を提供する。

【解決手段】実施の形態の半導体装置1は、配線20を有する配線層11bと、配線層11b上に形成された層間絶縁膜26と、層間絶縁膜26上に形成され、上部がシリサイド化されたアモルファスシリコン層27を有するTFT14と、TFT14上に、層間絶縁膜47を介して形成された配線50を有する配線層12aと、層間絶縁膜47、アモルファスシリコン層27及び層間絶縁膜26を貫通し、第1及び第2の配線を電気的に接続するコンタクトプラグ32と、を備える。

(もっと読む)

101 - 120 / 325

[ Back to top ]