Fターム[5F110BB11]の内容

Fターム[5F110BB11]に分類される特許

201 - 220 / 325

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

同軸のトランジスタ構造

【課題】 本発明は基板上での同軸トランジスタを開示する。

【解決手段】同軸構造のMOSFETであって、チップ或いは基板(Wafer Bonding)を積層し、軸心貫通孔により貫通し接続してより高い集積度及びラッチ効果のない同軸全対称のCMOSFETの集積回路を形成することができる。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域に高抵抗不純物領域(HRD

または低濃度不純物領域)を自己整合的に形成する方法を提供する。

【解決手段】ゲイト電極105上面にマスク106を残し、比較的低い電圧でポーラスな

第1の陽極酸化膜107をゲイト電極の側面に成長させる。この陽極酸化膜をマスクとし

てゲイト絶縁膜104’をエッチングする。必要に応じては比較的高い電圧でバリア型の

第2の陽極酸化膜108をゲイト電極の側面および上面に形成する。第1の陽極酸化膜を

選択的にエッチングする。不純物ドーピングをおこなうと、ゲイト電極の下部にはドーピ

ングされず、ゲイト電極に近い領域では、不純物濃度の低い高抵抗領域111,112と

なる。ゲイト電極から遠い領域では、不純物濃度の高い低抵抗領域110,113となる

。

(もっと読む)

横方向成長半導体ナノワイヤの製造方法とその方法により得られたトランジスタ

【課題】

【解決手段】 発明は、金属酸化物層(2)を有する基板(1)上に半導体ナノワイヤ(5)を製造する方法であって、

a)前記層(2)を還元して前記金属酸化物層(2)の表面上に半径(Rm)の金属ナノドロップ(3)を形成するのに適した時間tの間出力Pの水素プラズマ(11)を前記金属酸化物層(2)に照射するステップと、

b)前記金属ナノドロップ(3)を含む前記金属酸化物層(2)上への、前記金属ナノドロップ(3)を被覆するのに適した厚さ(Ha)を有する半導体材料の薄層(4)の低温プラズマ助長蒸着ステップと、

c)前記金属ナノドロップ(3)から薄層(4)として堆積された前記材料の触媒作用によりナノワイヤ(5)の横方向成長を促進するのに十分な温度Tにおいて熱アニールするステップと

を含む半導体ナノワイヤ(5)を製造する方法を提供する。発明はまた、発明の方法により得られたナノワイヤ(5)と、半導体ナノワイヤ(5)、例えばソース(16)、ドレイン(17)、及びゲート(18)間に半導体接続部を形成するシリコンナノワイヤ(SiNW)を含むナノメータトランジスタとを提供する。

(もっと読む)

インバータ及びその動作方法並びにインバータを含む論理回路

【課題】インバータ及びその動作方法並びにインバータを含む論理回路を提供する。

【解決手段】負荷トランジスタと駆動トランジスタとを含み、負荷トランジスタと駆動トランジスタとのうち、少なくとも一つは、ダブルゲート構造を有するインバータである。該ダブルゲート構造によって、負荷トランジスタまたは前記駆動トランジスタのスレショルド電圧が調節され、従って、該インバータは、E/D(enhancement/depletion)モードでありうる。

(もっと読む)

分子素子およびその製造方法ならびに集積回路装置およびその製造方法ならびに三次元集積回路装置およびその製造方法

【課題】一つの分子素子を印加電界の制御によってダイオード、トランジスタまたはメモリとして使うことができ、必要な機能を有する素子を安価に得ることができる分子素子を提供する。

【解決手段】ソース電極13およびドレイン電極14の間の間隙15に機能性分子16を架橋して分子素子10を構成する。機能性分子16は、誘電率異方性および/または双極子モーメントを有し、かつ電界により配向変化が起きるペンダント分子からなる側鎖が、そのペンダント分子の配向変化によって構造変化が起きて電気的特性が変化する共役系分子からなる主鎖に共有結合したものである。ゲート電極17、18により機能性分子16のペンダント分子に印加する電界によって分子素子10をダイオード、トランジスタまたはメモリとして働かせる。

(もっと読む)

配線基板及びその作製方法、並びに、半導体装置及びその作製方法

【課題】絶縁膜中の貫通配線が、絶縁膜よりも下層に配置されている配線層あるいは半導体素子層の配線と剥離するのを防ぐ。

【解決手段】マイクロカプセルと、前記マイクロカプセルが分散された絶縁性樹脂と、前記マイクロカプセルの空孔が接する貫通孔と、前記貫通孔中に形成され、前記絶縁性樹脂の両面に露出している貫通配線を有する配線基板及びその作製方法に関する。また、マイクロカプセルと、前記マイクロカプセルが分散された絶縁性樹脂と、前記マイクロカプセルの空孔が接する貫通孔と、前記貫通孔中に形成され、前記絶縁性樹脂の両面に露出している貫通配線を有する配線基板と、絶縁膜の表面に配線が露出した半導体素子層とを有し、前記配線が前記貫通配線と接触するように、前記半導体素子層が前記配線基板と密接している半導体装置及びその作製方法に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚さを10nm程度以下とした酸化物TFTにおいて、チャネル層とソース電極との間やチャネル層とドレイン電極との間のコンタクト抵抗を低減して高速で動作することができる半導体装置を提供する。

【解決手段】酸化物TFTのオフ状態において完全空乏化状態を実現できるように形成する。そして、チャネル層CHNとソース電極STの間にコンタクト層CTSを形成し、チャネル層CHNとドレイン電極DTとの間にコンタクト層CTDを形成する。さらに、ゲート電極GTとチャネル層CHNとの間のゲート絶縁膜容量をCgi、ゲート電極GT以外の構造物とチャネル層CHNとの間の寄生容量の総和をCpとしたとき、Cgiに対するCpの割合Cp/Cgiが0.7よりも小さくなるように形成する。

(もっと読む)

動的に調整可能な閾値電圧を有する3次元集積トランジスタの回路

【課題】低減された集積度および低消費電力の基準を満たすと同時に、電気的性能の改良をもたらす、多重構造トランジスタを有する新規なデバイスを提供する。

【解決手段】積層の所定レベルに位置する第1トランジスタT11と、所定レベルの上方の積層の第2レベルに位置する第2トランジスタT21とを備え、第1トランジスタは第2トランジスタのチャネル区域116に対向するゲート電極108を備え、第1トランジスタと第2トランジスタとは絶縁区域120により分離され、この絶縁区域は第1トランジスタのゲートと第2トランジスタのチャネルとの間の第1領域R1にて第1トランジスタのゲートと第2トランジスタのチャネルとの間の結合を可能にするように規定された組成および厚さを有し、この絶縁区域は、第1トランジスタおよび第2トランジスタのアクセス区域の間の第1領域の周囲に、第1領域とは異なる組成および厚さを有する第2領域R2を備える。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

三次元集積回路装置の製造方法および三次元集積回路装置

【課題】スイッチング部に分子を用いるトランジスタの性能の劣化を防止することができ、かつ製造コストの低減を図ることができる三次元集積回路装置の製造方法を提供する。

【解決手段】ソース電極の頂点とドレイン電極の頂点とが互いに対向して設けられたICチップ11、31、32を実装基板30上に順次積層する。これらの実装基板30およびICチップ11、31、32のそれぞれの間の隙間34に分子溶液を毛細管現象により注入する。自己組織化により分子溶液中の分子をソース電極の頂点とドレイン電極の頂点との間に接続する。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】支持基板上に、単結晶半導体層を多層構造とした、多層集積回路を形成する場合の、工程数の簡略化を図る。また同集積化の向上を図る。

【解決手段】複数の半導体素子が絶縁層を介して積層される半導体装置において、絶縁層を介して半導体素子を構成する半導体層が積層された構造を有し、一の半導体層が配線とコンタクトする領域が、絶縁層を介して設けられる他の半導体層と重畳するように配置された構成とする。当該コンタクトする領域は、該一の半導体層に設けられる一導電型不純物領域から延在するシリサイド層によって形成される。すなわち、一の半導体素子と配線とのコンタクト領域をシリサイドで形成すると共に上層半導体素子と重畳する位置に配置させ、該半導体素子を構成する一導電型不純物領域と配線とのコンタクト領域との間をシリサイドで連結する構成を有する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上できる半導体基板を提供する。

【解決手段】シリコン基板102と、シリコン基板の上に形成された絶縁膜104であってアスペクト比が√3/3以上のシリコン基板に達する開口部を有する絶縁膜104と、開口部に形成された化合物半導体結晶108であって絶縁膜104の表面より凸に形成されたシード化合物半導体結晶108と、シード化合物半導体結晶108の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層112と、を備えた半導体基板。

(もっと読む)

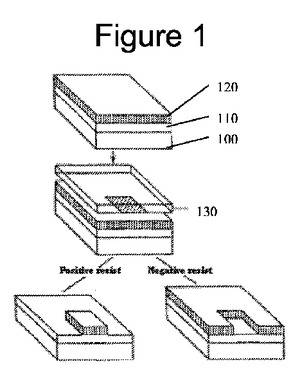

半導体装置の製造方法、半導体装置

【課題】薄膜トランジスタを有する半導体装置を安価に大量生産することを可能にする、半導体装置の製造方法を提供する。

【解決手段】プラスチック基板11等の基板上にアモルファスシリコン層13を形成する工程と、アモルファスシリコン層13をパターニングして、薄膜トランジスタとなる所定のパターンを形成する工程と、その後、パターニングされたアモルファスシリコン層13を結晶化する工程とを有して、薄膜トランジスタを有する半導体装置を製造する。

(もっと読む)

半導体装置とその製造方法

【課題】格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置とその製造方法。

【解決手段】少なくとも第1、第2のSi1-xGex(0≦x≦1)層14a,14b,14cが絶縁膜13上に形成されている。第1、第2のSi1-xGex(0≦x≦1)層上に対応して少なくとも第1、第2の材料層15,16,17が形成されている。第1、第2のSi1-xGex(0≦x≦1)層層14a,14b,14cの格子定数はその上の第1、第2の材料層15,16,17の格子定数に整合されている。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】支持基板上に、単結晶半導体層を多層構造とした、多層集積回路を形成する場合の、工程数の簡略化を図る。また同歩留まりの向上を図る。

【解決手段】基板面内の半導体素子の半導体接合界面領域は、支持基板側から、すなわち基板の素子が形成されていない面からレーザを直接照射し加熱することができるよう配置される。1層目の半導体素子層、2層目の半導体素子層が形成された後、支持基板側からレーザを照射することで、1層目の半導体素子層及び2層目の半導体素子層の、半導体接合界面領域の活性化を同時に行う。支持基板と前記半導体素子層との間の層は光透過性とし、レーザを減衰しない構造とする。

(もっと読む)

基板素子を形成するための方法

本発明は、ナノワイヤ、トランジスタおよび他の構造などの半導体素子を始めとする基板素子を形成する方法、ならびにこのような方法によって形成される素子に関する。 (もっと読む)

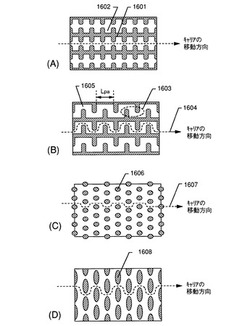

均一な結晶シリコン薄膜を製造するリソグラフィ方法

位置が制御される結晶粒の領域を備える結晶半導体膜と、位置が制御される結晶粒の位置を基準として規定される位置にある結晶半導体膜の中に位置するデバイスとを含む、結晶膜の中の既知の位置に位置付けられる電子デバイスに関係する方法および装置が説明される。この方法は、各照射ステップが、膜のリソグラフィで画成される領域を少なくとも部分的に融解させ、横方向に結晶化させ、横方向成長長さに垂直である少なくとも1つの長い粒子境界を有する横方向に成長した結晶粒の領域を得る、3つ以上の重複する照射ステップを使用して半導体膜の少なくとも一部を照射することと、少なくとも1つの長い粒子境界の位置を識別することと、長い粒子境界の位置を基準にして規定される位置にある半導体膜の中に電子デバイスを製造することとを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域と、前記島状の半導体領域の側面及び上面を覆って設けられたゲート絶縁膜と、前記ゲート絶縁膜を介して前記島状の半導体領域の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

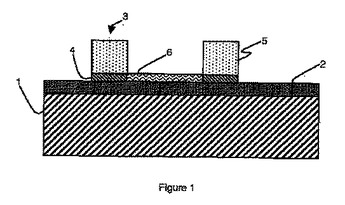

誘電体材料上に2つの電極を接続する半導体材料で作られたナノワイヤを成長する方法

金属材料で作られた電極(3)が、誘電体材料(2)の層上に形成される。少なくとも1つの電極(3)の最下層は、誘電体材料(2)の層と直接接触する触媒材料(4)を構成する。ナノワイヤ(6)は、触媒(4)を用いることにより、電極(3)間に、誘電体材料(2)の層に並行して成長する。次いで、2つの電極(3)を接続するナノワイヤ(6)は、単結晶半導体材料で作られ、誘電体材料(2)の層と接触する。  (もっと読む)

(もっと読む)

201 - 220 / 325

[ Back to top ]