Fターム[5F110BB12]の内容

Fターム[5F110BB12]に分類される特許

441 - 451 / 451

半導体装置及びその製造方法

【課題】 高いドレイン・ソース間耐圧を確保しつつ、低いオン抵抗を実現できる半導体装置及びその製造方法を提供する。

【解決手段】 支持基板1と、支持基板1上に埋込酸化膜2を介して形成され、P-型活性領域3aを有する半導体層3と、ゲート酸化膜17及びLOCOS酸化膜5aの一部を介して半導体層103上に形成されたゲート電極16aとを備え、P-型活性領域3aは、N+型ソース領域11と、P型ボディー領域12と、P+型バックゲートコンタクト領域14と、N型ドレインオフセット領域19と、N+型ドレインコンタクト領域20と、N型ドレインオフセット領域19とP型ボディー領域12との間の局所的な領域に形成されたN型ドレインバッファ領域18とを有し、N型ドレインバッファ領域18はLOCOS酸化膜5aのソース側の端部と接し、N型ドレインオフセット領域19よりも浅い。

(もっと読む)

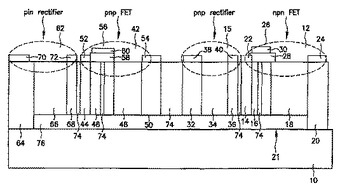

横型絶縁ゲートバイポーラPMOS装置

横型絶縁ゲートバイポーラPMOS装置(20b)は、半導体基板(22)と、埋め込み絶縁層(24)と、埋め込み絶縁層上のSOI層内に、p導電型のソース領域を有する横型PMOSトランジスタ装置とを含む。n導電型の横方向ドリフト領域(32)が本体領域(30)近傍に設けられ、p導電型のドレイン領域がドリフト領域により本体領域から横方向に分離されて設けられている。n導電型ドレイン領域(34b)が、p反転バッファ内に挿入されたシャローn型コンタクト表面領域として形成される。動作中にチャネル領域が形成され、本体領域(30)近傍の横方向ドリフト領域(32)の一部分の上部に延在する本体領域(30)の一部分の上部にゲート電極(36)が設けられている。ゲート電極(36)は絶縁領域(38)により本体領域(30)とドリフト領域(32)とから絶縁されている。  (もっと読む)

(もっと読む)

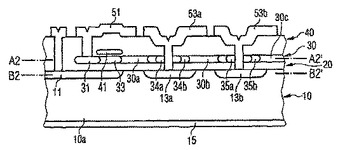

半導体装置

【課題】同一なチップ内でNチャネルおよびPチャネルの両チャネルが高い耐圧特性を有する高耐圧MOSトランジスタを実現でき得るデバイス構造の製造方法を提供する。

【解決手段】本発明は、Nch型L−DMOS101 とPch型L−DMOS102と論理部103 から成る半導体装置であり、Nch型L−DMOS101 は、N型ドリフト領域12、Pウエル19、P型高濃度拡散層20、ソース拡散層21、ドレイン拡散層22、ソースコンタクト14、ドレインコンタクト16、ソース電極配線15、ドレイン電極17、ゲート電極18の各主要素から成り、SOI領域であるN型ドリフト領域12に形成されたこのNch型L−DMOS101のソース電極14と、領域11と、を電気的に導通して同電位になるように構成するデバイス構造である。

(もっと読む)

SOIトレンチ横型IGBT

【課題】IGBTにおいて、高耐圧で、大電流での駆動を可能とし、ラッチアップ耐量を高くし、単位面積あたりのオン抵抗を低くすること。

【解決手段】n+エミッタ領域6aとp+コレクタ領域12aとの間のウェハ全面にトレンチ16a,16bを形成し、その中をトレンチ埋め込み絶縁膜17で埋めることによって、耐圧を担持するドリフト領域を折り曲げて、実効的なドリフト長を長くする。トレンチ埋め込み絶縁膜17内に、エミッタ側フィールドプレート15を埋め込み、トレンチ埋め込み絶縁膜17のエミッタ側に生じる横電界を遮蔽することによって、n-ドリフト領域3aとpベース領域4aとのPN接合で発生する電界を緩和する。

(もっと読む)

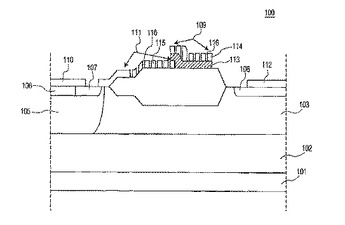

テーパ状単位セル金属酸化物半導体高電圧デバイス構造

電界効果電子デバイス(100,600)(例えばVDMOS等のFET)は、誘電体層(104,608)に隣接して配置されたフィールドプレート(105,607)を有しており、当該フィールドプレートは、半導体層(103,602)に隣接して配置されている。この場合、デバイスのドリフト領域は半導体層中にある。ドーピングレベルはドリフト領域に亘って略非線形的に変化し、デバイスは略一定の低減された表面電界を示す。電界効果デバイスの製造方法は、デバイスの半導体層のドリフト領域に非線形で不均一なドーピング密度を与えることを含んでいる。この場合、半導体層及び誘電体層の両方が一定でない厚さを有している。誘電体層は、low−k誘電材料によって形成され得る。  (もっと読む)

(もっと読む)

コンプリメンタリ横型窒化物トランジスタ

基板の支持表面上に形成された、横方向に隣接した導電性半導体領域により構成された横方向に延びているスタックを備える半導体デバイスおよびそのデバイスを作製する方法。  (もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

絶縁耐力の高いSOI半導体素子

本発明は、第1半導体域と第2半導体域との間に配置されたフィールド電極および/またはフィールド領域を備えた、SOI半導体素子に関するものである。電気的結合を、フィールド電極とフィールド領域との間で行うことができる。  (もっと読む)

(もっと読む)

絶縁された金属領域を備えたフィールドプレートを有する横方向薄膜SOIデバイス

横方向薄膜シリコン−オン−インシュレータ(SOI)デバイスにおいて、フィールドプレートは、パッケージ及び表面電荷効果からデバイスを保護するために横方向ドリフト領域に亘って実質的に延在するように設けられている。特に、フィールドプレートは、シリコンドリフト領域にドーピング量勾配により形成される横方向電界分布を呈するように、スペーシングにより相互に横方向において絶縁される複数の金属領域からなる層を備えている。  (もっと読む)

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

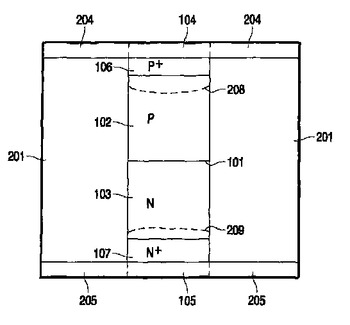

高絶縁破壊電圧を有する半導体装置

半導体装置、例えば、pn接合(101)を有するダイオード(200)がこのpn接合の近傍に、そして、これを跨ぐこともある絶縁材料の電界形成領域(201)を有する。電界形成領域(201)は好ましくは高誘電率を有し、容量性電圧結合領域(204,205)を介してpn接合に印加されるのとほぼ同じ電圧に結合される。pn接合(101)間に逆電圧が印加され且つ装置が非道通時に、電界形成領域(201)が存在しない場合に存在しうるpn接合空乏領域の限界を超えて延びる電界形成領域の一部分に容量性電界が存在し、電界形成領域内の電界が拡張された電界を誘起し、この拡張された電界は対応して拡張されたpn接合空乏領域(208,209)までとされ、装置の逆絶縁破壊電圧を増加させる。  (もっと読む)

(もっと読む)

441 - 451 / 451

[ Back to top ]