Fターム[5F110DD14]の内容

Fターム[5F110DD14]に分類される特許

201 - 220 / 2,817

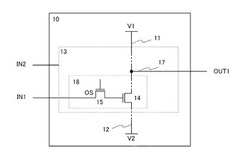

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置

【課題】電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なプログラマブルなアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルを複数並列に接続されたプログラマブル回路とし、ユニットセル毎に導通または非導通の切り替えを行う。また、当該ユニットセルのスイッチとして、オフ電流を十分に小さくすることができる第1のトランジスタと、ゲート電極が第1のトランジスタのソース電極又はドレイン電極と電気的に接続された第2のトランジスタと、を含む構成とし、当該第2のトランジスタのゲート電位によってユニットセルの導通または非導通を制御する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用いたnチャネルTFTのみを用いてバッファ回路やインバータ回路などを構成することを課題の一つとする。

【解決手段】ソース電極及びドレイン電極の両方がゲート電極に重なる第1のトランジスタと、ソース電極はゲート電極と重ね、且つ、ドレイン電極はゲート電極と重ならない第2のトランジスタとを組み合わせてバッファ回路やインバータ回路などを構成する。第2のトランジスタをこのような構造とすることによって、容量Cpを小さくし、電位差VDD−VSSが小さい場合でもVA’が大きくとれるようになる。

(もっと読む)

半導体装置

【課題】ラッチ型メモリが搭載されたCPUを動作させるに際して、処理内容に応じて常時記憶方式と終了時記憶方式のいずれかを選択し、ラッチ型メモリが搭載されたCPUの消費電力を低減する。

【解決手段】ラッチ型メモリが搭載されたCPUを動作させるに際して、電源のオンオフの繰り返し動作が多い場合には常時記憶方式とし、電源のオンオフの繰り返し動作が少ない場合には終了時記憶方式とする。常時記憶方式と終了時記憶方式のどちらを選択するかは、消費電力に応じて決定したしきい値をもとにして決定する。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体装置

【課題】パワーデバイスである大電力用途向けの電界効果トランジスタにおいて、特性の良好な電界効果トランジスタを提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆うゲート絶縁層と、第1のゲート電極と重畳して、且つゲート絶縁層と接する酸化物半導体層と、酸化物半導体層の端部を覆うキャリア密度の高い酸化物半導体層と、キャリア密度の高い酸化物半導体層と接するソース電極及びドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層を覆う絶縁層と、絶縁層と接し、且つ、ソース電極及びドレイン電極の間に設けられる第2のゲート電極と、を有し、キャリア密度の高い酸化物半導体層は、酸化物半導体層を介して対向し、且つ酸化物半導体層の端部の上面、下面、及び側面のそれぞれ一部、並びにゲート絶縁層の上面一部と接する半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料を用いたトランジスタと、第1の半導体材料とは異なる第2の半導体材料を用いたトランジスタと、容量素子とを有する複数のメモリセルを有し、書き込み期間にソース線に電源電位を供給する機能を有する電位切り替え回路を備えた半導体装置とする。これにより、半導体装置の消費電力を十分に抑えることができる。

(もっと読む)

表示装置

【課題】酸化物半導体を用いたトランジスタを有する表示装置において、寄生容量を軽減する。表示装置において、解像度の向上や、高精細化といった高性能化及び高品質化を達成する。

【解決手段】ボトムゲート型のトランジスタにおいて、酸化物半導体膜と重畳して設けられるゲート電極が第1のゲート電極と第2のゲート電極とに間隔を有して分割して設けられる。第1のゲート電極はソース電極又はドレイン電極の一方と重畳して設けられ、第2のゲート電極はソース電極又はドレイン電極の他方と重畳して設けられる。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】トランジスタの損傷、破壊の発生を抑制することができる半導体装置を提供する。

【解決手段】第1の基板11上の第1の絶縁層12と、第1の絶縁層上のトランジスタ13と、トランジスタ上の第2の絶縁層14と、第2の絶縁層14に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に接続された第1の導電層15〜18と、第1の導電層上の第3の絶縁層38と、第3の絶縁層38上の第2の基板19と、を有し、トランジスタは、半導体層20と、第2の導電層22と、半導体層20と第2の導電層22の間に設けられた第4の絶縁層21とを有し、第1の絶縁層12、第2の絶縁層14、第3の絶縁層38及び第4の絶縁層21から選択された一つ又は複数は、トランジスタと重ならないように設けられた段差部を有する。

(もっと読む)

EL表示装置および電子機器

【課題】画素部と同じ絶縁基板上において、大きな電流供給能力が得られるトランジスタで構成される電源線駆動回路を備えたEL表示装置を提供する。

【解決手段】絶縁基板上に複数の画素と複数の信号線、複数の走査線、及び複数の電源線を有するアクティブマトリクス型表示装置において、前記絶縁基板上に電界効果移動度が少なくとも80cm2/Vs以上、好ましくは120cm2/Vs以上を有する酸化物半導体のトランジスタを有し、トランジスタを1つの構成要素とする電源線駆動回路を有するEL表示装置である。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

201 - 220 / 2,817

[ Back to top ]