Fターム[5F110DD14]の内容

Fターム[5F110DD14]に分類される特許

2,801 - 2,817 / 2,817

液晶装置及び電子機器並びに投射型表示装置

【課題】 アクティブマトリクス駆動方式の液晶装置において、プリチャージ回路、サンプリング回路等が有するTFTの下側からの戻り光等に対する遮光性能を高め、優れたスイッチング特性により高品質の画像表示を行う。

【解決手段】 液晶装置(200)は、一対の基板間に挟持された液晶層(50)と、基板にマトリクス状に設けられた画素電極(11)と、これをスイッチング制御するTFT(30)とを備える。このTFTや、プリチャージ回路(201)及びサンプリング回路(301)のTFTの下側には、遮光層が設けられている。

(もっと読む)

ナノ構造単層の形成方法および形成デバイスならびにかかる単層を含むデバイス

ナノ構造配列の形成またはパターニング法が提供される。この方法は、ナノ構造会合基を含んでなるコーティング上での配列形成、レジストを使用するパターニングおよび/または配列形成を促進するデバイスの使用を含む。またナノ構造配列を含むデバイス(例えばメモリーデバイス)のように、ナノ構造配列の形成のための関連デバイスも提供される。 (もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

金属トランジスターデバイス

本発明はトランジスターデバイスのチャネル領域の絶縁基板上に形成される金属薄膜あるいは複合金属層が含まれるデプレッションあるいはエンハンスメントモードの金属トランジスターに関する。

(もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

スペーサによって定められる通路内で成長した半導体ナノチューブを組み込んだ垂直型電界効果トランジスタ

【課題】 ICチップの大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込んだ垂直型FET構造体を提供する。

【解決手段】 少なくとも1つの半導体ナノチューブによって定められたチャネル領域を有する垂直型電界効果トランジスタ、及び、こうした垂直型電界効果トランジスタを、スペーサによって定められるチャネルを用いて化学気相成長法によって製造する方法である。各々のナノチューブは、スペーサとゲート電極との間に定められる高アスペクト比通路の底部に位置決めされた触媒パッドにより触媒される化学気相成長法によって、成長する。各々のナノチューブは、スペーサによる境界の存在によって制限される垂直配向を持つ通路内で成長する。通路の開口部から離れたスペーサの底部に、隙間が設けられる。隙間を通って触媒パッドに流れる反応物質が、ナノチューブの成長に関与する。

(もっと読む)

スタック状テンプレート層の局部的なアモルファス化及び再結晶化によって形成される、選択された半導体結晶配向を有するプレーナ型基板

【課題】 異なる配向の半導体が共通のBOX層上に配置された、プレーナ型ハイブリッド配向半導体基板構造体を形成するための、より簡単で優れた方法を提供すること。

【解決手段】 異なる結晶配向の半導体層を有するプレーナ型基板を製造するための、スタック状テンプレート層の局部的なアモルファス化及び再結晶化を用いる方法が提供される。本発明の方法を用いて構築されるハイブリッド配向半導体基板構造体、及び、デバイスの性能を高めるために異なる表面配向上に配置された少なくとも2つの半導体デバイスを含む種々のCMOS回路と一体化されたこうした構造体が提供される。

(もっと読む)

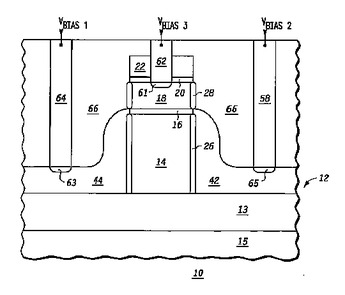

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

絶縁構造部上の半導体チャンネル

半導体装置基板上に貫通誘電体層を形成するステップと、貫通誘電体層の上部にトレンチ誘電体層を形成するステップと、貫通誘電体層を露出させるため、トレンチ誘電体層を貫通する溝を形成するステップと、基板を露出させるため、前記溝内の貫通誘電体層に貫通孔を形成するステップと、溝内および前記貫通孔内に半導体材料を形成するステップと、を有する方法を示した。装置基板と、該装置基板の表面に形成された誘電体層と、誘電体層上に形成された、装置基板と相間する結晶構造を有する装置基部と、を有する装置を示した。  (もっと読む)

(もっと読む)

表示装置及びその製造方法

【課題】表示品質と画像取込み性能に優れた表示装置及びその製造方法を提供する。

【解決手段】表示装置の製造工程にてTFT11のチャネル部とフォトダイオードD1,D2のI層をともに水素化する際、TFT11とフォトダイオードD1,D2とで水素化の進行に違いが出るようにして、TFT11のチャネル部の欠陥密度を少なくし、かつフォトダイオードD1,D2のI層の欠陥密度を多くする。これにより、TFT11のリーク電流が抑制され、フォトダイオードD1,D2の光に対する感度を向上できる。

(もっと読む)

シリコン結晶化方法

【課題】 短い時間で良質の結晶成長をなすことができるポリシリコンの結晶化方法を提供する。

【解決手段】 非晶質シリコン薄膜が蒸着された基板110にあって、固定手段とレーザー発生装置間の遮断領域と階段状の透過領域で構成されたマスクにレーザービームを照射して、前記非晶質シリコン薄膜に照射された領域が溶融した領域との界面でグレーンが各々成長して、第1グレーン領域114aと核生成領域と第2グレーン領域114bで構成された階段状の領域を形成する第1結晶化段階と;前記マスクを横長さだけ移動して、同一な照射した後に再結晶化して、重畳された部分のグレーンが成長して、横方向に新しい結晶領域が形成される第2結晶化段階を含む方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

D/A変換回路及び半導体装置

【課題】 高いビット数のデジタル信号に対応し、線形性が良く、占有面積の小さいD/A変換回路を提供する。

【解決手段】 複数の容量を有するD/A変換回路であって、複数の容量は、第1電極と、第1電極に接している第1誘電体と、第1誘電体に接している第2電極と、第2電極に接している第2誘電体と、第2誘電体に接している第3電極とをそれぞれ有しており、第2電極は、第1電極及び第3電極と重なっており、第2電極は、第1電極及び第3電極と重なっている部分において開口部を有しており、第2電極が有する開口部において、第1誘電体及び第2誘電体にコンタクトホールが形成されており、コンタクトホールを介して第1電極と第3電極が接続されていることを特徴とするD/A変換回路。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

半導体装置の製造方法

【課題】 優れた特性を有する多結晶シリコン膜を備えた半導体装置を高い歩留まりで製造することが可能な半導体装置の製造方法を提供する。

【解決手段】 石英ガラスや無アルカリガラスなどの基板1上に、非晶質シリコン膜2aを形成する。その非晶質シリコン膜2a上にWシリサイド膜(導電膜)4bを形成する。そして、Wシリサイド膜(導電膜)4bに対し、高周波やYAGレーザービームなどの電磁波を照射することにより、Wシリサイド膜(導電膜)4bを発熱させ、この熱を利用して、非晶質シリコン膜2aを多結晶シリコン膜2に変える。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

2,801 - 2,817 / 2,817

[ Back to top ]