Fターム[5F110DD24]の内容

Fターム[5F110DD24]の下位に属するFターム

処理 (504)

Fターム[5F110DD24]に分類される特許

201 - 220 / 371

NMOS及びPMOSトランジスタそれぞれのチャネルに同時に引っ張り及び圧縮歪みを与えるための方法

【課題】同一支持体上に第一歪みによる歪みが与えられた少なくとも一つの半導体領域と、第二歪みとは異なる第二歪みによる歪みが与えられた少なくとも一つの半導体領域とを備えたマイクロエレクトロニクス装置の製造方法を提供する。

【解決手段】プレ歪み層上の半導体領域の形成、その後の、プレ歪み層の厚さにわたって延伸するトレンチの形成が含まれ、トレンチのレイアウト及び寸法の関数としての半導体領域の寸法及びレイアウトは、プレ歪み層と同じ種類の歪みを有する半導体領域及びプレ歪み層のものとは異なる種類の歪みを有する半導体領域が得られるようにされる。

(もっと読む)

半導体装置の作製方法

【課題】動作性能及び信頼性を向上させた半導体装置の作製方法を提供する。

【解決手段】単結晶シリコン基板の一部からなる単結晶シリコン薄膜を、単結晶シリコン基板を熱酸化して得られた第1の酸化シリコン膜上に有し、第1の酸化シリコン膜が、シリコン基板上に設けられた第2の酸化シリコン膜に貼り合わされたシリコン基板を用いる半導体装置の作製方法であって、単結晶シリコン薄膜から複数の島状シリコン層を形成し、複数の島状シリコン層の熱酸化工程後に、複数の島状シリコン層上にポリシリコンでなるゲート電極を形成し、ゲート電極の側面にサイドウォールを形成し、複数の島状シリコン層にソース領域及びドレイン領域を形成し、ゲート電極、ソース領域、ドレイン領域に金属膜を形成し、加熱してゲート電極、ソース領域、ドレイン領域にシリサイドを形成し、複数の島状シリコン層を覆って、層間絶縁膜を形成する半導体装置の作製方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】高電位基準回路部内で基準電位の急峻な変動がある場合であっても、周りのデバイス形成領域への影響(電位干渉)を抑制することができ、誤動作が生じ難い半導体装置、および該半導体装置の安価な製造方法を提供する。

【解決手段】埋め込み絶縁膜3を間に挟んで、主面側の第1半導体層1と裏面側の第2半導体層2とで構成される半導体基板11において、第1半導体層1に、低電位基準回路部と高電位基準回路部が設けられ、各デバイス形成領域Dが、絶縁分離トレンチ4によって互いに絶縁分離されてなる半導体装置20であって、第2半導体層2に、埋め込み絶縁膜3に達するようにして、多孔質シリコン領域P1が形成され、多孔質シリコン領域P1により仕切られて、第2半導体層2が、複数のフィールド領域F1,F2に分離され、フィールド領域F1,F2が、電位固定されてなる半導体装置20とする。

(もっと読む)

不揮発性半導体記憶装置及びその作製方法

【課題】書き込みや消去を繰り返し行った場合であっても、読み出し不良を抑制することを目的の一とする。又は、メモリトランジスタの面積の増大を抑制しつつ、書き込み電圧、消去電圧を低減することを目的の一とする。

【解決手段】基板上に設けられた書き込み動作及び消去動作に用いる第1の半導体層及び読み出し動作に用いる第2の半導体層上に、絶縁膜を介してフローティングゲートとコントロールゲートを設け、第1の半導体層を用いてフローティングゲートへの電子の注入・放出を行い、第2の半導体層を用いて読み出しを行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】内層配線が薄くても内層配線とビアとの間の優れた電気伝導性を得ることができる半導体装置およびその製造方法を提供する。

【解決手段】第1層と第2層との間に介在した所定の厚みの第1金属層と、前記第2層の表層に配置された第2金属層と、前記第1金属層、前記第1層及び前記第2層を貫通するビアホールと該ビアホールに形成された導電性組成物とからなるビアと、を具備し、前記ビアホールの外周に沿った第1金属層の端部は前記ビアホールの側面に接するように折れ曲がった形状であり、前記第1金属層の折れ曲がった表面で前記導電性組成物に導通している半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFETダイオードのチャネル幅を効率良く広げることができ、レイアウトの利用効率を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】Si基板1上に絶縁層3を介して形成されたSi層5と、Si層5上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、平面視で複数の環状体151,152a〜152dが接触した形状である第1の部位15aを有するゲート電極15と、第1の部位15aをなす各環状体151,152a〜152dの内側と外側のSi層5にそれぞれ形成されたS/D層17,18と、S/D層18とゲート電極15とを接続する配線31と、を備える。このような構成であれば、アクティブ領域のSi層5に、多数の環状のチャネル領域を形成することができ、MOSFETダイオードのチャネル幅を効率良く広げることができる。

(もっと読む)

半導体装置

【課題】動作性能及び信頼性を大幅に向上することができる半導体装置を提供することを課題とする。

【解決手段】シリコン基板上に設けられた酸化シリコン膜と、単結晶シリコン基板の一部よりなりTFTの活性層となる島状シリコン層を熱酸化して得られ、酸化シリコン膜に貼り合わせ界面にて貼り合わせて設けられた酸化シリコン膜と、活性層を熱酸化して設けられた他の面の酸化シリコン膜とにより取り囲まれた活性層と、活性層上に設けられたゲート電極と、を有する半導体装置を提供する。

(もっと読む)

有機半導体装置の製造方法及び素子基板

【課題】可撓性の高い有機半導体装置の製造方法及び素子基板を提供する。

【解決手段】有機半導体装置11の製造方法は、可撓性を有する樹脂基板4の一方の主面4aにガラス基板からなる遮蔽基板6を固着するとともに、樹脂基板4の他方の主面4bにガラス基板からなる支持基板2を接着して素子基板1を作製する工程と、有機半導体層14を有する有機EL素子である有機半導体素子12を素子基板1の遮蔽基板6上に形成する工程と、支持基板2を素子基板1Aから除去する工程とを備えている。

(もっと読む)

半導体装置の作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置、および、その製造方法

【課題】広帯域での利得、および、低い歪み特性を実現する。

【解決手段】第1のフィンF1における閾値電圧Vthと、第2のフィンF2a,F2bにおける閾値電圧Vthと、第3のフィンF3a,F3bにおける閾値電圧Vthとのそれぞれが互いに異なるように、finFET100を形成する。

(もっと読む)

単結晶半導体膜の結晶性評価方法及び半導体基板の作製方法

【課題】良好な結晶性を有し高性能な半導体素子を形成することを可能とする半導体基板を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定し、単結晶半導体層にレーザ光を照射し、単結晶半導体層を部分溶融状態として再結晶化し、結晶欠陥を修復する。再結晶化後の単結晶半導体層は深さ方向の濃度分布において、炭素濃度が極大を有する。

(もっと読む)

半導体装置の作製方法及び電子書籍の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する半導体装置を作製するための技術を提供する。

【解決手段】分離層を有する固定基板上に樹脂基板を形成する工程と、前記樹脂基板上に少なくともTFT素子を形成する工程と、前記分離層にレーザー光を照射することにより、前記分離層の層内または界面において前記固定基板から前記樹脂基板を剥離する工程とを行い、前記樹脂基板を用いた柔軟性を有する表示装置を作製する。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び表示装置

【課題】静電気による帯電を防止し、素子破壊による不良発生を低減させることができる薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ基板1を製造する各処理工程に長尺プラスチック基板10をロール・ツー・ロールで供給、巻き取りを行いながらその長尺プラスチック基板10の一方の面S1に薄膜トランジスタ50を形成する薄膜トランジスタ基板1の製造方法であって、少なくとも長尺プラスチック基板10の一方の面S1に薄膜トランジスタ50を形成する前に、長尺プラスチック基板10の他方の面S2の全面に導電膜2を形成する。

(もっと読む)

フィルムデバイス製造用支持体、およびこれが用いられたフィルムデバイスの製造方法

【課題】フィルム基材上に微小なデバイスを高精度で作製し、性能に優れたフィルムデバイスを作製することが可能なフィルムデバイス製造用支持体を提供することを主目的とする。

【解決手段】フィルムデバイス製造用支持体を用い、上記フィルムデバイス製造用支持体上にフィルム基材を貼り合わせる工程と、上記フィルム基材上にデバイスを製造する工程とを有し、上記フィルム基材上に複数のデバイスが形成されたフィルムデバイスを製造する、フィルムデバイスの製造方法に用いられるフィルムデバイス製造用支持体であって、基材と、上記基材上にパターン状に形成され、粘着性樹脂からなり、上記フィルム基材を剥離可能なように粘着させることが可能な粘着層と、を有することを特徴とする、フィルムデバイス製造用支持体を提供することにより、上記課題を解決するものである。

(もっと読む)

SOI基板の作製方法

【課題】複数の半導体基板をベース基板に貼り合わせる場合であっても、貼り合わせ効率を向上すると共に、接合不良を抑制することを目的とする。

【解決手段】第1の基板支持台上に複数の半導体基板を設け、第2の基板支持台上にベース基板を設け、複数の半導体基板の表面とベース基板の表面が所定の間隔をもって対向するように、第1の基板支持台の上方に第2の基板支持台を配置し、複数の半導体基板又はベース基板を帯電させ、複数の半導体基板の表面とベース基板の表面の間隔を狭めることにより、ベース基板の表面に複数の半導体基板を接触させ、ベース基板の表面と複数の半導体基板の表面を接合させる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い単結晶半導体層及び半導体装置を、少ない作製工程で得ることを課題とする。

【解決手段】絶縁膜が形成された単結晶半導体基板に、イオンビームを照射し、前記単結晶半導体基板中に損傷領域を形成し、液状ガラスよりも密度の高い液体上に、前記液状ガラスを浮かべて板状にし、前記板状の液状ガラス上に、前記損傷領域が形成された単結晶半導体基板を、前記絶縁膜と前記液状ガラスが向き合うように配置し、前記板状の液状ガラスと前記単結晶半導体基板を徐冷することにより、前記板状の液状ガラスからガラス基板を形成すると同時に、前記ガラス基板と前記単結晶半導体基板を接合させ、前記損傷領域に沿って、前記単結晶半導体基板から単結晶半導体層を分離する半導体装置の作製方法に関する。

(もっと読む)

SOI基板の作製方法

【課題】半導体基板とベース基板の貼り合わせを低温で行う場合であっても、半導体基板とベース基板との接合強度を十分に向上させることを目的の一とする。

【解決手段】半導体基板と、絶縁体でなるベース基板とを用意し、半導体基板上に塩素原子を含有する酸化膜を形成し、酸化膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板の表面から所定の深さの領域に脆化領域を形成し、半導体基板上の酸化膜に対してバイアス電圧を印加してプラズマ処理を行い、単結晶半導体基板の表面とベース基板の表面とを対向させ、酸化膜の表面とベース基板の表面とを接合させ、酸化膜の表面とベース基板の表面とを接合させた後に熱処理を行い、脆化領域を境として分離することにより、ベース基板上に酸化膜を介して半導体膜を形成する。

(もっと読む)

半導体装置、および、その製造方法

【課題】フィンの数に応じた電流比で電流を流す場合に、その電流比の精度を向上させる。

【解決手段】第1のfinFET100と、第2のfinFET200と、第3のfinFET300とについて、ドレイン電流の値に応じてフィンの数を増加させるが、第1のfinFET100と、第2のfinFET200と、第3のfinFET300とのそれぞれにおいて、一対のソース・ドレイン領域に接続させるコンタクトを同一の数にする。

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板やプラスチックなど可撓性を有する基板を用いた場合にも、実用に耐えうるSOI層を備えたSOI基板を歩留まり高く作製する方法を提供することを目的の一とする。また、そのようなSOI基板を用いた薄型の半導体装置を歩留まり高く作製することを提供することを目的とする。

【解決手段】可撓性を有し且つ絶縁表面を有する基板に、単結晶半導体基板を接合し、単結晶半導体基板を剥離してSOI基板を作製するに際し、接合面の一方若しくは双方を活性化した後、可撓性を有し且つ絶縁表面を有する基板と、単結晶半導体基板とを圧着する。

(もっと読む)

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

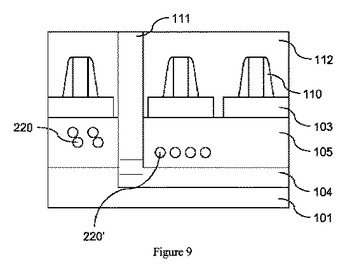

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

201 - 220 / 371

[ Back to top ]