Fターム[5F110DD24]の内容

Fターム[5F110DD24]の下位に属するFターム

処理 (504)

Fターム[5F110DD24]に分類される特許

141 - 160 / 371

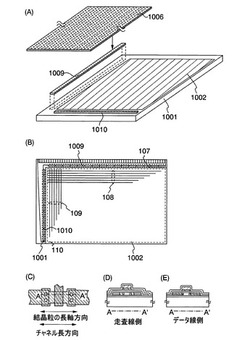

液晶表示装置の作製方法

【課題】生産性を向上させた液晶表示装置及びその作製方法の提供する。

【解決手段】走査線とデータ線が絶縁層を介して交差する領域に、非晶質半導体又は有機半導体をチャネル部とする第1の薄膜トランジスタを有する第1の基板と、第2の基板と、第1の基板と第2の基板の間の液晶層と、結晶質半導体をチャネル部とする第2の薄膜トランジスタを有する第3の基板を有し、結晶質半導体は第2の薄膜トランジスタにおける電子又は正孔が流れる方向に沿って結晶粒界が延び、第1の基板と第2の基板は第1の基板が露出するように貼り合わされ、第3の基板は第1の基板上の露出した領域に貼り合わされ、第3の基板上には第2の薄膜トランジスタを形成する第1の領域と入出力端子を形成する第2の領域が設けられ、第3の基板の短辺は1乃至6mm、第1の領域の短辺は0.5乃至1mmである。

(もっと読む)

ナノワイヤデバイスの絶縁

本開示は、マイクロ電子デバイスの製造の分野に関する。少なくとも1つの実施形態において、本願の特徴は、絶縁されたナノワイヤの形成に関し、ナノワイヤに隣接する絶縁構造は、マイクロ電子構造をその上面に形成するために、実質的に平坦な表面となっている。 (もっと読む)

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

非線形素子、該非線形素子を有する表示装置および該表示装置を有する電子機器

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トランジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができる。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジスタの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリコン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置並びにその半導体装置を内蔵する多層基板

【課題】dv/dtサージにより、寄生容量を充放電する変位電流の発生を抑制できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】低電位基準回路部LV、高電位基準回路部HV、レベルシフト回路部LSを形成したSOI基板の半導体層の主面上にサポート部材を貼り付け、支持基板を除去する。次いで、回路部と対向するように絶縁部材を半導体層の裏面上に固定した後、サポート部材を剥がす工程と、チップ内にLV,HV,LSが含まれるように絶縁部材の固定された半導体層をダイシングする工程を経る。そして、サポート部材を剥がし、チップ化した半導体層を、絶縁部材を挟んで、第1のリードがLVと、第2のリードがHVと対向するように、第1リード及び第2リード上に固定するとともに、第1のリードとLVにおける第1の電位が印加される部位を電気的に接続し、第2のリードとHVにおける第2の電位が印加される部位を電気的に接続する。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】金属箔から成る支持層、支持層の上に形成された半導体構造部、および半導体構造部の上に形成された樹脂フィルムを有して成るフレキシブル半導体装置。かかるフレキシブル半導体装置では、樹脂フィルムには開口部が形成されており、その開口部に半導体構造部の表面と接触する導電部材が形成されており、半導体構造部が半導体層および半導体層の表面に形成された絶縁層を有して成る。

(もっと読む)

半導体装置の駆動方法

【課題】電荷蓄積層での電子の蓄積または放出が十分でない場合に、不揮発性メモリ素子に保持された記憶状態の正誤を判定し、誤ったデータを読み出すことによる不良を低減する。

【解決手段】メモリセル領域104と、テスト領域105と、を含む半導体記憶回路103と、制御回路と、を有し、制御回路は、メモリセルへのデータの書き込み、第1の領域105Aへの第1の記憶状態の書き込み、または第2の領域105Bへの第2の記憶状態の書き込みを行うための第1の動作を行い、第1の領域及び第2の領域からの第1の記憶状態または第2の記憶状態の読み出しを行うための第2の動作を行い、メモリセルからのデータの読み出しを行うための第3の動作を行い、第2の動作において、第1の領域からの読み出しが第1の記憶状態であるか、または第2の領域からの読み出しが第2の記憶状態であるかに応じて、第3の動作の正誤を判定する。

(もっと読む)

半導体装置の製造方法

【課題】寄生MOSの形成を抑制し、且つ狭チャネル化を低減した半導体装置の製造方法を提供する。

【解決手段】支持基板2と絶縁層3と半導体層4とを含むSOI基板1に、ソース領域及びドレイン領域が第1導電型であるトランジスターを形成する半導体装置の製造方法であって、半導体層4上に、第1の耐酸化性膜6a’を形成する工程と、第1の耐酸化性膜6a’をマスクにして、第1導電型とは導電性の異なる、第2導電型の不純物7を半導体層4に注入する工程と、第2導電型の不純物7を半導体層4に注入する工程の後、第1の耐酸化性膜6a’の側面に第2の耐酸化性膜6b’を形成する工程と、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’をマスクにして、素子分離層8を形成する工程と、素子分離層8を形成する工程の後、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’を半導体層4上から除去する工程とを有することを特徴とする半導体装置100の製造方法。

(もっと読む)

半導体装置

【課題】半導体膜に混入する不純物濃度を制御した活性層を有する半導体回路を備えた半

導体装置を提供するものである。

【解決手段】上記目的を解決するため、ガラス基板上に200nm〜500nmの膜厚の

第1の窒化珪素膜と、前記第1の窒化珪素膜上に第2の窒化珪素膜と、前記第2の窒化珪

素膜上にチャネル形成領域となる領域を含む非晶質半導体膜と、を有する構成において、

前記第1の絶縁膜と前記第2の絶縁膜との界面において、ボロンを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5ラ1010dyn/cm2 〜5ラ1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

誘電体分離型半導体装置とその製造方法

【課題】耐圧が維持されるとともに絶縁耐量の高いワイヤ配線が電極に配線される誘電体分離型半導体装置を提供する。

【解決手段】誘電体分離型半導体装置は、支持基板、埋込誘電体層および半導体基板から構成される誘電体分離型基板を具備し、半導体基板は、選択的に形成される第1半導体領域と、第1半導体領域をその外周縁から所定の距離だけ離間して取り囲むように設けられる第2導電型の第2半導体領域と、第1半導体領域に接合される第1主電極と、第2半導体領域に接合される第2主電極と、を備え、支持基板は、第1半導体領域に重畳する領域を内包する位置に貫通孔と、貫通孔の開口に現れる埋込誘電体層の領域に接して配設されるシリコーンラダーポリマー層と、貫通孔の開口に現れる埋込誘電体層の領域、シリコーンラダーポリマー層に接して配設される裏面電極と、シリコーンラダーポリマー層に囲まれる空間を埋めて平坦化する第1ハンダと、を備える。

(もっと読む)

半導体装置及び電子機器

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイン電極に接触しない。

(もっと読む)

半導体基板、半導体装置及び半導体装置の製造方法

【課題】半導体層の界面に生じるダングリングボンドをフッ素で終端することで、界面準位を低減することができ、また、低熱履歴のプロセスでも活性領域のみへ効率よくフッ素を導入することができる半導体基板を提供する。

【解決手段】フッ素拡散防止膜6と該フッ素拡散防止膜6上に形成されたフッ素を含有するシリコン酸化膜7からなる絶縁層9と、前記絶縁層9上に形成された半導体層8と、を含み、前記半導体層8とフッ素を含有する前記シリコン酸化膜7とが接触していることを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

薄膜トランジスタ搭載基板、その製造方法及び画像表示装置

【課題】活性層として用いた酸化物薄膜の安定化と高品質化を実現した薄膜トランジスタをプラスチック基板上に搭載した薄膜トランジスタ搭載基板の製造方法を提供する。

【解決手段】プラスチック基板10の上又はその上方に活性層となるアモルファス酸化物薄膜13を形成する工程と、少なくとも活性層となる部分のアモルファス酸化物薄膜13に向けてパルスレーザー20を照射する工程とを少なくとも有する。パルスレーザー20の照射工程は、プラスチック基板10に該プラスチック基板のガラス転移温度以上の温度を一定時間加えず、且つアモルファス酸化物薄膜13をアモルファス相のままで所定の比抵抗に制御する工程である。

(もっと読む)

薄膜装置、薄膜装置を備えた可撓性回路基板、及び薄膜装置の製造方法

【課題】剥離層、基板、又は設置面等の帯電による影響を受けない、回路動作が安定した薄膜装置を提供すること。

【解決手段】本発明の薄膜装置は、基板と、前記基板の上に形成された、導電性を有する電界遮蔽板と、前記電界遮蔽板の上に形成された、薄膜素子を含む能動層と、を備え、前記電界遮蔽板は、前記薄膜素子のいずれか電極の電位又は接地電位に接続されていることを特徴とする。

(もっと読む)

141 - 160 / 371

[ Back to top ]