Fターム[5F110DD24]の内容

Fターム[5F110DD24]の下位に属するFターム

処理 (504)

Fターム[5F110DD24]に分類される特許

121 - 140 / 371

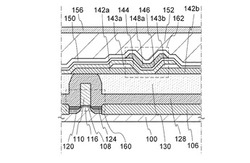

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタと、酸化物半導体以外の半導体材料を用いたトランジスタとを積層して、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第1のトランジスタ上に絶縁層と、絶縁層上に第2のトランジスタと、を有し、第1のトランジスタは、第1のチャネル形成領域を含み、第2のトランジスタは、第2のチャネル形成領域を含み、第1のチャネル形成領域は、第2のチャネル形成領域と異なる半導体材料を含んで構成され、絶縁層は、二乗平均平方根粗さが1nm以下の表面を有する半導体装置。

(もっと読む)

半導体装置およびその駆動方法

【課題】フォトセンサを有する半導体装置において、高分解能で撮像が行えるフォトセンサを提供する。

【解決手段】フォトダイオード204は光の強度に応じて電気信号を生成する機能を有し、第1のトランジスタ205はゲートに電荷を蓄積し、蓄積された電荷を出力信号に変換する機能を有し、第2のトランジスタ207はフォトダイオード204から生成された電気信号を第1のトランジスタ205のゲートに転送し、かつ、第1のトランジスタ205のゲートに蓄積された電荷を保持する機能を有する。第1のトランジスタ205はバックゲートを有し、第2のトランジスタ207は、酸化物半導体層により形成されたチャネル形成領域を有する。

(もっと読む)

薄膜回路構造及びその製造方法並びに有機EL装置

【課題】回路構造のスペースを小さくして画素の微細化を達成できる、薄膜回路構造及びその製造方法を提供する。

【解決手段】基材1上の面内方向Xに、ゲート電極2、ゲート絶縁膜3、酸化物半導体膜4、ソース電極5s及びドレイン電極5dで少なくとも構成された隣り合う2以上の薄膜トランジスタ10A,10Bを有する薄膜回路装置12であって、前記2以上の薄膜トランジスタ10A,10Bは、共通するゲート絶縁膜3を有するとともに、ゲート絶縁膜3の下に第1の酸化物半導体膜4Aが設けられた第1の薄膜トランジスタ10Aと、ゲート絶縁膜3の上に第2の酸化物半導体膜Aが設けられた第2の薄膜トランジスタ10Bとを有するようにして、上記課題を解決した。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

電圧調整回路

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ゲートがソース又はドレインに電気的に接続され、ソース及びドレインの一方に第1の信号が入力され、チャネル形成層としてキャリア濃度が5×1014/cm3以下である酸化物半導体層を有するトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極にクロック信号である第2の信号が入力される容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成である。

(もっと読む)

トランジスタ及びその製造方法

【課題】キャリア移動度を高く、かつ、動作のための印加電圧を低くしつつ、オフ電流が低いトラジスタを提供すること。

【解決手段】基板上にて互いに離間したソース電極及びドレイン電極を有し、前記基板上における前記ソース電極と前記ドレイン電極との間にチャネル部を有し、前記チャネル部上に所定の間隔をおいてゲート電極を有し、前記チャネル部は、カーボンナノチューブ又はグラフェン若しくは金属ナノワイヤーよりなり、前記基板は、表面において、前記チャネル部と立体交差する複数の導体線が周期的にパターンニングされた導体パターンを有する。

(もっと読む)

表示装置の作製方法

【課題】表示装置の作製工程で紫外線の照射を行っても、酸化物半導体層を用いた薄膜トランジスタのしきい値電圧のシフトを低減させることができる、表示装置の作製方法を提供することを課題の一つとする。

【解決手段】少なくとも一回以上の紫外線の照射を行い、且つ酸化物半導体層を有する薄膜トランジスタをスイッチング素子として用いる、表示装置の作製方法において、全ての紫外線照射工程を終えた後で、紫外線照射による該酸化物半導体層のダメージを回復させる熱処理を行う表示装置の作製方法である。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

表示装置及び電子機器

【課題】表示装置に置いて、多階調表示を実現することを目的とする。

【解決手段】トランジスタ及び表示素子を有する画素がマトリクス状に配置された画素部と、前記トランジスタのゲートに電気的に接続されたゲートドライバと、前記トランジスタのソース又はドレインに電気的に接続されたソースドライバと、前記ソースドライバに信号を出力するデータ処理回路とを有し、前記トランジスタは、酸化物半導体を用いており、前記データ処理回路は、入力されるmビットのデジタルデータのうち、nビットのデジタルデータ(m、nは共に正の整数、かつm>n)を電圧階調に用い、(m−n)ビットのデジタルデータを時間階調に用いる表示装置である。

(もっと読む)

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

低寄生容量ボディ・コンタクト・トランジスタ

【課題】寄生ゲート容量の低いボディ・コンタクトSOI(semiconductor−on−insulator)金属ゲートを含むトランジスタを提供する。

【解決手段】ゲート・スタック(26)の金属部分がボディ・コンタクト領域の上方で除去され、SOI基板(12)のボディ・コンタクト領域(24)中のゲート誘電体(28)に接触するシリコン含有物質が形成される。これによって、ボディ・コンタクト領域上の有効ゲート誘電体厚さが5オングストローム(Å)よりも大きく増加する。この結果、ボディ・コンタクト領域における寄生容量が低下する。

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

絶縁ゲート型トランジスタ

【課題】酸化物半導体を用いた絶縁ゲート型トランジスタに関し、短チャネル効果を極力抑えることのできる構成を提供する。

【解決手段】絶縁ゲート型トランジスタのチャネル領域を形成する酸化物半導体層に、脱水または脱水素化の工程及び酸素を添加する工程を施してキャリア濃度が1×1012/cm3未満となる真性又は実質的に真性な半導体を使用し、酸化物半導体層に形成されるチャネルの長さが0.2μm以上3.0μm以下であって、酸化物半導体層の厚さが15nm以上30nm以下で、かつゲート絶縁層の厚さが20nm以上50nm以下もしくは、酸化物半導体層の厚さが15nm以上100nm以下で、かつゲート絶縁層の厚さが10nm以上20nm以下とすることで短チャネル効果を抑え、上記チャネル長の範囲でしきい値の変動量を0.5V未満とすることができる。

(もっと読む)

高分子基板及びその製造方法、並びに前記高分子基板を含む表示装置及びその製造方法

【課題】熱膨張率が低く、高温で脱ガスを減少させることができる表示装置用高分子基板を提供すると共に、前記高分子基板の製造方法を提供する。また、前記高分子基板を含む表示装置を提供すると共に、前記表示装置の製造方法を提供する。

【解決手段】420乃至600℃の温度で重量損失が初期重量に対して1%より小さい高分子基板、前記高分子基板を準備する段階及び前記高分子基板を350℃より高い温度で熱処理する段階を含む高分子基板の製造方法、及び前記高分子基板を含む表示装置、並びにその製造方法を提供する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

変調回路及びそれを備えた半導体装置

【課題】変調回路の消費電力を低減する。

【解決手段】変調回路は、負荷と、スイッチとして機能するトランジスタとを有し、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有し、前記トランジスタのオフ電流は、1×10−13A以下である。または、変調回路は、負荷と、スイッチとして機能するトランジスタと、ダイオードとを有し、前記負荷、前記トランジスタ、及び前記ダイオードは、アンテナの両端間に直列に接続されており、前記トランジスタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有し、前記トランジスタのオフ電流は、1×10−13A以下である。また、前記トランジスタのゲートに入力される信号により、当該トランジスタの導通・非導通が制御される。また、前記負荷は、抵抗、容量、または抵抗及び容量である。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置の製造方法、を提供する。

【解決手段】半導体装置の製造方法は、50nmを超え150nm以下の厚みを有し、第1の層7mと第2の層7nとを有する半導体膜7を形成する工程を備える。半導体膜7を形成する工程時、第1の層7mに含まれる水素の割合は、第2の層7nに含まれる水素の割合よりも小さい。半導体装置の製造方法は、半導体膜7を熱処理することによって、半導体膜7に含まれる水素を低減する工程と、ゲート絶縁膜17およびゲート電極21を形成する工程と、半導体膜7にソース領域9およびドレイン領域13を形成する工程と、半導体膜7を水素雰囲気中で熱処理することによって、半導体膜7に含まれる水素を0.5原子%以上10原子%以下に設定する工程とを備える。

(もっと読む)

121 - 140 / 371

[ Back to top ]