Fターム[5F110EE14]の内容

Fターム[5F110EE14]の下位に属するFターム

三層以上 (1,118)

Fターム[5F110EE14]に分類される特許

2,001 - 2,020 / 3,665

半導体装置、半導体装置の製造方法、半導体装置の設計方法、電気光学装置、電子機器、電気光学装置の製造方法及び電子機器の製造方法

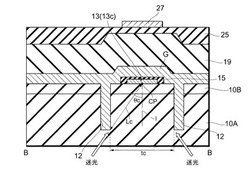

【課題】半導体装置の特性の向上、特に、遮光性の向上による光リーク電流の低減を図る。

【解決手段】本発明に係る半導体装置は、基材(10A,10B)と、基材上に形成され、第1方向に延在する半導体膜(13)と、半導体膜上にゲート絶縁膜(15)を介して形成され、第1方向と交差する第2方向に延在するゲート電極(G)と、半導体膜の両側に前記第1方向に延在するよう形成された一対の凹部(12)と、凹部内に配置された充填材料と、を有し、凹部の底面と半導体膜の底部の第1方向に延在する中心線(CP)との距離をLcと、凹部の底面間の距離をtcと、nを基材の屈折率とした場合、ntc2<488Lcを満たす。本構成によれば、上記凹部(12)により、基板側からの光の入射が制限され、光リーク電流を低減できる。さらに、凹部の深さの関数であるLc等を上記式を満たすよう設定することで、光リーク電流を効果的に低減できる。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタ等の半導体素子を介して上層と下層に形成された配線層間の良好な接続を可能にし、配線の自由度を向上させた半導体装置及びその作製方法を提供すること目的の一とする。

【解決手段】絶縁体でなる基板上の第1の絶縁層と、第1の絶縁層上に形成された第1の配線層と、第1の絶縁層上の第1の配線層が形成された領域以外の領域に形成された第2の絶縁層と、第1の配線層及び第2の絶縁層上に形成され、チャネル形成領域と不純物領域を有する単結晶半導体層と、単結晶半導体層のチャネル形成領域上にゲート絶縁層を介して形成されたゲート電極と、第1の配線層、第2の絶縁層、単結晶半導体層及びゲート電極を覆うように形成された第3の絶縁層と、第3の絶縁層上に形成された第2の配線層とを設け、第1の配線層と単結晶半導体層の不純物領域が接続し、第1の配線層と第2の配線層が電気的に接続する。

(もっと読む)

半導体装置の製造方法及び混成トランジスタ用半導体装置の製造方法

【課題】MOSトランジスタの寄生抵抗の低減化を図るとともに、ソース・ドレイン領域及びエクステンション部を構成するエピタキシャル成長領域の安定化を図った半導体装置の製造方法を得る。

【解決手段】ポリシリコンゲート5の側面にオフセット部をオフセットスペーサ用酸化膜31及びオフセットスペーサ用窒化膜32の2層構造で形成し、さらにその側面にサイドウォール用酸化膜33及びダミーサイドウォール用窒化膜を形成した後、当該ダミーサイドウォール用窒化膜を熱燐酸を用いて除去する。その結果、選択エピ成長領域12とポリシリコンゲート5との間に段差部19が形成される。そして、ポリシリコンゲート5、上記酸化膜及び窒化膜31〜33をマスクとして、ゲート外SOI領域3e、選択エピ成長領域11及び12にExt用不純物22及びHalo用不純物23を順次注入,拡散する。

(もっと読む)

半導体装置およびその作製方法

【課題】工程を増やすことなく、1枚のマザーガラス基板上に所望の部分にそれぞれ精密に配線の側面の角度を異ならせた配線を提供することを課題とする。

【解決手段】多階調マスクを用いることで1つのフォトレジスト層を1枚のマザーガラス基板から遠ざかる方向に向かって断面積が連続的に減少するテーパ形状を有するフォトレジスト層を形成する。1本の配線を形成する際、1枚のフォトマスクを用い、金属膜を選択的にエッチングすることで、場所によって側面形状(具体的には基板主平面に対する角度)が異なる1本の配線を得る。

(もっと読む)

半導体装置の作製方法

【課題】フリンジフィールドスイッチングモードで駆動する液晶表示装置の作製方法において、フォトマスク数を削減することで製造工程の簡略化及び製造コストの削減をする。

【解決手段】透光性を有する絶縁基板上に第1の透明導電膜及び第1の金属膜を順に成膜し積層し、第1のフォトマスクである多階調マスクを用いて第1の透明導電膜及び第1の金属膜を形状加工し、絶縁膜、第1の半導体膜、第2の半導体膜、第2の金属膜を順に成膜し積層し、第2のフォトマスクである多階調マスクを用いて第2の金属膜、第2の半導体膜を形状加工し、保護膜を成膜し、第3のフォトマスクを用いて保護膜を形状加工し、第2の透明導電膜を成膜し、第4のフォトマスクを用いて第2の透明導電膜を形状加工する。

(もっと読む)

薄膜トランジスタ及び半導体装置

【課題】より高い移動度及びオン電流を得ることができる微結晶半導体膜を用いた薄膜トランジスタ、及び薄膜トランジスタを用いた半導体装置を提供する。

【解決手段】微結晶半導体膜のうち、成膜を開始した当初に形成される結晶性の劣った層ではなく、その後に形成される結晶性の高い層においてチャネル形成領域が形成されるように、結晶性の高い層のうちゲート絶縁膜に近い層に、一導電型を付与する不純物元素を含ませる。そして、不純物元素を含む層をチャネル形成領域として用いる。また、ソース領域またはドレイン領域として機能する不純物元素を含む一対の半導体膜と、チャネル形成領域として機能する不純物元素を含む層との間に、一導電型を付与する不純物元素を含まない、もしくは他の層に比べて一導電型を付与する不純物元素の濃度が著しく低い層を設ける。

(もっと読む)

微結晶半導体膜、当該微結晶半導体膜を有する薄膜トランジスタ、及び光電変換装置の作製方法

【課題】異種材料基材上において、界面及び膜中の結晶性の高い微結晶半導体膜の形成方法を提案する。また、結晶性の高い微結晶半導体膜を有する薄膜トランジスタの作製方法を提案する。また、結晶性の高い微結晶半導体膜を有する光電変換装置の作製方法を提案する。

【解決手段】被膜上に、密度が高く、且つ結晶性の高い結晶核を形成した後、結晶核から半導体の結晶粒を結晶成長させて、被膜との界面における結晶性、隣接する結晶粒の密着性、及び結晶粒の結晶性、それぞれを高めた微結晶半導体膜を形成する。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の設計方法、電気光学装置、電子機器、電気光学装置の製造方法及び電子機器の製造方法

【課題】半導体装置の特性の向上、特に、遮光性の向上による光リーク電流の低減を図る。

【解決手段】本発明に係る半導体装置は、基材(10A,10B)と、基材上に形成され、第1方向に延在する半導体膜(13)と、半導体膜上にゲート絶縁膜(15)を介して形成され、第1方向と交差する第2方向に延在するゲート電極(G)と、半導体膜の両側に前記第1方向に延在するよう形成された一対の凹部(12)と、凹部内に配置された充填材料と、を有する。かかる構成によれば、凹部(12)およびその内部の充填材料により、基板側からの光の入射が制限され、半導体膜(特に、チャネル)において発生する光リーク電流を低減できる。

(もっと読む)

半導体装置及び電子機器

【課題】動作性能および信頼性の高い半導体装置を提供する。

【解決手段】第1の薄膜トランジスタと、第2の薄膜トランジスタとを有する画素部を有する。前記第1の薄膜トランジスタは、第1の半導体層と、前記第1の半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された第1のゲート電極とを有し、前記第2の薄膜トランジスタは、第2の半導体層と、前記第2の半導体層上に形成された前記ゲート絶縁膜と、前記ゲート絶縁膜上に形成された第2のゲート電極とを有する。前記第1のゲート電極及び前記第2のゲート電極は、それぞれ端部にテーパー部を有し、前記第1の半導体層は、第1のチャネル形成領域、一対の第1の不純物領域、及び一対の第2の不純物領域を有し、前記第2の半導体層は、第2のチャネル形成領域、及び一対の第3の不純物領域を有する。

(もっと読む)

薄膜トランジスタ、及びその製造方法、並びに表示装置

【課題】特性を良好に保ち、信頼性の高い薄膜トランジスタ及びその製造方法、並びにこの薄膜トランジスタを搭載した表示装置を提供すること。

【解決手段】本発明の一態様に係る薄膜トランジスタの製造方法は、ゲート電極2上にゲート絶縁膜3を形成する工程を備え、ゲート絶縁膜3は、水素化非晶質シリコン膜4と接する第1領域11と、当該第1領域11より下層に位置する第2領域12とを少なくとも備え、第1領域11及び第2領域12は、NH3,N2,SiH4からなる原料ガスと,H2又はH2とHeからなるガスとを用いて成膜され、第1領域11はNH3とSiH4の流量比(NH3/SiH4)を11以上、14以下とし、第2領域12はNH3とSiH4の流量比(NH3/SiH4)を4以下として成膜する。

(もっと読む)

半導体装置の作製方法、半導体装置及び電子機器

【課題】製造コストを低減しつつ、高速動作が可能な回路を有する半導体装置の作製方法を提供することを課題の一とする。または、該半導体装置を提供するための半導体基板の作製方法を提供することを課題の一とする。または、該半導体装置を用いた電子機器を提供することを課題の一とする。

【解決手段】基板上に非単結晶半導体層を形成した後、非単結晶半導体層の一部の領域上に単結晶半導体層を形成する。これにより、非単結晶半導体層を用いて大面積が必要とされる領域(例えば、表示装置における画素領域)の半導体素子を形成し、単結晶半導体層を用いて高速動作が求められる領域(例えば、表示装置における駆動回路領域)の半導体素子を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数の増加や前後のプロセスへの影響を抑えて、n型MOS−FET、p型MOS−FETのそれぞれに適する応力を付与することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板wと、半導体基板wに形成されたソース領域12aおよびドレイン領域13aと、半導体基板w上のソース領域12a、ドレイン領域13a間に形成されたゲート電極16と、半導体基板wおよびゲート電極16上に形成された層間膜18と、層間膜18に埋め込み形成され、引張または圧縮応力を有する金属または金属化合物を含む膜22a、22bを有し、半導体基板wおよびゲート電極16と離間するように形成されたダミーフローティングパターン22を備える。

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

(式中、X1〜X14はそれぞれ独立に、水素原子、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、あるいは置換または未置換のアリール基を表し、環Aは、置換または未置換のベンゼン環、置換または未置換のナフタレン環、置換または未置換のチオフェン環、置換または未置換のベンゾ[b]チオフェン環、あるいは置換または未置換のフェナントレン環を表す)

(もっと読む)

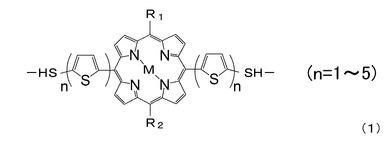

有機電子デバイス及びその製造方法、並びに、有機半導体分子

【課題】物性的に安定し、しかも、製造が比較的容易な有機電子デバイスを提供する。

【解決手段】有機電子デバイスは、(A)微粒子、及び、(B)微粒子と微粒子とを結合した有機半導体分子から成り、p型としての挙動を示す導電路を具備し、有機半導体分子は、下記の構造式(1)で表されることを特徴とする有機電子デバイス。

但し、構造式(1)中、R1,R2はアルキル基を表し、Mは、2H,Zn+2,Mg+2,Fe+2,Co+2,Ni+2,Cu+2を表し,nは1乃至5の整数である。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

半導体装置の作製方法及び成膜方法及び成膜装置

【課題】チャンバー外からチャンバー内へのリーク量が低減された成膜装置を提供することを課題とする。

【解決手段】チャンバー外からチャンバー内へのリークが生じたとしても、チャンバー外壁を囲む雰囲気に含まれる酸素及び窒素を極力低減し、希ガスまたは水素で充填することにより、大気における酸素濃度及び窒素濃度の100分の一以下、好ましくは1000分の一以下とし、チャンバー内をさらにクリーンに保つ。チャンバーの外側に気密性の高い空間を隣接して設けるため、チャンバーを袋体で覆い、高純度のアルゴンガスを袋体内に供給する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】横方向電界方式の液晶表示装置の基板上に形成される成膜構造を簡略化でき、安

価に製造することが可能な液晶表示装置及びその製造方法を提供すること。

【解決手段】本発明の液晶表示装置1は、液晶30を挟持した一対の透明基板11、25

を備え、一方の透明基板11の液晶30側には、間に第1絶縁膜13を介してマトリクス

状に配置された複数の走査線12及び信号線16と、走査線12及び信号線16の交差部

近傍に設けられたスイッチング素子と、スイッチング素子の表面を含む表示領域DA全体

を被覆する層間樹脂膜14と、層間樹脂膜14の表面に形成された第1電極17と、第1

電極17上に形成された第2絶縁膜18と、第2絶縁膜18上に形成され走査線12及び

信号線で区画された領域毎に複数のスリット20が形成された第2電極21と、を備え、

層間樹脂膜14はスイッチング素子のチャネル領域CR及び電極(S、D)を直接被覆し

ている。

(もっと読む)

半導体装置の製造方法

【課題】 オフ電流の突発的な増大が抑制されるTFTを備えた半導体装置を簡便に製造する。

【解決手段】本発明による半導体装置(100)の製造方法は、フォトレジスト層(P)を形成する工程と、導電層(G)に、第1領域(GH)と、第1領域(GH)よりも薄い第2領域(GL)を形成する工程と、フォトレジスト層(P)の一部を除去してフォトレジスト層(P)の残りの部分を除去しないようにフォトレジスト層(P)を部分的にエッチングする工程と、フォトレジスト層(P)の除去しなかった部分(PA’)をマスクとして用いてゲート電極(130)を形成する工程と、導電層(G)の第1領域(GH)および第2領域(GL)に対応して絶縁層(120)の第1領域(120H)および第2領域(120L)を形成する工程とを包含する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置の作製方法及び液晶表示装置の作製方法

【課題】酸化亜鉛を含む半導体膜を用い、ソース電極及びドレイン電極にn型又はp型の不純物を添加した酸化亜鉛を含む膜を用いたときでも欠陥や不良が生じない半導体装置及びその作製方法を提供する。

【解決手段】絶縁膜を形成し、絶縁膜上に第1の導電膜を形成し、第1の導電膜上にn型又はp型の不純物が添加された酸化亜鉛を含む第2の導電膜を形成し、第2の導電膜を第1のエッチングによって島状にし、第1の導電膜を第2のエッチングによって島状にし、絶縁膜及び島状の第2の導電膜上に酸化亜鉛を含む半導体膜を形成する。

(もっと読む)

2,001 - 2,020 / 3,665

[ Back to top ]