Fターム[5F110EE29]の内容

Fターム[5F110EE29]に分類される特許

1 - 20 / 152

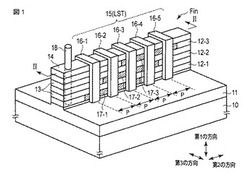

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トラ

ンジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体

に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ

<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン

電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができ

る。

(もっと読む)

検波器及び受信機

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な検波器を提供する。

【解決手段】検波器は、信号入力端子に接続された第1導電型の第1の半導体領域と、信号出力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、交流的に接地された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、一端が第2の半導体領域に接続され、他端が交流的に接地された第1の抵抗素子と、を含む。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

光検出回路、入力装置、及び入出力装置

【課題】光検出回路から出力される光データへの寄生容量の影響を抑制する。

【解決手段】光電変換素子と、第1の電界効果トランジスタと、第2の電界効果トランジスタと、を備え、第1の電界効果トランジスタのゲートとしての機能を有する第1の導電層と、第1の導電層の上に設けられた絶縁層と、絶縁層を介して第1の導電層に重畳し、第1の電界効果トランジスタのチャネル形成層としての機能を有する半導体層と、半導体層に電気的に接続され、第1の電界効果トランジスタのソース及びドレインの一方としての機能を有する第2の導電層と、半導体層に電気的に接続され、対向する一対の側面が絶縁層を介して第1の導電層を含む1つ以上の導電層に重畳し、第1の電界効果トランジスタのソース及びドレインの他方としての機能を有する第3の導電層と、を含む。

(もっと読む)

半導体装置

【課題】長期に亘って信頼性の高い横型MISFETを有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板11上に形成された半導体層13と、半導体層13に溝状に形成され、その内壁が絶縁膜31で被覆され、絶縁膜31の内部にゲート電極32が埋設されたトレンチ溝30と、半導体層13上に、トレンチ溝30と少なくとも一部が対向配置する位置に形成されたゲート配線51と、ゲート配線51を挟むように半導体層13上に形成されたソース電極52、及びドレイン電極53とを具備する。半導体層13におけるオン動作時の電流経路は、ソース電極52とドレイン電極53の間の半導体層13の表面領域を実質的に経由せず、上記トレンチ溝30の側面近傍を経由する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】薄膜トランジスタは、第1方向に形成された少なくとも1本のゲートラインを含むゲート11と、ゲート上に形成されたゲート絶縁層12と、ゲート絶縁層12上に形成された少なくとも1つのソース13及びドレイン14と、を含み、ソース13及びドレイン14のうち少なくともいずれか一つは、延長部分13b、14bを含み、延長部分13b、14bは、少なくとも1本のゲートラインと平行するように、第1方向に形成される。ゲート11は、ライン状に均一厚を有し、その側面と上面との間に曲面を含み、1本または2本以上のゲートラインを含む形態となる。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのスイッチング速度を高速化した半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁層の一部上に形成された半導体層10と、半導体層10の側面10aに形成され、第1のゲート絶縁膜21、第1のゲート電極22、並びにソース及びドレインとなる2つの第1の不純物層23,24を有する第1のトランジスタ20と、半導体層10の側面10bに形成され、第2のゲート絶縁膜31、第2のゲート電極32、並びにソース及びドレインとなる2つの第2の不純物層33,34を有する第2のトランジスタ30とを具備する。

(もっと読む)

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】良好な電気特性を有する半導体装置を提供する。

【解決手段】基板上に形成される第1の電極と、第1の電極に接して形成される一対の酸化物半導体膜と、一対の酸化物半導体膜に接する第2の電極と、少なくとも第1の電極および一対の酸化物半導体膜を覆うゲート絶縁膜と、ゲート絶縁膜に接して、少なくとも一対の酸化物半導体膜の間に形成される第3の電極とを有する半導体装置であり、酸化物半導体膜のドナー密度が1.0×1013/cm3以下である場合、酸化物半導体膜の膜厚は、酸化物半導体膜の膜厚横方向の長さに対して厚くすることである。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、スイッチング特性が良好で、順逆両方向で高耐圧が得られる半導体装置を提供する。

【解決手段】第1導電型のエミッタ層と、エミッタ層上に設けられエミッタ層よりも不純物濃度が低い第1導電型半導体層と、第1導電型半導体層上に設けられた第2導電型半導体層と、第2導電型半導体層に接して設けられた第1の主電極と、エミッタ層に接して設けられた第2の主電極と、第2導電型半導体層の表面から第1導電型半導体層に達して形成された複数のトレンチ内にゲート絶縁膜を介して設けられたゲート電極とを備え、第1の主電極とゲート電極とが短絡された状態で、第1の主電極と第2の主電極との間に逆方向電圧が印加されると、隣り合うゲート電極間の第1導電型半導体層内で空乏層がピンチオフするようにゲート電極間の間隔が設定されている。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタ

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】n型バリア層15を形成することでエミッタ側のキャリア濃度を高くしてオン電圧の低減を図りつつ、n型バリア層15を隣り合うエミッタ間に形成しないようにすることで、ターンオフ時間の改善を図る。また、このような構造により、スイッチング時の破壊耐量の向上も図ることも可能となる。したがって、オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTとすることが可能となる。

(もっと読む)

半導体装置

【課題】生産性の高い半導体材料を用い、且つ耐圧性を向上させたトランジスタを提供することを課題の一とする。または、高耐圧のトランジスタを用いた大電力向けの半導体装置を提供することを課題の一とする。

【解決手段】トランジスタにおいて、高電界の印加されるドレイン電極を平坦な面上に形成し、且つ、ゲート電極の、チャネル幅方向のドレイン電極側の端部、およびチャネル長方向の端部を、ゲート絶縁層を介して酸化物半導体層で覆うことによって、トランジスタの耐圧を向上させる。また、該トランジスタを用いた大電力向けの半導体装置を提供することができる。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

半導体装置

【課題】ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を提供する。

【解決手段】ドリフト領域2と、ベース領域3と、ベース領域3を挟んでドリフト領域2に対向して設けられたソース電極12と、ドリフト領域2とベース領域3とにゲート絶縁膜を介して接するトレンチ構造の複数のゲート電極6と、2つのゲート電極6の間において、ドリフト領域2とベース領域3との境界に沿って設けられ、ベース領域3に接する長さがゲート電極6よりも短いトレンチ構造のゲート電極7と、を備え、ソース電極12は2つのゲート電極6の間において、ソース電極12からゲート電極7に向かう方向に設けられたトレンチ9bの中に、ゲート電極7に近接した位置まで延在し、ゲート電極6のソース電極側の端とゲート電極7のソース電極側の端との間において、トレンチ9bの内壁面に露出したベース領域3に接していること。

(もっと読む)

1 - 20 / 152

[ Back to top ]