Fターム[5F110EE30]の内容

Fターム[5F110EE30]に分類される特許

161 - 180 / 944

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置、半導体装置の製造方法、電気装置

【課題】半導体装置、半導体装置の製造方法、電気装置を提供する。

【解決手段】本発明の半導体装置は、一面に、ソース電極41cおよびドレイン電極41dを有する第1基板34と、一面に、ゲート電極41e、ゲート絶縁膜41bおよび半導体層41aを有する第2基板39と、第1基板34および第2基板39が互いの一面側を対向させて貼り合わされることによりこれら第1基板34と第2基板39との間に構成される薄膜トランジスタTRと、を備えている。

(もっと読む)

薄膜トランジスタ形成用基板、半導体装置、電気装置

【課題】多層基板内にTFT素子の構成要素のうちの少なくとも1つを内蔵させることによって薄膜トランジスタの高精細化を実現できる薄膜トランジスタ形成用基板、半導体装置、電気装置を提供する。

【解決手段】本発明の第1基板30(素子基板300)は、表面に制御トランジスタの構成要素の少なくとも一部を備え、内部には制御トランジスタの構成要素に接続される走査線66、データ線68、保持容量線、保持容量が埋め込まれていることを特徴とする。

(もっと読む)

表示装置の駆動方法

【課題】酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表示装置の駆動方法を提供する

【解決手段】複数のフレーム期間により画像表示を行う表示装置の駆動方法において、各フレーム期間における複数の走査線のうち、いずれか一の走査線を選択する期間で駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるよう駆動する。そして複数のフレーム期間にわたって、各行を選択していくことで全ての駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるようにしてトランジスタの特性劣化を回復するものである。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

結晶性半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性半導体の核生成を均一にする。

【解決手段】ガス管から導入された成膜ガスを拡散する第2のガス拡散室と、前記第2のガス拡散室と分散板を隔てて設けられ、該分散板のガス孔から成膜ガスが導入される第1のガス拡散室と、を介して、前記第1のガス拡散室とシャワー板を隔てて設けられた処理室内に該シャワー板のガス孔から成膜ガスを供給し、前記成膜ガスを導入することによって前記処理室内の圧力を2000Pa以上100000Pa以下とし、前記処理室内に電界を生じさせる一対の電極のうち、一方の電極面から電界強度が均一な高周波電力を供給することでグロー放電プラズマを生成させ、前記対向する電極の他方に配された基板上に結晶核を生じさせ、その後、該結晶核を成長させて結晶性半導体膜を作製する。

(もっと読む)

硬化性組成物

【課題】高誘電率かつ絶縁性に優れた薄膜を与え得る硬化性組成物に関するものであり、さらに当該組成物を用いて形成した薄膜をゲート絶縁膜として適用し、良好な特性を示す薄膜トランジスタを提供することである。

【解決手段】A)ポリシロキサン系樹脂、B)有機金属化合物、C)有機溶剤を必須成分として含有し、有機金属化合物の含有率がポリシロキサン系樹脂に対して10〜80重量%である硬化性組成物により達成でき、該組成物からなる膜をゲート絶縁膜として用いた薄膜トランジスタは良好な特性を有する。

(もっと読む)

半導体装置及びトランジスタの駆動方法

【課題】光照射されてトランジスタの電気特性が変動した場合でも、その電気特性をほぼ光照射前の状態にする手法を提供する。

【解決手段】酸化物半導体を用いたトランジスタのゲート電極に、正のバイアス電圧を10msec以上印加することにより、光照射されて変動した当該トランジスタの電気特性をほぼ光照射前の状態にすることが可能になる。なお、当該トランジスタのゲート電極に対する正のバイアス電圧印加は、当該トランジスタが受光する光量を参照して適切なタイミングで行う。これより光照射されても表示品位の低下が抑制された表示装置を実現することができる。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

半導体装置

【課題】表示装置に用いられるトランジスタは、より高耐圧なものが求められており、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図る。

【解決手段】チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられたトランジスタを有する半導体装置である。バッファ層は、チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にあって、特にドレイン端近傍の電界を緩和して、トランジスタの耐圧を向上させるように設けられる。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】電気的特性が良好な半導体装置の作製方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、HBrガスと、CF4ガスと、酸素ガスの混合ガスを含むガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを薄膜トランジスタのバックチャネル部を形成するエッチングに適用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバICの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジスタを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給する。

(もっと読む)

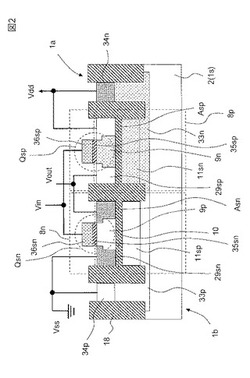

半導体装置、および半導体装置の製造方法

【課題】同一の極性を有する複数の薄膜FETの閾値電圧に差をつけて、半導体装置の性能の最適化を図ることができる。

【解決手段】半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に形成された薄膜n型FET100と、埋め込み絶縁膜2上に形成された薄膜p型FET101と、埋め込み絶縁膜2上に形成された薄膜n型FET100bと、薄膜n型FET100のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4と、薄膜p型FET101のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域5と、薄膜n型FET100bのチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4bと、を備え、p型ウェル領域4、4b、5は、n型ウェル領域40によって囲まれており、かつ互いに接触していない。

(もっと読む)

半導体装置

【課題】画素部の周辺領域にTFTを用いて駆動回路を基板上に同時形成するポリシリコンTFTによって回路を構成する際、TFTのしきい値によって出力振幅が減衰しない、表示装置の駆動回路を提供する。

【解決手段】信号出力端子に電気的に接続されるTFTのゲート電極に、容量手段に保持されている電圧を加えた電位が与えられることにより、当該TFTにおける振幅減衰が生ずることなく、信号出力端子からは正常な振幅の出力を得ることができる。

(もっと読む)

トランジスタの作製方法

【課題】特性のバラツキが少なく、電気特性が良好なトランジスタを作製する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体を含む半導体層を形成し、半導体層上に不純物半導体層を形成し、不純物半導体層上にマスクを形成した後、マスクを用いて半導体層及び不純物半導体層をエッチングして、半導体積層体を形成し、マスクを除去した後に半導体積層体を希ガスを含む雰囲気で発生させたプラズマに曝して半導体積層体の側面に障壁領域を形成し、半導体積層体の不純物半導体層に接する配線を形成する。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワーMISFETを提供する。

【解決手段】半導体層101を挟んでゲート電極102aとソース電極103a、ドレイン電極103bを形成し、半導体層のうちゲート電極102aとドレイン電極103bとの間にこれらが重ならない領域を設ける。この領域の長さを0.5μm乃至5μmとする。このようなパワーMISFETのドレイン電極とソース電極の間に100V以上の電源と負荷を直列に接続し、ゲート電極102aに制御用の信号を入力して使用する。

(もっと読む)

薄膜トランジスタ

【課題】上記事情から、本発明の目的は、低温条件下で簡便な溶液塗布プロセスにより形成可能であり、かつ、良好なトランジスタ特性を発現する薄膜トランジスタを提供することである。

【解決手段】 ヒドロシリル化反応を架橋反応とする樹脂組成物を溶液塗布し形成されるゲート絶縁膜を有する有機薄膜トランジスタ素子。

(もっと読む)

161 - 180 / 944

[ Back to top ]