Fターム[5F110EE30]の内容

Fターム[5F110EE30]に分類される特許

121 - 140 / 944

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極及び空孔付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に選択的に一対の第1の半導体層6が設けられ、第1の半導体層6にそれぞれ1側面を接し、空孔5上に一対の第2の半導体層8が設けられ、第2の半導体層8間に2側面を接し、残りの周囲にゲート絶縁膜14を介してゲート電極15に包囲された、歪み構造の第3の半導体層7が設けられ、第1及び第2の半導体層(6、8)には概略ソースドレイン領域(10、11、12、13)が設けられ、第3の半導体層7には概略チャネル領域が設けられ、ソースドレイン領域(10、13)及び包囲型ゲート電極15には配線体(19、20、22、23)が接続されているMISFET。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタはその動作原理から、低消費電力化を図るためには、動作時のバルク領域は完全空乏化される必要があった。結果として、プロセスばらつきがバルク領域のばらつきを生み、消費電力にばらつきを与えるという問題が生じていた。

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

SOI基板を用いた半導体装置と性能向上方法

【課題】素子の微細化とともに、DIBL(Drain Induced Barrier Lowering)などにより、トランジスタのON/OFF性能が劣化する。

【解決手段】半導体基板上に絶縁膜を積層し、その上にSi層を積層した構造上に形成した半導体装置において、前記Si層が10nm以下のであり、ゲート長が20nm以下であって、前記半導体基板から負電界のバックゲート電界が印加されていることを特徴とする半導体装置。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

膜形成用組成物および該組成物を用いた薄膜トランジスタ

【課題】 本発明の目的は、有機半導体素子の製造プロセス適応性に優れる膜形成用組成物および該組成物を用いた薄膜トランジスタを提供することである。

【解決手段】上記課題は、必須成分として、(a)式(I)で表される構造を0.6mmol/g以上含有する有機化合物と、(b)有機溶剤とを含有する膜形成用組成物および該組成物を有機半導体素子の絶縁膜等に用いる薄膜トランジスタにより達成される。該薄膜トランジスタは、閾値電圧が高く、ON/OFF電流比も高い特性の良好なトランジスタとなる。

【化1】 (もっと読む)

(もっと読む)

真性半導体層を備えたウェーハ

【課題】ウェーハを製造するための新規な方法を提供する。

【解決手段】本発明は、ウェーハを製造するための方法に関し、この方法は、半導体基板上にドープト層を設けるステップと、ドープト層上に第1の半導体層を設けるステップと、第1の半導体層上に埋込み酸化物層を設けるステップと、埋込み酸化物層上に第2の半導体層を設けるステップと、を備える。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流が小さく、好ましくはオン電流及び移動度も高く、工程が簡略化された半導体装置の作製方法を提供する。

【解決手段】チャネルエッチ型の薄膜トランジスタの作製に際して、ゲート絶縁層上に少なくとも半導体層を形成し、半導体層上に導電膜を形成し、導電膜上にエッチングマスクを形成し、基板を反応室内に搬入し、導電膜を加工してソース電極及びドレイン電極層を形成し、反応室内に半導体エッチング用のガスを導入し、反応室内で半導体エッチング用のガスでエッチングを行い、基板を反応室から搬出し、その後エッチングマスクを除去する。すなわち、導電膜の加工から半導体エッチング用のガスで行うエッチングまでを同一チャンバー内で連続して行い、半導体エッチング用のガスで行うエッチングはエッチングマスクを除去する前に行う。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

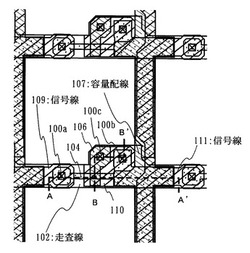

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置

【課題】消費電力を極力抑制することで電源の安定化を実現する半導体装置を提供する。

【解決手段】ロジック部11、メモリ部12、ロジック部とメモリ部の一方又は両方の動作頻度を検出する検出部13、検出部の検出結果に基づきロジック部及びメモリ部の一方又は両方にしきい値制御信号を供給するしきい値制御部14を有する半導体装置である。ロジック部とメモリ部の各々は複数のトランジスタを有しており、複数のトランジスタの各々は、論理信号が入力される第1のゲート電極と、しきい値制御信号が入力される第2のゲート電極と、半導体膜とを有する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

121 - 140 / 944

[ Back to top ]