Fターム[5F110EE30]の内容

Fターム[5F110EE30]に分類される特許

81 - 100 / 944

半導体装置

【課題】パワーデバイスである大電力用途向けの電界効果トランジスタにおいて、特性の良好な電界効果トランジスタを提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆うゲート絶縁層と、第1のゲート電極と重畳して、且つゲート絶縁層と接する酸化物半導体層と、酸化物半導体層の端部を覆うキャリア密度の高い酸化物半導体層と、キャリア密度の高い酸化物半導体層と接するソース電極及びドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層を覆う絶縁層と、絶縁層と接し、且つ、ソース電極及びドレイン電極の間に設けられる第2のゲート電極と、を有し、キャリア密度の高い酸化物半導体層は、酸化物半導体層を介して対向し、且つ酸化物半導体層の端部の上面、下面、及び側面のそれぞれ一部、並びにゲート絶縁層の上面一部と接する半導体装置である。

(もっと読む)

半導体装置

【課題】容易に共振周波数の設定を行う。

【解決手段】コイルとしての機能を有するアンテナと、アンテナと並列接続で電気的に接続される容量素子と、アンテナ及び容量素子と並列接続で電気的に接続されることにより、アンテナ及び容量素子と共振回路を構成する受動素子と、受動素子とアンテナ及び容量素子を並列接続で電気的に接続するか否かを制御する第1の電界効果トランジスタと、記憶回路と、を備え、記憶回路は、チャネルが形成される酸化物半導体層を含み、ソース及びドレインの一方にデータ信号が入力され、ソース及びドレインの他方の電圧に応じて第1の電界効果トランジスタのゲートの電圧が設定される第2の電界効果トランジスタを備える。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】少なくとも微結晶半導体領域及び非晶質半導体領域が積層する半導体膜を有する逆スタガ型の薄膜トランジスタにおいて、半導体膜上に導電膜及びエッチング保護膜を積層形成し、エッチング保護膜上にマスクを形成し、エッチング保護膜、導電膜及び非晶質半導体領域の一部をエッチングする第1のエッチング処理の後、マスクを除去する。次に、上記エッチングされたエッチング保護膜をマスクとして、露出した非晶質半導体領域及び微結晶半導体領域の一部をドライエッチングする第2のエッチング処理により、微結晶半導体領域の一部を露出させ、バックチャネル領域を形成する。

(もっと読む)

半導体装置及びその駆動方法

【課題】信号処理回路に対する電源電圧の供給及び遮断を選択することができるスイッチとして機能する回路(電源供給制御回路)として好ましい回路を提供する。

【解決手段】信号処理回路に対する電源電位の供給を担う第1の配線と、電源電位を供給する第2の配線との電気的な接続を制御するトランジスタ、及び、信号処理回路に対する電源電位の供給を担う第1の配線を接地させるか否かを制御するトランジスタとを設け、当該2つのトランジスタの少なくとも一方として、チャネルが酸化物半導体層に形成されるトランジスタを適用する。これにより、2つのトランジスタの少なくとも一のカットオフ電流に起因する消費電力を低減することが可能となる。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】大電力の制御を行う、高耐圧の半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上の、ゲート電極と重畳する酸化物半導体層と、酸化物半導体層と接し、端部をゲート電極と重畳するソース電極及びドレイン電極と、を有し、ゲート電極と酸化物半導体層が重畳する領域において、ゲート絶縁層は、ドレイン電極と端部を重畳する第1の領域と、前記第1の領域と隣接する第2の領域と、を有し、第1の領域の静電容量は第2の領域の静電容量より小さいトランジスタを提供すること。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

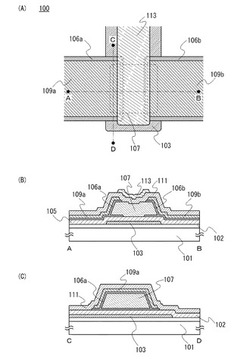

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】ワイドギャップ半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

酸化物薄膜トランジスタ及びその製造方法

【課題】短チャネルを実現し、薄膜トランジスタの性能を向上させる酸化物薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明による酸化物薄膜トランジスタの製造方法は、基板110上に第1導電膜からなるゲート電極121及びゲートライン116を形成する段階と、ゲート電極121及びゲートライン116が形成された基板110上にゲート絶縁膜115aを形成する段階と、ハーフトーン露光を用いて、ゲート絶縁膜115aが形成されたゲート電極121の上部に第2導電膜からなるソース電極122、第1ドレイン電極123、及び第1データライン117を形成し、かつ第1ドレイン電極123の延長部及び第1データライン117上に第3導電膜からなる第2ドレイン電極123’及び第2データライン117’を形成する段階と、ソース電極122及び第1ドレイン電極123上に酸化物半導体からなるアクティブ層124を形成する段階とを含む。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】非接触にて、被写体の位置情報の取得を容易に行うことができる固体撮像装置、または半導体表示装置の提供。

【解決手段】第1入射方向から第1入射角を有する光が入射する複数の第1フォトセンサと、第1入射方向とは異なる第2入射方向から第2入射角を有する光が入射する複数の第2フォトセンサとを有し、複数の第1フォトセンサのうち、第1入射方向の上流側の一つの第1フォトセンサの方が、第1入射方向の下流側の他の一つの第1フォトセンサよりも、第1入射角が大きく、複数の第2フォトセンサのうち、第2入射方向の上流側の一つの第2フォトセンサの方が、第2入射方向の下流側の他の一つの第2フォトセンサよりも、第2入射角が大きい。

(もっと読む)

半導体装置

【課題】動作速度の低下を抑制しつつ、消費電力を低減する。

【解決手段】第1の半導体領域の上に絶縁領域を有し、且つ絶縁領域の上に第2の半導体領域を有する基板に設けられた第1の電界効果トランジスタと、基板の上に設けられた絶縁層と、絶縁層の一平面に設けられ、酸化物半導体層を含む第2の電界効果トランジスタと、第2の電界効果トランジスタのソース及びドレインと同一工程により形成され、第1の電界効果トランジスタの閾値電圧を制御するための電圧が供給される制御端子と、を備える。

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶データとしてデータを記憶するメモリセルと、出力信号線と、電圧が与えられる配線と、を具備し、メモリセルは、記憶データと検索データの比較演算を行い、演算結果に応じて導通状態又は非導通状態になる比較回路と、記憶データの書き込み及び保持を制御する電界効果トランジスタと、を備え、比較回路が導通状態のときに、出力信号線の電圧値が配線の電圧と同等の値になる記憶装置。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

入出力装置

【課題】光電変換素子に対するトランジスタの数を低減する。

【解決手段】表示データ信号のデータに応じた表示状態になる表示回路と、それぞれ入射する光の照度に応じた光データを生成する複数の光検出回路と、を含み、光検出回路は、X個(Xは2以上の自然数)の光電変換素子131と、ソース及びドレインの一方がX個の光電変換素子のうちの一つの光電変換素子の第2の電流端子に電気的に接続され、ゲートに光検出回路制御部からX個の電荷蓄積制御信号うち一つの電荷蓄積制御信号が入力されるX個の電荷蓄積制御トランジスタTXと、ゲートがX個の電荷蓄積制御トランジスタのソース及びドレインの一方のそれぞれに電気的に接続される増幅トランジスタ132と、を備える。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

部材の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生

産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向か

って結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化

物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部

材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の

同軸(アキシャル)成長をさせていることである。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを

目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かっ

て成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2

の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層

と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と

、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、

第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置であ

る。

(もっと読む)

81 - 100 / 944

[ Back to top ]