Fターム[5F110EE30]の内容

Fターム[5F110EE30]に分類される特許

21 - 40 / 944

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

表示装置

【課題】チャネルが非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回

路に用いる際、しきい値電圧の変動の程度に応じてしきい値電圧を補正する駆動回路を提

供することを課題の一とする。

【解決手段】半導体層の上下に絶縁層を介して配置された第1のゲート及び第2のゲート

を有する単極性のトランジスタで構成される駆動回路において、第1のゲートには、トラ

ンジスタのスイッチングを制御するための第1の信号が入力され、第2のゲートには、ト

ランジスタのしきい値電圧を制御するための第2の信号が入力され、第2の信号は、トラ

ンジスタのソースとドレインとの間を流れる電流を含む、駆動回路の消費電流の値に応じ

て制御されるものとする。

(もっと読む)

半導体装置、発光装置、及び電子機器

【課題】動作不良を抑制する。

【解決手段】電界効果トランジスタと、スイッチと、容量素子と、を設ける。電界効果トランジスタは、チャネル形成領域を介して互いに重畳する第1のゲート及び第2のゲートを有し、第2のゲートの電位に応じて閾値電圧の値が変化する。スイッチは、電界効果トランジスタのソース及びドレインの一方と、電界効果トランジスタにおける第2のゲートと、を導通状態にするか否かを制御する機能を有する。容量素子は、電界効果トランジスタにおける第2のゲートと電界効果トランジスタにおけるソース及びドレインの他方との間の電圧を保持する機能を有する。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置において、電気特性の安定した半導体装置を提供する。とくに、酸化物半導体を用いた半導体装置において、より優れたゲート絶縁膜を有する半導体装置を提供する。また、当該半導体装置の作製方法を提供する。

【解決手段】ゲート電極と、ゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜と接して形成されたソース電極、及びドレイン電極と、を有し、ゲート絶縁膜は、少なくとも酸化窒化シリコン膜と、酸化窒化シリコン膜上に形成された酸素放出型の酸化膜と、により構成され、酸素放出型の酸化膜上に酸化物半導体膜が接して形成される。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体素子

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半

導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを

課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレ

イン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート

絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は

側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

表示装置

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置

【課題】電流駆動能力がより小さなクロック信号生成回路を適用することが可能な半導体装置を提供する。

【解決手段】nチャネル型トランジスタで構成されるスイッチ及び論理回路を有し、スイッチは導通状態又は非導通状態がクロック信号によって選択され、論理回路は、ブートストラップ回路と、入力信号が入力される入力端子と、反転入力端子と、出力端子とを有し、高電源線と出力端子との接続を反転入力端子に入力される信号によって制御し、低電源線と出力端子との接続を入力端子に入力される信号によって制御することによって、入力信号がローレベル電位の場合には、ブートストラップ回路を用いて出力端子の電位を上昇させることにより出力端子から高電源電位を出力し、トランジスタは、チャネルが形成される半導体層と、半導体層を挟んで上下に設けられた一対のゲート電極とを有し、一対のゲート電極の他方はソースと接続される。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素

子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査

線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソー

スまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第

2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソース

またはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジ

スタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、

前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供

給される信号の出力が停止される期間を有する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力の低減が可能な半導体装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを備える半導体装置において、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜において、酸素濃度が異なる。代表的には、ゲート電圧が負のときの電流が小さいトランジスタの酸化物半導体膜と比較して、電界効果移動度が高くオン電流が大きいトランジスタの酸化物半導体膜の酸素濃度が低い。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

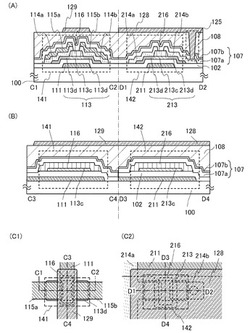

半導体装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複

数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを

課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる

酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャ

ネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成する

ことにより、開口率を上げる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

半導体装置の作製方法

【課題】薄膜トランジスタのしきい値電圧を制御するため、薄膜トランジスタのチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設けた際に、プロセス数の増加を招くことなく、電気特性の優れた薄膜トランジスタを備えた半導体装置を得る。

【解決手段】酸化物半導体層131の上方に設ける第2のゲート電極133を形成するとき、酸化物半導体層131のパターニングと同時に形成することで、第2のゲート電極133の作製に要するプロセス数の増加を削減する。

(もっと読む)

21 - 40 / 944

[ Back to top ]