Fターム[5F110FF30]の内容

Fターム[5F110FF30]の下位に属するFターム

ECRプラズマCVD (84)

Fターム[5F110FF30]に分類される特許

141 - 160 / 2,978

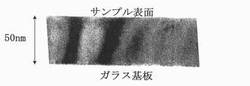

酸化物半導体薄膜層を有する積層構造、積層構造の製造方法、薄膜トランジスタ及び表示装置

【課題】酸化物薄膜の結晶配置の方向を制御し、良質な酸化物薄膜を提供する。

【解決手段】薄膜トランジスタのチャネル層となる酸化物層と絶縁層からなる積層構造であって、前記酸化物層を構成する材料は、実質的に酸化インジウムのビックスバイト構造からなり、前記酸化物層のキャリア濃度が1018/cm3以下、平均結晶粒径が1μm以上であり、前記酸化物層の結晶が、前記絶縁層の表面に柱状に配置していることを特徴とする積層構造。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トラ

ンジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体

に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ

<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン

電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができ

る。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

液晶表示装置

【課題】非晶質半導体膜の結晶化工程において、非晶質半導体膜上に金属元素を導入して加熱処理を行なった、レーザアニールを行って得られた多結晶半導体膜を基に作製された薄膜トランジスタの電気的特性は非常に高いものとなるが、ばらつきが顕著になる場合がある。

【解決手段】非晶質半導体膜上に金属元素を導入して加熱処理を行なって連続的な結晶化領域の中に非晶質領域が点在する第1の多結晶半導体膜103bを得る。このとき、非晶質領域を所定の範囲に収めておく。そして、結晶化領域より非晶質領域にエネルギーを加えることができる波長域にあるレーザビームを第1の多結晶半導体膜103bに照射すると、結晶化領域を崩すことなく非晶質領域を結晶化させることができる。以上の結晶化工程を経て得られた第2の多結晶半導体膜を基にTFTを作製すると、その電気的特性は高く、しかもばらつきの少ないものが得られる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を不活性ガス雰囲気化で加熱し、その後、酸化物半導体膜を酸素雰囲気化で加熱する。本工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化することができる。不純物を排除する際、酸化物半導体を構成する主成分材料である酸素が欠損する場合があるが、酸素雰囲気化で加熱することによって、酸素を供給することができる。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

積層体とその製造方法及びそれを用いたデバイス構造体の製造方法

【課題】各種デバイスを積層するための基材とするためのポリイミドフィルムと支持体との積層体であって、デバイス作製時の高温プロセスにおいても剥がれることなく、しかもポリイミドフィルム上にデバイスを作製した後には容易に支持体からポリイミドフィルムを剥離することができる積層体を提供する。

【解決手段】ポリイミドフィルム6として、少なくとも支持体1に対向させる面にプラズマ処理が施されたフィルムを用い、支持体1とポリイミドフィルム6とが対向する面の少なくとも一方にカップリング剤を用いて、接着剥離強度は異なり表面粗さは略同一である良好接着部分と易剥離部分とを形成するパターン化処理を施した後、重ね合わせて加圧加熱処理することとし、ポリイミドフィルム6は、70モル%以上がベンゾオキサゾール構造を有する芳香族ジアミン類を主成分とするジアミン類とテトラカルボン酸類との反応によって得られる。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信

頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】絶縁表面上において、ゲート絶縁膜を間に挟んでゲート電極上に酸化物半導

体膜を形成し、酸化物半導体膜上に、チタン、モリブデンまたはタングステンを含む第1

の導電膜を形成し、第1の導電膜上に、電気陰性度が水素より低い金属を含む第2の導電

膜を形成し、第1の導電膜及び第2の導電膜をエッチングすることでソース電極及びドレ

イン電極を形成し、酸化物半導体膜、ソース電極及びドレイン電極上に、酸化物半導体膜

と接する絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸化物半導体を用いた薄膜トランジスタにおいては、酸素原子等を酸化物半導体中に十分かつ均一に拡散させることが困難である。

【解決手段】半導体装置であって、ゲート電極と、前記ゲート電極の一方の表面を覆うように配置されたゲート絶縁膜と、前記ゲート絶縁膜に重ねて配置された酸化物半導体と、前記酸化物半導体に重ねて配置されたソース電極及びドレイン電極と、前記ソース電極及びドレイン電極と、前記ゲート絶縁膜層との間に、前記酸化物半導体に接するように配置された酸素原子含有膜と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に酸化物半導体を用いたオフセットトランジスタとオフセットでないトランジスタを形成する。

【解決手段】酸化物半導体層202とゲート絶縁物203とゲート配線となる第1層配線204a、第1層配線204bを形成する。その後、オフセットトランジスタをレジスト206で覆い、酸化物半導体層に不純物を導入し、N型酸化物半導体領域207を形成する。その後、第2層配線209a、第2層配線209b、第2層配線209cを形成する。以上の工程により、オフセットトランジスタとそうでないトランジスタ(アラインドトランジスタ等)を形成することができる。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

イメージセンサ及び電子機器

【課題】後の工程で形成される光電変換層を広く形成することができ、センサの受光面積(開口率)を上げることができる、インテリジェント化された新規な半導体装置を用いた表示装置を提供する。

【解決手段】イメージセンサは、チャネル領域、ソース領域及びドレイン領域を有するトランジスタを有し、トランジスタの上方に絶縁膜を有し、絶縁膜の上方にフォトダイオードを有する。トランジスタはフォトダイオードと重なる位置に設けられている。

(もっと読む)

141 - 160 / 2,978

[ Back to top ]