Fターム[5F110FF30]の内容

Fターム[5F110FF30]の下位に属するFターム

ECRプラズマCVD (84)

Fターム[5F110FF30]に分類される特許

201 - 220 / 2,978

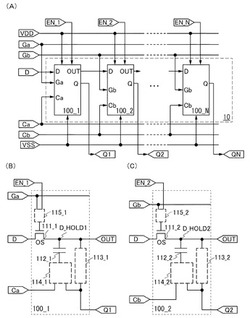

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

表示装置

【課題】酸化物半導体を用いたトランジスタを有する表示装置において、寄生容量を軽減する。表示装置において、解像度の向上や、高精細化といった高性能化及び高品質化を達成する。

【解決手段】ボトムゲート型のトランジスタにおいて、酸化物半導体膜と重畳して設けられるゲート電極が第1のゲート電極と第2のゲート電極とに間隔を有して分割して設けられる。第1のゲート電極はソース電極又はドレイン電極の一方と重畳して設けられ、第2のゲート電極はソース電極又はドレイン電極の他方と重畳して設けられる。

(もっと読む)

半導体装置

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチ

ングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングト

ランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチング

トランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気

的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半

導体装置である。

(もっと読む)

半導体装置

【課題】容易に共振周波数の設定を行う。

【解決手段】コイルとしての機能を有するアンテナと、アンテナと並列接続で電気的に接続される容量素子と、アンテナ及び容量素子と並列接続で電気的に接続されることにより、アンテナ及び容量素子と共振回路を構成する受動素子と、受動素子とアンテナ及び容量素子を並列接続で電気的に接続するか否かを制御する第1の電界効果トランジスタと、記憶回路と、を備え、記憶回路は、チャネルが形成される酸化物半導体層を含み、ソース及びドレインの一方にデータ信号が入力され、ソース及びドレインの他方の電圧に応じて第1の電界効果トランジスタのゲートの電圧が設定される第2の電界効果トランジスタを備える。

(もっと読む)

半導体装置

【課題】パワーデバイスである大電力用途向けの電界効果トランジスタにおいて、特性の良好な電界効果トランジスタを提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆うゲート絶縁層と、第1のゲート電極と重畳して、且つゲート絶縁層と接する酸化物半導体層と、酸化物半導体層の端部を覆うキャリア密度の高い酸化物半導体層と、キャリア密度の高い酸化物半導体層と接するソース電極及びドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層を覆う絶縁層と、絶縁層と接し、且つ、ソース電極及びドレイン電極の間に設けられる第2のゲート電極と、を有し、キャリア密度の高い酸化物半導体層は、酸化物半導体層を介して対向し、且つ酸化物半導体層の端部の上面、下面、及び側面のそれぞれ一部、並びにゲート絶縁層の上面一部と接する半導体装置である。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶データとしてデータを記憶するメモリセルと、出力信号線と、電圧が与えられる配線と、を具備し、メモリセルは、記憶データと検索データの比較演算を行い、演算結果に応じて導通状態又は非導通状態になる比較回路と、記憶データの書き込み及び保持を制御する電界効果トランジスタと、を備え、比較回路が導通状態のときに、出力信号線の電圧値が配線の電圧と同等の値になる記憶装置。

(もっと読む)

半導体記憶装置

【課題】データ保持のためのリフレッシュ動作の頻度を低減し、消費電力の小さいDRAMを提供する。また、DRAMに占めるキャパシタの面積を縮小し、集積度の高い半導体記憶装置を提供する。

【解決手段】ビット線、ワード線、トランジスタおよびキャパシタからなる半導体記憶装置であり、トランジスタは、ソース電極およびドレイン電極と、少なくともソース電極およびドレイン電極の上面と接する酸化物半導体膜と、少なくとも酸化物半導体膜の上面と接するゲート絶縁膜とを有し、上面から見て網状の導電膜の網の目の部分に設けられる。ここで、キャパシタは、一対の電極の一方と、網状の導電膜と、一対の電極の一方および網状の導電膜の間に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

る。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて

、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及

び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層

する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガス

を用いた酸化シリコン膜で形成する。

(もっと読む)

EL表示装置および電子機器

【課題】画素部と同じ絶縁基板上において、大きな電流供給能力が得られるトランジスタで構成される電源線駆動回路を備えたEL表示装置を提供する。

【解決手段】絶縁基板上に複数の画素と複数の信号線、複数の走査線、及び複数の電源線を有するアクティブマトリクス型表示装置において、前記絶縁基板上に電界効果移動度が少なくとも80cm2/Vs以上、好ましくは120cm2/Vs以上を有する酸化物半導体のトランジスタを有し、トランジスタを1つの構成要素とする電源線駆動回路を有するEL表示装置である。

(もっと読む)

半導体装置

【課題】フォトセンサを有する半導体装置において、外光のノイズを軽減し、且つトランジスタのオフ電流によるリークが原因となるノイズも低減する。

【解決手段】マトリクス状に配置された複数のフォトセンサを有する。複数のフォトセンサはそれぞれ、光電変換素子と増幅回路とを有する。バックライトを点灯して被検出物に光を照射して第p行目のフォトセンサでリセット動作及び蓄積動作を行った後、バックライトを非点灯として第(p+1)行目のフォトセンサでリセット動作及び蓄積動作を行い、その後全行のフォトセンサの選択動作を順次行う。隣接する行のフォトセンサで得られた出力信号の差分を取得し、差分を用いて被検出物の撮像画像の生成や被検出物の存在する領域の検出を行う。増幅回路は蓄積された電荷を保持するトランジスタを有し、当該トランジスタはチャネルが酸化物半導体層に形成される。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】非接触にて、被写体の位置情報の取得を容易に行うことができる固体撮像装置、または半導体表示装置の提供。

【解決手段】第1入射方向から第1入射角を有する光が入射する複数の第1フォトセンサと、第1入射方向とは異なる第2入射方向から第2入射角を有する光が入射する複数の第2フォトセンサとを有し、複数の第1フォトセンサのうち、第1入射方向の上流側の一つの第1フォトセンサの方が、第1入射方向の下流側の他の一つの第1フォトセンサよりも、第1入射角が大きく、複数の第2フォトセンサのうち、第2入射方向の上流側の一つの第2フォトセンサの方が、第2入射方向の下流側の他の一つの第2フォトセンサよりも、第2入射角が大きい。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

表示基板の製造方法

【課題】過剰なエッチングによる不良を減少させるための表示基板の製造方法を提供する。

【解決手段】互いに交差する信号ラインによって定義された複数の単位画素Pを有する表示領域DAと表示領域DAを取り囲む周辺領域PAを含む基板110上にフォトレジスト膜を塗布する段階と、フォトレジスト膜をパターニングして、表示領域DAで信号ラインとオーバーラップされる第1パターン部P1と、周辺領域PAで信号ラインと重畳されない領域に形成された複数のダミー開口部DOを含む第2パターン部P2とを形成する段階と、第1パターン部P1及び第2パターン部P2が形成された基板110上に透明電極層117a、117bを形成する段階と、ストリップ溶液で第1パターン部P1、第2パターン部P2、及び第1及び第2パターン部上に形成された透明電極層117a、117bを除去して、単位画素Pに対応する画素電極PE及びダミー開口部DOに対応するダミー電極DMを形成する段階と、を含む。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程におい

て、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。酸素ドープ処

理されたゲート絶縁膜、熱処理による脱水化または脱水素化処理された酸化物半導体膜を

有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジ

スタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることが

できる。

(もっと読む)

表示装置

【課題】TFTの閾値電圧がシフトしても、駆動回路の高い信頼性を確保することができ

る表示装置を提供する。

【解決手段】出力回路が有するトランジスタのゲートに、順方向バイアスの電圧または逆

方向バイアスの電圧を与えることができる電源制御回路と、出力回路が有するトランジス

タの閾値電圧の変化量をモニターするためのモニター用トランジスタと、出力回路が有す

るトランジスタの閾値電圧を補正するべく、該トランジスタのゲートに逆方向バイアスの

電圧を与えるように電源制御回路を制御する閾値制御回路と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

201 - 220 / 2,978

[ Back to top ]