Fターム[5F110GG19]の内容

Fターム[5F110GG19]の下位に属するFターム

超格子 (27)

Fターム[5F110GG19]に分類される特許

1,241 - 1,246 / 1,246

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

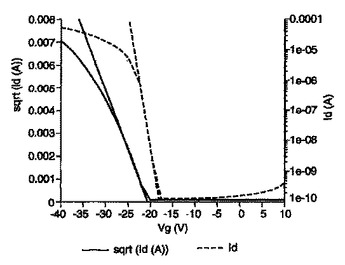

半導体デバイス及び有機薄膜トランジスタの製造方法

有機半導体として有用なビス(2−アセニル)アセチレン化合物が開示される。これらの化合物は、OTFTの活性層として使用されると、ペンタセンと同等の電荷キャリア移動度および電流オン/オフ比のようなデバイス特性を示す。また、少なくとも1種の本発明の化合物を含む半導体デバイス、ならびに薄膜トランジスタまたはトランジスタアレイおよびエレクトロルミネッセンスランプなどの半導体デバイスを含む物品についても記載される。  (もっと読む)

(もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

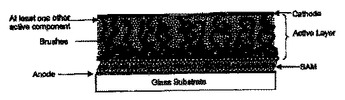

半導体ポリマーブラシを組み込んだ有機電子素子

少なくとも2つの電極と半導体層を含み、その半導体層は少なくとも一の正孔輸送半導体材料と少なくとも一の電子輸送半導体材料の混合物を含むものであって、少なくとも一の前記半導体材料が、少なくとも一の前記電極表面に付着していて且つ少なくとも一の前記の他の半導体性材料と接触している、半導体ポリマーブラシの形状を有する有機電子素子。また、少なくとも2つの電極と半導体層を含み、その半導体層は少なくとも一の正孔輸送半導体材料または少なくとも一の電子輸送半導体材料を含むものであって、前記少なくとも一の半導体材料が、少なくとも一の前記電極表面に付着している、半導体ポリマーブラシの形状を有する有機電子素子。前記素子の製造方法も提供されている。  (もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

1,241 - 1,246 / 1,246

[ Back to top ]