Fターム[5F110HJ02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物材料 (2,949) | キャリアにならない不純物 (131)

Fターム[5F110HJ02]に分類される特許

101 - 120 / 131

半導体装置の製造方法およびMOS電界効果トランジスタ

【課題】基板浮遊効果の抑制、およびオフリーク電流の低減化を、実用上充分なレベルで同時に達成すること

【解決手段】 絶縁体12b上の半導体層12cに設けられたp型の素子形成領域18にイオン注入された、n型の第1ドーパントを、アニールにより活性化することで形成されたソース領域20、ドレイン領域22、およびボディ領域24とを備える半導体装置を製造するにあたり、第1ドーパントのイオン注入に先立ち、(a)ボディ領域の形成予定領域内の領域であって、形成されるべきソースおよびドレイン領域との境界領域へのArのイオン注入と、(b)第1ドーパントの活性化のためのアニールよりも高温で、Arのイオン注入により生じた結晶の欠陥を部分的に回復させるための高温アニールとを行う。

(もっと読む)

サーマルバジェットを低減する接合およびケイ化物の形成

半導体基板(1)の上に金属ケイ化物層(12,13,14,18,19)を形成する方法であって、半導体基板(1)は少なくともドーパント領域(5)を含み;ドーパント領域(5)は極浅接合領域を含み;同方法は第1のステップとしてドーパント領域(5)を形成する少なくとも1つの不純物注入処理(IB dopant)を含み;同方法は第2のステップとしてドーパント領域(5)の上に金属ケイ化物層(12,13,18,19)を形成する少なくとも1つの金属注入処理(IB metal)を含み、さらに同方法は第1および第2のステップより後に実行される第3のステップとしてドーパント領域(5)を活性化し同時に金属ケイ化物層(12,13,14,18,19)を形成する低温アニール処理を含む。  (もっと読む)

(もっと読む)

混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタ

【課題】 混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタを提供すること。

【解決手段】 ハイブリッド配向基板は、n型電界効果トランジスタ(nFET)が電子移動度に最適な半導体の配向内に配置され、p型電界効果トランジスタ(pFET)が正孔移動度に最適な半導体の配向内に配置される、相補型金属酸化膜半導体(CMOS)回路の製造を可能にする。本発明は、最適な半導体の配向内に完全に形成されたFETの性能利点が、デバイスのチャネルを最適な配向をもつ半導体内に配置することを必要とするだけで実現できることを開示する。様々な新しいFET構造体が説明され、その全ては、FETのチャネルは、FETのソース及び/又はドレインとは異なる配向を有するという特徴を備えている。これらの新しいFETを組み込むことができるハイブリッド基板は、その製造方法と共に説明される。

(もっと読む)

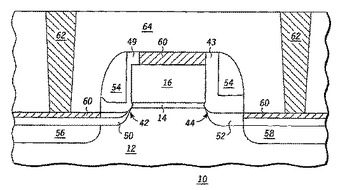

非対称性誘電領域を備える半導体装置の形成方法及びその半導体装置の構造

半導体基板(12)を形成するステップ、半導体基板の上方に第一側面及び第二側面を備えるゲート電極(16)を形成するステップ、及びゲート電極の下方にゲート誘電体を形成するステップを含む半導体装置(10)の形成方法。ゲート誘電体は、ゲート電極の下方でゲート電極の第一側面に隣接した第一領域(42)と、ゲート電極の下方でゲート電極の第二側面に隣接した第二領域(44)と、ゲート電極の下方で第一領域及び第二領域間にある第三領域(14)とを備えている。第一領域は、第二領域よりも薄く、第三領域は、第一領域よりも薄く、更に第二領域よりも薄い。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 SOI基板において、エクステンション部等の活性領域における寄生抵抗を減少させて急峻な不純物プロファイルを得る。

【解決手段】 ソース32aを形成する領域及びドレイン32bを形成する領域と、エクステンション部32c、32dを形成する領域とをアモルファス化した後に再結晶化し、不純物を、固溶限界を超えて熱拡散を抑制して活性化させる。このようにすると、不純物が固溶限界を超えて活性化するので、エクステンション部32c、32d等の活性領域における寄生抵抗が減少する。また、不純物の熱拡散を抑制して活性化するので、イオン注入直後の不純物プロファイルをほとんど維持できる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 浅いソース,ドレイン接合位置を保ちつつ接合リークを低く抑えることができ

、且つコンタクト抵抗も低く保つ。

【解決手段】

SOI−MOSFETにおいて、絶縁膜102の上に形成され、チャネル領域を除いて

除去された第1のシリコン層103と、シリコン層103上にゲート絶縁膜200を介し

て形成されたゲート電極300と、シリコン層103のチャネル長方向の両側の絶縁膜1

02に設けられた溝の底面及び側面に形成され、側面の一部でシリコン層103に接する

ように形成された第2のシリコン層600と、第2のシリコン層600からなるソース,

ドレイン領域601,602上に形成されたシリサイド層631,632と、シリコン層

103と接するシリコン層600の側面部に位置するシリサイド層631,632に形成

された、AsとOを1019cm−3以上の濃度で含む拡散抑制領域とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】 酸化濃縮法を用いて半導体層の一部におけるGe濃度を高める際に生じる不具合を解決することができ、素子製造の再現性及び歩留まりの向上をはかる。

【解決手段】 半導体装置の製造方法において、基板上に少なくともSiを含む半導体層3を形成した後、半導体層3に素子分離用絶縁膜4を形成し、半導体層3を第1の半導体層3aと第2の半導体層3bに分離し、次いで第2の半導体層3b及び素子分離用絶縁膜4の上にシリコン窒化膜7を形成し、次いで第1の半導体層3a及びシリコン窒化膜7の上にSiGe膜6を形成し、次いでSiGe膜6を酸化して酸化膜8を形成すると共に、該膜6中のGeを第1の半導体層3a中に拡散させ、次いでSiGe膜6の酸化物8を除去し、次いでシリコン窒化膜7を除去する。

(もっと読む)

MOS型半導体装置及びその製造方法

【課題】 CMOS構造の両方の極性の素子に対してコンタクト抵抗の低減を図り、Fin−MOSFET構造による移動度の増大を享受しつつ、製造コストの増大を回避する。

【解決手段】 MOS型半導体装置において、絶縁膜101上に薄壁状に形成された単結晶半導体層102と、半導体層102の両側壁面上にそれぞれゲート絶縁膜104を介して形成されたゲート電極105と、ゲート電極105に対応して半導体層102に形成されたソース・ドレイン領域と、半導体層102の一方の側壁面に形成され、ソース・ドレイン領域とショットキー接合を成す第1の金属−半導体化合物層112と、第1の金属−半導体化合物層112とは組成が異なり、半導体層102の他方の側壁面に形成され、ソース・ドレイン領域とショットキー接合を成す第2の金属−半導体化合物層122とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】 窒化ガリウム系化合物半導体層を用いた半導体装置において、半導体装置の動作時に、歪による結晶欠陥によってリーク電流が発生することを防止する。

【解決手段】 窒化ガリウム系化合物半導体層よりなるチャネル層12とゲート電極17との間にゲート絶縁膜13を備えた半導体装置であって、ゲート絶縁膜13は、砒素が添加された窒化ガリウムよりなる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果によるリーク電流の低減に優れた半導体装置およびその製造方法を提供する。

【解決手段】単結晶半導体基板上に形成された電界効果トランジスタの作成過程において、エクステンション領域を形成するために不純物を導入するとともに、単結晶格子を崩してアモルファス化させる。または、不純物および原子量の大きい元素を導入することによって、単結晶格子を崩してアモルファス化させる。そして、パルス幅が1fs以上10ps以下、かつ波長が370nm以上640nm以下のレーザビームを照射することにより、アモルファス化した部分のみを選択的に活性化させ、エクステンション領域を20nm以下の厚さで形成する。

(もっと読む)

半導体デバイスの製造方法およびこの方法で製造される半導体デバイス

本発明は半導体本体(2)を有する半導体デバイス(10)に関し、この半導体デバイスは、電界効果トランジスタを備え、第1ゲート誘電体(6A)をチャネル領域(5)の位置における第1表面上に形成してその上に第1ゲート電極(7)を形成し、半導体本体(2)の第1側面から、また第1ゲート電極(7)を通しておよびの両脇の側面にもぐり込みイオン注入(20)を行い、このイオン注入により、第1ゲート電極(7)の下方のシリコンの特性を、第1ゲート誘電体(6A)から離れたチャネル領域(5)の部分にあるゲート電極(7)の両脇のシリコンの特性と比較して変化させ、このシリコンの特性変化を利用しつつ、半導体本体(2)の第2表面に選択的エッチングによってキャビティ(30)を設ける。第2ゲート(6B、8)をこのように形成したキャビティ内に堆積させる。イオン注入(20)の前に、ゲート電極(7)の両脇にそこから距離を離してマスク(M1)を形成し、それによってマスク(M1)の位置でのイオン注入(20)の後、マスク(M1)の位置でもシリコンの特性変化を得る。このようにして、デバイス(10)には側方絶縁領域を設けることができる。さらに、ゲート電極(7,8)の端部領域を、このようにして絶縁領域によって包囲することができる。  (もっと読む)

(もっと読む)

深く炭素がドーピングされた領域並びに隆起したドナーがドーピングされたソース及びドレインを特徴とする歪みnMOSトランジスタ

本発明に係る複数の実施例は、炭素がドーピングされた領域、及び隆起したソース/ドレイン領域を有することで、nMOSトランジスタチャネル中に引っ張り応力を供する。

(もっと読む)

(もっと読む)

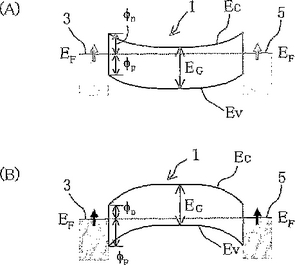

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

ゲート電圧VGSの印加によって、強磁性ソースにおける金属的スピンバンドによるショットキー障壁幅が減少し、この金属的スピンバンドからのアップスピン電子がチャネル領域にトンネル注入される。このとき強磁性ソース3aの半導体的スピンバンドによるエネルギー障壁により非磁性コンタクト3bからダウンスピン電子は注入されない。すなわち、強磁性ソース3aからはチャネル層へアップスピン電子のみが注入される。強磁性ソース3aと強磁性ドレイン5aとが平行磁化の場合では、アップスピン電子は強磁性ドレインの金属的スピンバンドを伝導してドレイン電流となるが、反平行磁化を持つ場合では、アップスピン電子は強磁性ドレイン5aにおける半導体的スピンバンドによる高さΔEcのエネルギー障壁よって強磁性ドレイン5aを伝導することができない。 上記動作原理のMISFETに基づき、高性能・高集積密度の不揮発性メモリを構成することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

nMOS構造の半導体装置において、不純物拡散層(21)を形成するに際して、エクステンション領域(13)及びポケット領域(11)の形成、更にエクステンション領域(13)の不純物拡散を抑制する目的に用いる最適な不純物の組み合わせを考察し、エクステンション領域(13)の不純物に少なくともリン(P)を、ポケット領域(11)の不純物に少なくともインジウム(In)を用い、更に拡散抑制物質として炭素(C)を用いる。これにより、特にnMOS構造の半導体装置において、閾値電圧のロールオフ特性及び電流駆動能力を向上させ、ドレインリーク電流の低減を図りつつも、素子の微細化・高集積化を容易且つ確実に実現し、特にCMOS構造の半導体装置の最適設計を可能としてデバイス性能の向上及び低消費電力化を実現する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 寄生抵抗が低く、良好な性質を有する半導体装置およびその製造方法を提供する。

【解決手段】 本発明にかかる半導体装置100の製造方法は、(a)絶縁層8上に設けられた半導体層10の上方にゲート絶縁層20を形成する工程と、(b)前記ゲート絶縁層20の上方にゲート電極22を形成する工程と、(c)前記半導体層10に不純物を導入することにより、ソース領域26およびドレイン領域14を形成する工程と、(d)前記半導体層10にフッ素を導入することにより第1のフッ素含有領域50、52を形成する工程と、(e)前記半導体層10の半導体と遷移金属を反応させることにより、低抵抗半導体金属合金層32、34を形成する工程と、を含む。

(もっと読む)

水素イオン注入剥離方法及び活性シリコン装置

【課題】装置の移動に中間媒体基板を用いる必要がなく、移動工程後にシリコン活性層の薄層化を行う必要がない水素イオン注入剥離方法及び活性シリコン装置を提供する。

【解決手段】本発明は、シリコン・オン・インシュレータ基板に形成された回路を、キャリア基板へ接合するための水素イオン注入剥離方法であって、シリコン基板上にシリコン活性層と埋込酸化層とを形成し、シリコン・オン・インシュレータ基板を準備する工程302と、シリコン活性層に回路を形成する回路形成工程304と、選択された回路領域上に、遮断マスクを形成するマスク形成工程306と、シリコン基板に水素イオン(H+またはH2+)を注入する注入工程308と、水素の注入に応じて、シリコン基板に劈開分離層を形成する劈開分離層形成工程312と、回路をキャリア基板に接合する接合工程314と、シリコン基板を劈開分離層に沿って劈開分離する劈開分離工程316とを含むものである。

(もっと読む)

歪みチャネル、及びヘテロ接合ソース/ドレインを有する半導体素子を形成する方法

半導体素子(10)は、ゲート(22)を、シリコンから成ることが好ましい半導体層(16)の上に配置することにより形成される。例えば、SiGeまたはGeのみから成る半導体材料(26)をゲートに隣接するように、かつ半導体層の上に、更にソース/ドレイン領域の上に形成する。熱処理プロセスを行なってストレッサ材料を半導体層に拡散させる。横方向の拡散が生じることにより歪みチャネル(17)が形成され、ストレッサ材料層(30)が歪みチャネルの直ぐ傍に隣接するようになる。エクステンションイオン注入を行なうことにより、ソース及びドレイン注入領域がストレッサ材料層の第1部分に形成される。ストレッサ材料層の第2部分は、歪みチャネルとソース及びドレイン注入領域との間のチャネルに残される。従って、ヘテロ接合が歪みチャネルに形成される。別の形態では、エクステンションイオン注入ではなく、ストレッサ材料の酸化を行なうことにより、歪みチャネルを形成する。  (もっと読む)

(もっと読む)

歪みチャネルを備える二重ゲートデバイス

半導体デバイス(10)は、好ましくはシリコンの半導体層(16)上にゲート(22)を配置して形成される。一例として、SiGe又はGeの半導体材料(26)は、半導体層上のゲートに隣接し、かつソース/ドレイン領域上に形成される。熱工程により、ストレス材料が半導体層の内部に拡散される。横方向への拡散により、歪みチャネル(17)が形成される。ストレス材料層(30)は、歪みチャネルに直接隣接している。エクステンション注入により、ストレス材料層の第一部分からソース/ドレイン注入が形成される。ストレス材料層の第二部分は、歪みチャネルとソース/ドレイン注入との間のチャネル内に残存する。従って、歪みチャネル内にヘテロ接合が形成される。別の実施形態において、エクステンション注入よりは、むしろストレス材料の酸化により、歪みチャネルが形成される。  (もっと読む)

(もっと読む)

シリサイド膜の形成方法

【課題】 シリサイド膜を薄くしても細線効果を抑えることが可能なシリサイド膜の形成方法を提供する。

【解決手段】 SOI基板全面に対してアルゴンイオンを注入した後,基板を約300℃に調整し,ロングスロー・スパッタリング法を用いてチタン膜21(膜厚15nm)を形成する。基板を大気に曝すことなく連続的にチタン窒化膜23(膜厚30nm)を形成する。窒素雰囲気中で1回目の熱処理(750℃)を行い,ゲート領域,ソース領域,およびドレイン領域にそれぞれ自己整合的にシリサイド膜31,32,33(膜厚30nm)を形成する。チタン窒化膜と未反応のチタン膜を除去した後,2回目の熱処理(850℃)を行う。高抵抗の結晶構造C49を有するシリサイド膜31,32,33は,低抵抗の結晶構造C54を有するシリサイド膜に相転移する。

(もっと読む)

半導体装置の製造方法及びそのような方法を用いて得られる半導体装置

本発明は、半導体材料からなる半導体本体(1)の表面に、第1の導電型のソース領域(2)及びドレイン領域(3)と、ソース領域(2)とドレイン領域(3)との間に第1の導電型とは反対の第2の導電型のチャネル領域(4)と、チャネル領域(4)上の第1のゲート誘電体(6)によって半導体本体の表面から分離された第1のゲート領域(5)と、第1のゲート領域(5)とは反対に位置し且つ半導体本体(1)の反対面内の凹所(20)内に第2のゲート誘電体(8)によってチャネル領域(4)から分離されるように形成された第2のゲート領域(7)とが設けられる、二重ゲート電界効果トランジスタを備える半導体装置(1)を製造する方法であって、チャネル領域(4)のドーピング(9)の局所変化を用いて且つ半導体本体(1)の反対面から開始するエッチング工程を実施することによって凹所(20)が形成される方法に関する。  (もっと読む)

(もっと読む)

101 - 120 / 131

[ Back to top ]