Fターム[5F110HJ02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物材料 (2,949) | キャリアにならない不純物 (131)

Fターム[5F110HJ02]に分類される特許

21 - 40 / 131

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】高性能でかつばらつきの少ないナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に第1絶縁膜を形成する工程と、第1絶縁膜上に設けられ、第1領域と第1領域よりも幅の広い第2および第3領域とを有しこれらの第2および第3領域の少なくとも一方が第1領域に接続するように構成された第1半導体層と、第1半導体層の上面に設けられるマスクと、を形成する工程と、マスクを用いて、前記第1半導体層の第1領域の側面にイオン注入を行う第1イオン注入を行う工程と、イオン注入を行った後に、第1熱処理を行う工程と、マスクを除去した後、第1半導体層の前記第1領域の少なくとも側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲート電極の、第2および第3領域側の側面に絶縁体のゲート側壁を形成する工程と、少なくとも第1半導体層の第2および第3領域に第2イオン注入を行う工程と、とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

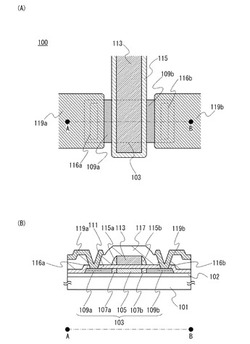

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

発光装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にp型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置の作製方法

【課題】金属元素を用いた結晶化法において、ゲッタリングのために必要な不純物元素の濃度が高く、その後のアニールによる再結晶化の妨げとなり問題となっている。

【解決手段】

本発明は半導体膜に、希ガス元素を添加した不純物領域を形成し、加熱処理およびレーザアニールにより前記不純物領域に半導体膜に含まれる金属元素を偏析させるゲッタリングを行なうことを特徴としている。そして、半導体膜が形成された基板(半導体膜基板)の上方または下方からレーザ光を照射してゲート電極を加熱し、その熱によってゲート電極の一部と重なる不純物領域を加熱する。このようにして、ゲート電極の一部と重なる不純物領域の結晶性の回復および不純物元素の活性化を行なうことを可能とする。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

HFET

【課題】耐圧が高いHFET(Heterojunction−FET)を提供する。

【解決手段】ヘテロ接合16aに生じる2次元電子ガスをチャネルとするHFET10であって、第1半導体領域16と、第1半導体領域16上で第1半導体領域16とヘテロ接合している第2半導体領域18と、第2半導体領域18上に形成されたソース電極20、ドレイン電極22及びゲート電極24と、第1半導体領域16と接しており、ソース電極20と導通しているp型の第3半導体領域14を有している。ゲート電極24とドレイン電極22の間の第2半導体領域18の上面のうちの、ゲート電極24に隣接する範囲の上面は、第1表面準位密度を有する第1領域40であり、第1領域40に隣接する範囲の上面は、第1表面準位密度より低い第2表面準位密度を有する第2領域42である。第3半導体領域14は、第2領域42の下側で第1半導体領域16に接している。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

21 - 40 / 131

[ Back to top ]