Fターム[5F110HK40]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751) | シリサイド化 (743)

Fターム[5F110HK40]に分類される特許

161 - 180 / 743

不揮発性のラッチ回路及び論理回路並びにそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力が第2の素子の入力に電気的に接続され、第2の素子の出力が第1の素子の入力に電気的に接続されるループ構造を有するラッチ部と、ラッチ部のデータを保持するデータ保持部とを有し、このラッチ部とデータ保持部とにより不揮発性のラッチ回路が構成される。データ保持部は、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用いている。またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有している。

(もっと読む)

半導体装置

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングトランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチングトランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半導体装置である。

(もっと読む)

NMOSエピ層の形成方法

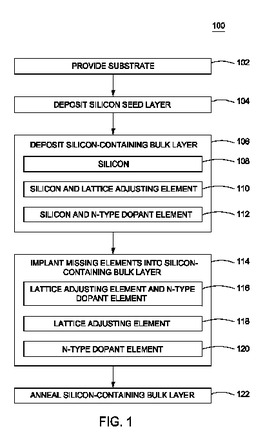

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

半導体装置、高周波集積回路、高周波無線通信システムおよび半導体装置の製造方法

【課題】SOS基板の異方性を低減して半導体装置のデバイス特性の面内均一性を向上する。

【解決手段】絶縁体基板101の主面上にSi層(またはSi基板)100を有する半導体装置10において、絶縁体基板101はサファイア基板101であり、絶縁体基板101の主面はc面である。サファイア基板101において異方性の少ないc面にSi層100を形成するので、Si層100上に形成された半導体装置10のデバイス特性の面内均一性を向上することができる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)と半導体基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。

【解決手段】溝部が設けられた半導体基板に、イオンを照射して半導体基板中に脆化領域を形成し、絶縁層を介して半導体基板とベース基板を貼り合わせると共に、半導体基板の溝部とベース基板とにより囲まれた空間を形成し、熱処理を施すことにより、脆化領域において半導体基板を分離して、ベース基板上に絶縁層を介して半導体層を形成する。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

不揮発性のラッチ回路及び論理回路並びにそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力が第2の素子の入力に電気的に接続され、第2の素子の出力が第1の素子の入力に電気的に接続されるループ構造を有するラッチ部と、ラッチ部のデータを保持するデータ保持部とを有し、このラッチ部とデータ保持部とにより不揮発性のラッチ回路が構成される。データ保持部は、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用いている。またこのトランジスタのソース電極又はドレイン電極に電気的に接続されたインバータを有している。上記トランジスタを用いて、ラッチ部に保持されているデータをインバータのゲート容量あるいは別に用意した容量に書き込むことができる。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置を低消費電力化又は長寿命化すること。

【解決手段】当該半導体装置は、電力供給源となる電池と、特定の回路とがチャネル形成領域が酸化物半導体によって構成されるトランジスタを介して電気的に接続することによって解決することができる。当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該半導体装置の待機時の消費電力を低減することができる。また、これにより当該半導体装置を長寿命化することができる。

(もっと読む)

半導体装置

【課題】良質な半導体装置を提供することを目的としている。

【解決手段】素子分離領域間の凸部108を含むシリコン基板106と、凸部108上の絶縁部112と、絶縁部112上のシリコンフィン114と、上面が凸部108の上面よりも低く位置する素子分離領域内の素子分離層116と、シリコンフィン114に設けられたソース/ドレイン領域と、ソース/ドレイン領域104のシリコンフィン114の側面から外側に突き出た横方向エピ成長シリコン部118と、ゲート電極領域102内のゲート絶縁層122を介してシリコンフィン114上に設けられるゲート電極124と、ゲート電極124の側面に隣接する第1のスペーサ128と、ソース/ドレイン領域104内の凸部108の側面を覆う第2のスペーサ130とを備える。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

自己整合されたデュアル応力層を用いるCMOS構造体及び方法

【課題】 デバイス性能を向上させ、チップの留まりを改善するために、CMOS構造体内に機械的応力を与える構造体及び方法を提供すること。

【解決手段】 第1のトランジスタの上に配置された第1の応力層及び第2のトランジスタの上に配置された第2の応力層が、当接するが、重ならない、CMOS構造体及びCMOS構造体を製造する方法が提供される。こうした重ならない当接により、第1のトランジスタ及び第2のトランジスタの一方の中のソース/ドレイン領域の上に、シリサイド層へのコンタクトを形成するとき、製造の柔軟性が向上する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

161 - 180 / 743

[ Back to top ]