Fターム[5F110HL07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | 透明導電膜(例;ITO) (1,570)

Fターム[5F110HL07]に分類される特許

201 - 220 / 1,570

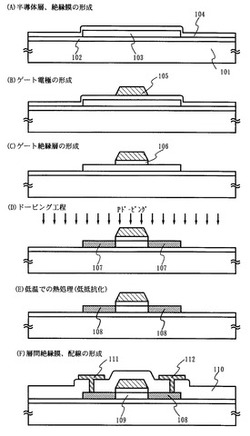

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置の作製方法

【課題】 光学系を複雑化させることなく、均一なエネルギー密度のレーザ光を被照射体

に照射することができる、レーザ照射装置の提案を課題とする。

【解決手段】本発明のレーザ照射装置は、レーザ発振器と、被照射体の表面における一軸方向に、前記レーザ発振器から発振されたレーザ光によって形成されるビームスポットを繰り返し走査するための光学系と、前記表面において前記一軸方向と交差する方向に向かって、前記レーザ光に対する前記被照射体の相対的な位置を移動させるための位置制御手段とを有することを特徴とする。

(もっと読む)

アレイ基板及び液晶表示装置

【課題】製造歩留まりの高いアレイ基板及び液晶表示装置を提供する。

【解決手段】アレイ基板は、複数の補助容量電極と、複数の半導体層15と、複数のゲート電極20を含んだ複数の走査線19と、複数の補助容量線と、複数のコンタクトホールを有した層間絶縁膜と、複数のコンタクトホールを通って複数の半導体層のソース領域に電気的に接続された複数の信号線と、複数の画素電極と、を備えている。走査線19が延在した方向に互いに隣合う一方の画素電極が接続された補助容量電極と、他方の画素電極が接続された補助容量電極とは、走査線を挟んで位置している。薄膜トランジスタのチャネル面積CSは、24μm2以上である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流が小さく、好ましくはオン電流及び移動度も高く、工程が簡略化された半導体装置の作製方法を提供する。

【解決手段】チャネルエッチ型の薄膜トランジスタの作製に際して、ゲート絶縁層上に少なくとも半導体層を形成し、半導体層上に導電膜を形成し、導電膜上にエッチングマスクを形成し、基板を反応室内に搬入し、導電膜を加工してソース電極及びドレイン電極層を形成し、反応室内に半導体エッチング用のガスを導入し、反応室内で半導体エッチング用のガスでエッチングを行い、基板を反応室から搬出し、その後エッチングマスクを除去する。すなわち、導電膜の加工から半導体エッチング用のガスで行うエッチングまでを同一チャンバー内で連続して行い、半導体エッチング用のガスで行うエッチングはエッチングマスクを除去する前に行う。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】高い移動度を実現でき、且つ、ストレス耐性(ストレス印加前後のしきい値電圧シフト量が少ないこと)にも優れた薄膜トランジスタ用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、Zn、Sn、およびInを含み、酸化物に含まれる金属元素の含有量(原子%)をそれぞれ、[Zn]、[Sn]、および[In]としたとき、下記式(1)〜(3)を満足するものである。

[In]/([In]+[Zn]+[Sn])≧−0.53×[Zn]/([Zn]+[Sn])+0.36 ・・・(1)

[In]/([In]+[Zn]+[Sn])≧2.28×[Zn]/([Zn]+[Sn])−2.01 ・・・(2)

[In]/([In]+[Zn]+[Sn])≦1.1×[Zn]/([Zn]+[Sn])−0.32 ・・・(3)

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製及び表示装置の作製に用いるフォトマスクの枚数を従来よりも少なくすることを課題の一とする。

【解決手段】ゲート電極を形成する工程と、島状半導体層を形成するための工程を、1回のフォトリソグラフィ工程で行い、平坦化絶縁層を形成した後、コンタクトホールを形成する工程を1回のフォトリソグラフィ工程で行い、ソース電極及びドレイン電極を形成する工程と画素電極を形成する工程を1回のフォトリソグラフィ工程で行い、合計3回のフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく

作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体層とする薄膜トランジスタ

を有する半導体装置の作製方法において、酸化物半導体層に接する酸化物絶縁膜を形成す

る。酸化物半導体層を減圧されたチャンバー内に導入後、窒素雰囲気下で加熱処理工程、

プラズマ(少なくとも酸素プラズマを含む)の導入工程を行い、成膜ガスを導入して酸化

物絶縁膜を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】オフ電流の極めて小さい半導体装置を提供する。また、該半導体装置を適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上にゲート電極を有し、ゲート電極上にゲート絶縁層を有し、ゲート絶縁層上に酸化物半導体層を有し、酸化物半導体層上にソース電極及びドレイン電極を有し、酸化物半導体層の外縁のうちソース電極の外縁からドレイン電極の外縁に達する部分の長さを、チャネル長の3倍以上、好ましくは5倍以上とする。また、熱処理により、ゲート絶縁層から酸化物半導体層へ酸素を供給する。また、酸化物半導体層を選択的にエッチングした後、絶縁層を成膜する。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】Gaを含まないIn−Zn−Oの酸化物半導体を備えた薄膜トランジスタのスイッチング特性およびストレス耐性が良好であり、特に正バイアスストレス印加前後のしきい値電圧変化量が小さく安定性に優れた薄膜トランジスタ半導体層用酸化物を提供する。

【解決手段】Inと;Znと;Al、Si、Ta、Ti、La、Mg、およびNbよりなる群から選択される少なくとも一種の元素(X群元素)と、を含む薄膜トランジスタの半導体層用酸化物である。

(もっと読む)

発光装置およびモジュール

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

201 - 220 / 1,570

[ Back to top ]