Fターム[5F110HL07]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | 透明導電膜(例;ITO) (1,570)

Fターム[5F110HL07]に分類される特許

1,561 - 1,570 / 1,570

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

ソース及びドレインの追加絶縁層を備えた共平面型薄膜トランジスタ

共平面型薄膜トランジスタ、TFT(22)及びその製造方法において、追加の絶縁層がソースコンタクト(30)及びドレインコンタクト(32)上に設けられ、当該追加の絶縁層の第1領域(34)がソースコンタクト(30)と実質的に同一領域を占有し、当該追加の絶縁層の第2領域(36)がドレインコンタクト(32)と実質的に同一領域を占有するように形が定められる。これにより、ゲート(62)−ソース容量、及びゲート(62)−ドレイン容量が低減される。一部の構成では、このことが追加のマスク又は形を定める工程なくして実現され得る。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

欠陥解析を実行するための方法及びそのシステム

回路欠陥解析及びプロセス問題識別を実行するための方法は、テスト信号を回路に印加するステップと、テスト信号に応答して生成された応答信号を得るステップと、応答信号を参照情報と比較するステップと、比較するステップの結果に基づいて回路内の欠陥を分類するステップと、欠陥分類に基づいて、欠陥を引き起こした製造プロセスにおける問題を識別するステップとを有している。参照情報は、製造プロセス中に発生する可能性がある予め定義されたタイプの欠陥に対応する1つ又は複数の信号プロフィルを含むことができる。欠陥の分類は、応答信号が、信号プロフィルのうちの1つ又は複数内に入るかどうか判定することによって実行されることが好ましい。応答信号が2つ以上の信号プロフィル内に入る場合には、各プロフィルについて確率を決定することができる。次いで、欠陥は、その信号プロフィルがより高い確率を有する欠陥タイプに対応するものとして分類することができる。処理システムは、同様の方法を使用して、欠陥の分類及びプロセス問題識別を実行する。 (もっと読む)

薄膜トランジスタを備えた平板表示装置

【課題】 薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】 各駆動薄膜トランジスタの活性層の結晶粒の差によって、そして、駆動薄膜トランジスタの活性層のサイズを変更せずホワイトバランスを合せ、各副画素に最適の電流を供給することによって適正な輝度を得、寿命を短縮させないようにするためのものであって、自己発光素子を備えた複数の副画素を含む画素と、前記各副画素に備えられて少なくともチャンネル領域を有する半導体活性層を備え、前記自己発光素子に各々接続されて電流を供給するものであって、前記活性層の少なくともチャンネル領域が前記副画素別にその結晶粒のサイズまたは形状が相異なるように備えられた駆動薄膜トランジスタと、を含むことを特徴とする平板表示装置。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

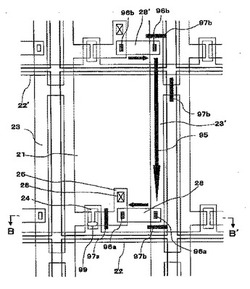

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

配線構造とこれを利用する薄膜トランジスタ基板及びその製造方法

【課題】 銀を利用する低抵抗配線構造を提供する。

【解決手段】

絶縁基板上に、ゲート配線が形成され、ゲート絶縁膜がゲート配線を覆っており、ゲート絶縁膜上に半導体パターン半導体が形成されている。半導体パターン半導体及びゲート絶縁膜の上には、ソース電極及びドレーン電極とデータ線を含むデータ配線が形成されており、データ配線上には、保護膜が形成されている。保護膜上には、接触孔を通じてドレーン電極と連結されている画素電極が形成されている。この時、ゲート配線及びデータ配線は、接着層、Ag層、及び保護層の3重層からなっており、接着層はクロムやクロム合金、チタニウムやチタニウム合金、モリブデンやモリブデン合金、タリウムやタリウム合金のうちのいずれか一つからなり、Ag層は銀や銀合金からなり、保護層はIZO、モリブデンやモリブデン合金、クロムやクロム合金のうちのいずれか一つからなっている。

(もっと読む)

1,561 - 1,570 / 1,570

[ Back to top ]